捷捷微电的此项发明提供的快速软恢复二极管芯片的制造方法,成本低,工艺简单可靠,也更易于形成局域少子寿命控制区。

集微网消息,捷捷微电自1995年创办以来,历经了25年的发展,渐渐成长为国内专门从事功率半导体器件的龙头企业。近年来,捷捷微电的营业收入和净利润保持持续增长,领先同业其他公司。同时,捷捷微电的产品正在逐步实现以国产替代进口,降低中国晶闸管、二极管等器件市场对进口的依赖。

现代电力电子技术广泛使用IGBT、功率MOSFET等开关器件,对与之配套使用的快恢复二极管提出了更高的要求,不仅要求其反向阻断电压高、正向瞬态压降小、反向恢复时间短,还要求其具有软恢复特性,对具备这种特性的快恢复二极管称为快速软恢复二极管(Fast Soft Recovery Diode,简称FSRD)。

目前的制造工艺中,更多的是采用局部寿命控制与发射极注入效率相结合的方法,在载流子寿命控制方面,虽然人们也做出了大量的研究工作,但无外乎采用重金属掺杂、电子、质子辐照中的一种或几种组合的方法。这些方法需要很高能量的离子注入机设备或者高能粒子加速器设备,由于设备的造价太高,造成产品成本极大的提升,生产的工艺难度也极大。

为了解决上述问题,捷捷微电申请了一项名为“一种快速软恢复二极管芯片的制造方法”(申请号:201711095076.7)的发明专利,申请人为江苏捷捷微电子股份有限公司。

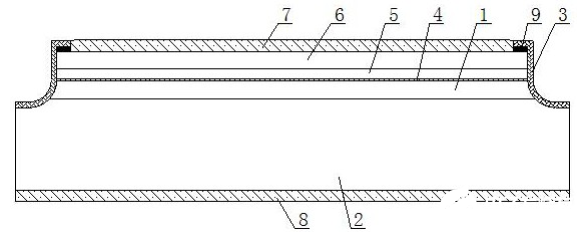

图1 FSRD芯片的结构示意图

上图是该专利提出的快速软恢复二极管芯片的结构示意图。为了制造此FSRD芯片,需要执行以下几个步骤:

首先,我们选用电阻率在15~150Ω·cm 之间的N-型硅单晶片1作为原材料,通过三氯氧磷扩散源,对其正面和背面实施高浓度磷予沉积扩散。经过2.5~10h的高温处理后,可以得到N+予沉积层。继续在高温中进行高达100~240h的推结扩散,这样就会形成深度为100~220μm的N+型衬底层2。

然后我们采用机械磨削方式,去除正面的N+型衬底层2,同时通过磨削量控制N-型硅单晶片1的厚度为50~130μm。接着再对N-型硅单晶片1的正面实施化学机械抛光,并通过抛光量来控制N-型硅单晶片1的剩余厚度为20~100μm,这样就能得到抛光基片。

在抛光基片的抛光面上外延生长N-型外延层5,其厚度为15~40μm。这里需要注意的一点是,在N-型外延层5初始生长0 .5~3μm的厚度时,其掺杂浓度为N-型硅单晶片1杂质浓度的2~5倍,形成一个掺杂高峰,以达到较好的损伤效果,然后降低掺杂浓度至N-型硅单晶片1杂质浓度的0 .8~1 .25倍继续外延生长到规定厚度,得到由N-型外延层5、N-型硅单晶片1和N+型衬底层2构成的双基区硅片,并在N-型外延层5初始生长部分与N-型硅单晶片1之间形成的损伤层作为局域少子寿命控制区4。

接下来,在双基区硅片的正面扩散形成P型发射区6, 并在P型发射区6的正面溅射0 .2~0 .5μm厚的铂或金,经过一小时的退火处理后,会形成合金层。然后进行重金属扩散,使铂或金沉积在局域少子寿命控制区4内,并用腐蚀法除去多余的铂或金。

然后在生成的氧化硅膜9中,用光刻法蚀刻出沟槽。再采用混酸对沟槽进行腐蚀,形成台面,之后经过烧结钝化,得到钝化膜3。通过光刻可以得到蒸镀铝所需的窗口,再对其进行反刻以生成阳极金属膜7。同时,在N+型衬底层2的背面蒸镀Ti-Ni-Ag,形成阴极金属膜8。最后再经过真空合金,即可得到图1所示的FSRD芯片结构。

捷捷微电此项发明提供了一种快速软恢复二极管芯片的制造方法,该制造方法成本低,工艺简单可靠,也更易于形成局域少子寿命控制区。此外,捷捷微电的产品已出口至韩国、日本、西班牙等国家和地区,公司的中高端产品实现替代进口及对外出口上升的趋势,打破了中国电子元器件领域受遏于国外技术制约局面。

-

芯片

+关注

关注

455文章

50812浏览量

423595 -

二极管

+关注

关注

147文章

9638浏览量

166482

发布评论请先 登录

相关推荐

揭秘捷捷微电可快速软恢复二极管芯片的专利

揭秘捷捷微电可快速软恢复二极管芯片的专利

评论