(文章来源:亚德诺半导体)

对于需要高动态范围的应用,通常使用Σ-Δ转换器。这些应用主要可以在化学分析、医疗保健和体重管理领域找到。但是,其中许多模块无法快速转换。图1中的电路描述了一种将高动态范围与高转换率相结合的方法。

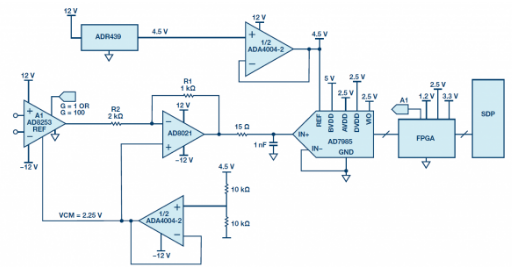

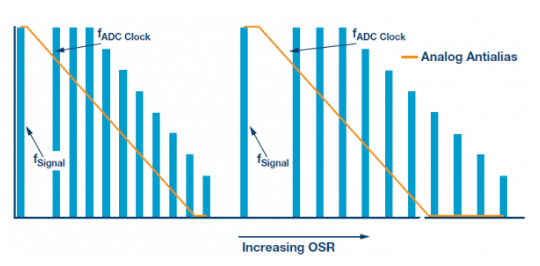

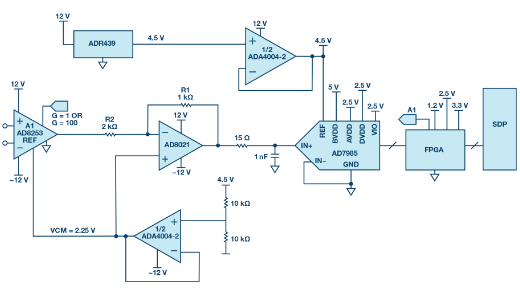

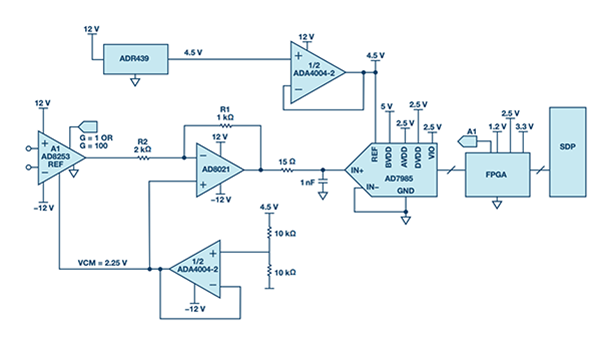

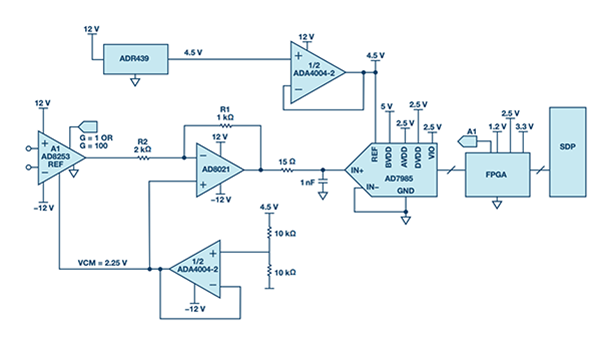

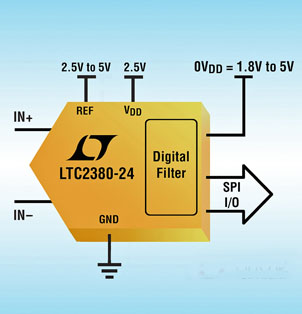

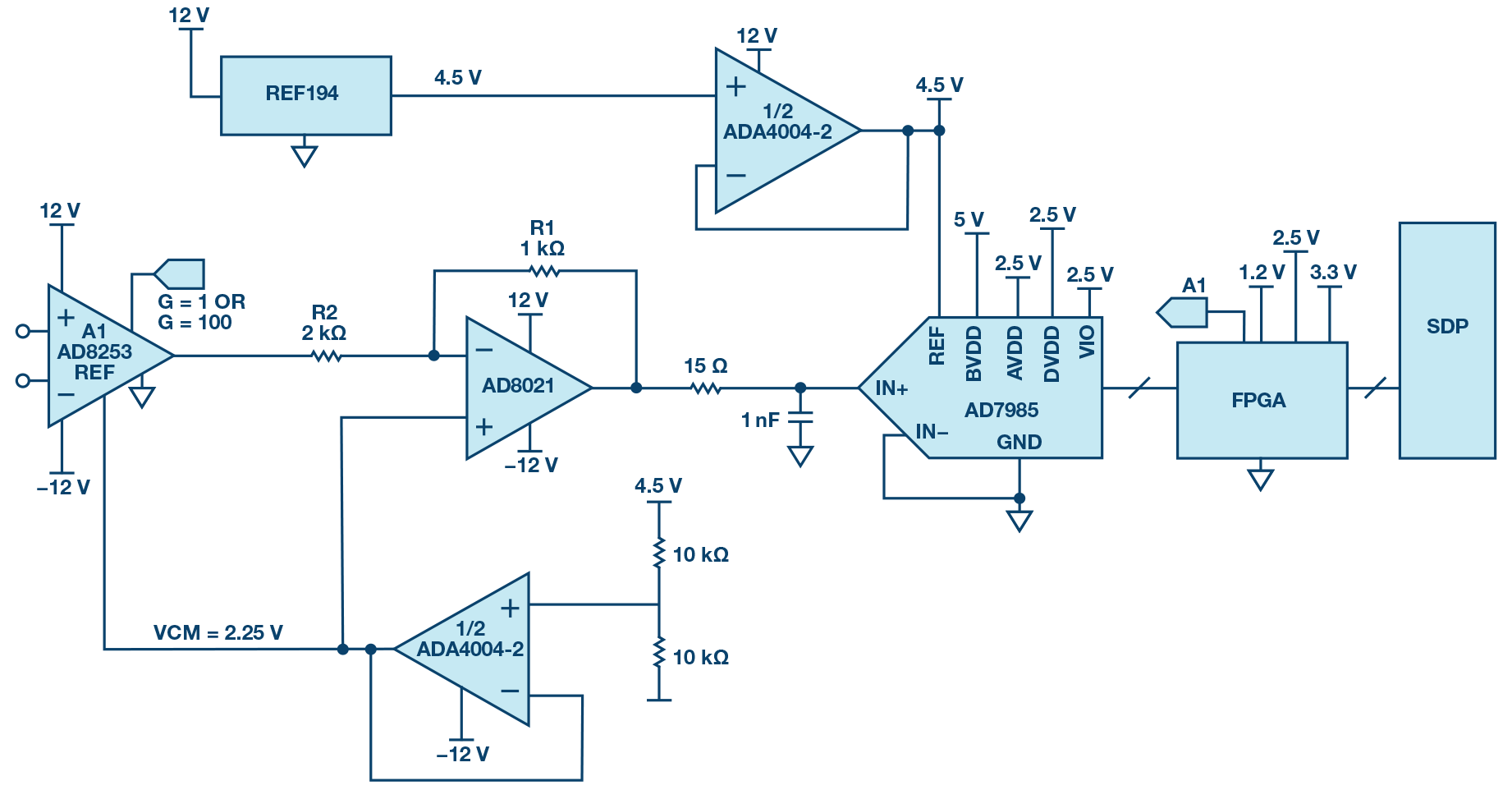

图1中的电路显示了带有2.5 MSPS和上游可编程仪表放大器的16位SAR转换器,它将增益设置为1或100。通过在FPGA中进行过采样和数字信号处理,该电路可实现大于125 dB的动态范围,并且仍然非常安静。高动态范围是通过AD8253的自动切换和过采样实现的,其中信号的采样速率远高于奈奎斯特频率。根据经验,采样频率加倍可在原始信号带宽下将信噪比(SNR)提高约3 dB。在图1所示的电路中,仍然在FPGA中应用数字滤波,以消除高于目标信号带宽的噪声。

图1.具有自动增益调节功能的SAR转换器。为了获得最大动态范围,在输入端使用仪表放大器将极低信号放大100倍。有关噪声的一些注意事项如下:

对于>126 dB的动态范围要求,在3 V (6 V p-p)输入信号时产生的最大噪声级为1 ?V rms。AD7985是具有2.5 MSPS的16位SAR转换器。如果它以600 kSPS(低功率损耗为11 mW)和72过采样系数运行,则产生大约8 kSPS的采样率,因此带宽为4 kHz。在这些条件下,将产生最大15.8 nV/√Hz的噪声密度(ND)。该值对于选择正确的仪表放大器很重要。ADC通常具有89 dB的SNR,而系数为72的过采样会额外增加18 dB,因此仍需要大约20 dB才能达到126 dB的目标,这是仪表放大器的任务。AD8253的增益为100时,其值为11 nV/√Hz。下方用作ADC驱动器和用于电平调节的AD8021又增加了2.1 nV/√Hz的噪声。

图2.过采样的增加消除了部分噪声。模拟信号链由基准电压ADR439(或REF194)以及ADA4004-2完成,作为基准缓冲区和驱动器,用于产生偏移电压。

除模拟路径中的组件外,FPGA(或处理器)对电路性能也很重要。关键任务是将仪表放大器的增益从1切换为100。为此,对许多阈值进行了编程以确保ADC不饱和。因此,AD8253在输入电压高达20 mV左右时以100为增益运行,这使得ADC输入端的最大电压达2.0 V。然后,FPGA将AD8253的增益降至1且没有延迟,以防止过载(见图3)。

图3.增益开关示例。

电路的变化可通过AD7980(16位、1 MSPS)、AD7982(18位、1 MSPS)或AD7986(18位、2 MSPS)等其他ADC操作。同样,不使用增益为1、10、100和1000的AD8253,而改用具有较低范围的AD8251等仪表放大器(增益为1、2、4和8)。基准电压的选择也可能会改变。

(责任编辑:fqj)

-

SAR

+关注

关注

3文章

418浏览量

45995 -

pga

+关注

关注

1文章

98浏览量

41536

发布评论请先 登录

相关推荐

16位SAR转换器应用可以在600 kSPS时达到125 dB的动态范围吗?

PGA-SAR系统无法达到12比特级别的可重复性时,Δ-Σ系统会怎么样呢?

8位SAR模数转换器MAX1391资料分享

如何采用SAR转换器实现125dB的动态范围

16位SAR转换器应用能否在600 kSPS时达到125 dB的动态范围

采用PGA的SAR转换器可实现125 dB的动态范围

CN0260 采用PGA的过采样SAR ADC,可实现125 dB以上的动态范围

24位SAR A/D转换器具实现145dB动态范围

带PGA的SAR转换器可实现125dB的动态范围

采用PGA的SAR转换器可实现的动态范围值为多少

采用PGA的SAR转换器可实现的动态范围值为多少

评论