楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日发布已经过数百次先进工艺节点成功流片验证的新版 Cadence 数字全流程,进一步优化功耗,性能和面积,广泛应用于汽车,移动,网络,高性能计算和人工智能(AI)等各个领域。流程采用了支持机器学习(ML)功能的统一布局布线和物理优化引擎等多项业界首创技术,吞吐量最高提升 3 倍,PPA 最高提升 20%,助力实现卓越设计。

经过多项关键技术,全新 Cadence 数字全流程实现了 PPA 和吞吐量的进一步提升:

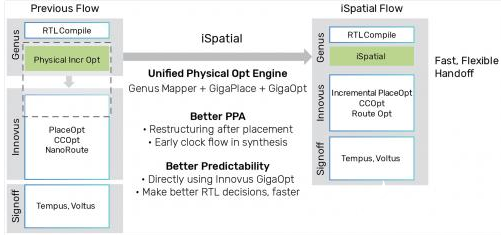

Cadence 数字全流程 iSpatial 技术:iSpatial 技术将 Innovus™ 设计实现系统的 GigaPlace™ 布线引擎和 GigaOpt™ 优化器集成到 Genus™ 综合解决方案,支持布线层分配,有效时钟偏移和通孔支柱等特性。iSpatial 技术让用户可以使用统一的用户界面和数据库完成从 Genus 物理综合到 Innovus 设计实现的无缝衔接。

机器学习(ML)功能:ML 功能可以让用户用现有设计训练 iSpatial 优化技术,实现传统布局布线流程设计裕度的最小化。

优化签核收敛:数字全流程采用统一的设计实现,时序签核及电压降签核引擎,通过所有物理,时序和可靠性目标设计的同时收敛来增强签核性能,帮助客户降低设计裕度,减少迭代。

“基于已经广泛采纳的集成流程,全新的增强版数字全流程进一步强化了 Cadence 在数字与签核设计领域的领导力,助力客户实现 SoC 卓越设计,”Cadence 公司资深副总裁兼数字与签核事业部总经理 Chin-Chi Teng 博士表示。“我们与客户紧密合作,缓解大规模设计下日益紧张的时间压力,提供高效达成 PPA 目标的全部所需。”

Cadence 数字全流程包括 Innovus 设计实现系统,Genus 综合解决方案,Tempus 时序签核解决方案和 Voltus IC 电源完整性解决方案。流程为客户提供实现设计收敛的快速路径和更好的可预测性,支持公司的智能系统设计™ 战略,助力实现高级节点片上系统(SoC)的卓越设计。

-

人工智能

+关注

关注

1797文章

47867浏览量

240845 -

ML

+关注

关注

0文章

149浏览量

34745 -

机器学习

+关注

关注

66文章

8453浏览量

133166

发布评论请先 登录

相关推荐

数据吞吐量提升!面向下一代音频设备,蓝牙HDT、星闪、Wi-Fi、UWB同台竞技

ADC芯片的采样率为100MSPS,位宽16位,那么吞吐量是多少?

TMS320C6472/TMS320TCI6486的吞吐量应用程序报告

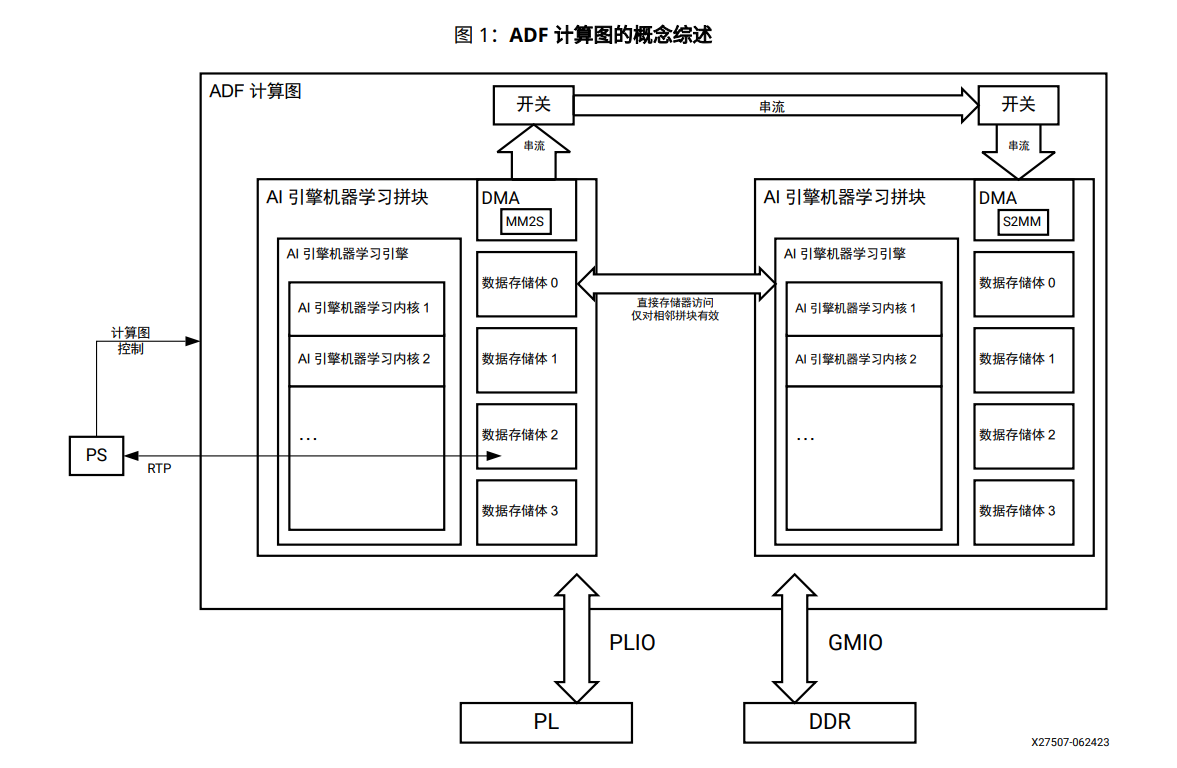

AI引擎机器学习阵列指南

求助,关于使用iperf测量mesh节点吞吐量问题求解

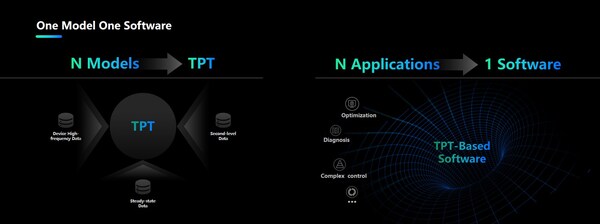

中控流程工业首款AI时序大模型TPT发布

首款基于机器学习引擎的新版数字全流程吞吐量最高提升了3倍

首款基于机器学习引擎的新版数字全流程吞吐量最高提升了3倍

评论