(文章来源:驱动之家)

根据外媒AdoredTV提供的消息,AMD代号为米兰的下一代Zen 3构架将会做一些核心级别的改进,目标是让Zen 3构架的IPC性能相比目前的Zen 2再度提升10~15%。

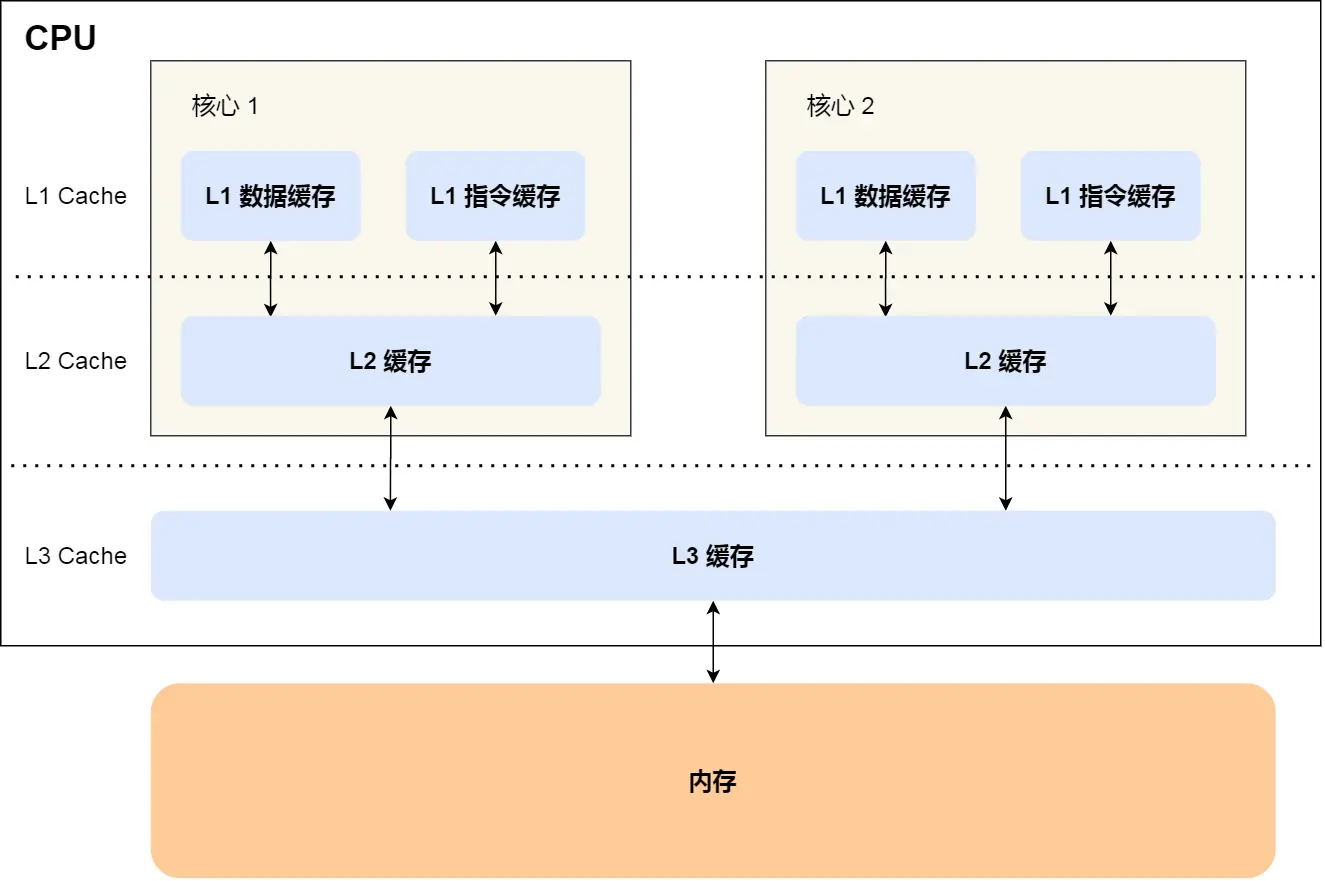

Zen3构架仍将采用CPU Die与I/O Die分离的Chiplets设计方案,但是最大的不同就是单个CCX将会拥有8个核心,而现在的锐龙处理器单个CCX是4个核心,2个CCX组成一个CCD。或许很多同学不能理解这样的变化能带来哪些改进!

此前单个CCD虽然是8个核心32M L3缓存,但是分成了2个CCX,单个CCX是4个核心16MB缓存,不同的CCX之间L3缓存是不能共用的,也就是说每个核心最多只能调用16MB L3缓存。如果一个应用程序只能支持4个或者更少核心的话,那么另外一个CCX的16MB L3缓存可能就会被闲置了。

Zen 3构架将单个CCX扩大到了8核,内置32MB L3缓存,也就是说不论在任何情况下,任何一个核心都可以调用全部的32M L3缓存,新的Zen3构架不再会浪费任何L3缓存。因此在一些对单核性能要求较高的应用中,这种设计方案将会极大增强处理器的运算效率。

Zen2构架IPC提升18%的秘诀之一就是L3缓存容量翻倍,Zen 3构架则是将每个核心能够利用的缓存容量再次翻倍。还有一点就是Zen 3的L3缓存设计并不需要增加额外的晶体管,即便是在制程工艺不变的情况下,也能带来额外的IPC性能提升。

PS:小编现在对于Zen 3构架的改进也是非常开心,此前的Zen1/2的设计方案并不能完全利用L3缓存,这一缺憾在Zen 3时代将不复存在!另外,下下代的Zen 4构架也有一些消息!

Zen 4构架的锐龙5000系列处理器将会使用全新的CPU针脚设计,也就是说现有的主板铁定是不能兼容了(Zen 3构架的锐龙4000系列处理器仍有可能采用AM4插座)。在制程工艺方面将会是5nm,在指令集方面将会扩展到完整的AVX 512。

另外Zen 4构架会将L2缓存容量翻倍,也就是单个核心将会配备1MB L2缓存。

(责任编辑:fqj)

-

amd

+关注

关注

25文章

5720浏览量

140602 -

Zen处理器

+关注

关注

1文章

29浏览量

8982

发布评论请先 登录

三级浪涌保护器的部署位置与行业应用方案

从设计约束到瞬态响应:航空三级式直流发电系统电抗-气隙-阻尼全参数链优化及工程应用

高性能(三级)电源滤波器

XC7Z020-2CLG484I 双核异构架构 全能型 SoC

CHA6154-99F三级单片氮化镓(GaN)中功率放大器

风华贴片电容的容量误差怎么看?

数据全复用高性能池化层设计思路分享

壹连科技成功通过CMMM三级认证

博泰厦门基地通过智能制造能力成熟度三级评估

Keithley 6514静电计在单电芯微法级容量衰减监测中的应用

高性能缓存设计:如何解决缓存伪共享问题

Zen 3构架迎来大改,三级缓存容量翻倍性能提升

Zen 3构架迎来大改,三级缓存容量翻倍性能提升

评论