深圳基本半导体的该项专利技术可以使得器件芯片区的面积利用率更高,获得更大的面积因子,从而提高器件的正向电流密度,并且没有对器件中其他电学特性造成影响。

集微网消息,近日“芯力量·云路演”第八期正式开始,其中参与路演的基本半导体的碳化硅二极管性能已经达到了国际一流水平,迎来了参会人员的一致好评,并且在投资机构的选票环节稳居第一,那么今天就带大家来看一下基本半导体的碳化硅二极管有什么过人之处吧。

碳化硅结势垒肖特基二极管(或称为“ SiC JBS器件”)具有芯片区和终端区。其中,芯片区的P型离子注入掺杂区(可简称“ Pgrid”)是阻止电流通过的区域,在器件反向关断时,Pgrid会因为PN结加反向电压的原因而扩宽PN结耗尽区宽度,从而关断电流,实现器件反向电流截止特性;芯片区的其它区域为电流导通区域。

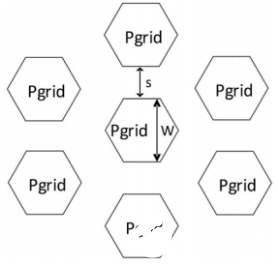

当前SiC JBS的主流器件中,Pgrid的结构大多设计成如图1(左)所示的正六边形和如图1(右)所示的长条形状,然而这两种主流的设计在面积的利用上仍有欠缺,面积因子有待提高。

图1 传统SiC JBS器件的Pgrid结构示意图

为了解决上述问题,基本半导体申请了一项名为“一种碳化硅结势垒肖特基二极管”的发明专利(申请号:201810622789.2),申请人为深圳基本半导体有限公司。

该专利提出了一种通过改善P型离子注入掺杂区结构设计,来提高面积因子的碳化硅结势垒肖特基二极管,以克服现有的结构设计面积利用率不高的问题。

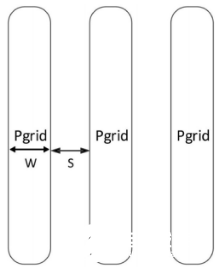

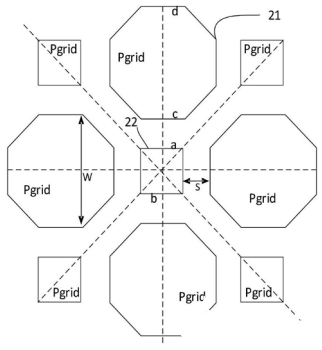

图2 改良后SIC JBS器件的Pgrid结构示意图

本专利改良后的SIC JBS器件的Pgrid结构示意图如上所示,P型离子注入掺杂区的形状主要有正方形和正八边形两种,并且正八边形P型离子注入掺杂区21和正方形P型离子注入掺杂区22等间距交替排列形成对称图案,该图案还同时满足中心对称和轴对称(对称轴如图2中虚线所示)。

在图2中所标示的正方形22和正八边形21,是两个相邻的Pgrid,正方形的两条平行边a、b与正八边形的其中两条平行边c、d相互平行。正八边形P型离子注入掺杂区21和正方形P型离子注入掺杂区22之间的间距S是指的相邻正方形和正八边形之间距离最近的两条平行边之间的距离,例如边a和边c之间的距离。

而且还可以根据产品性能要求(例如正向导通电流和反向击穿电压的需求)设计合适的间距S。间距S越大则正向电流越大,但反向击穿电压会降低,设计时需要综合兼顾这两个因素。

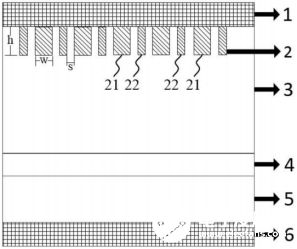

图3 Pgrid结构的SIC JBS器件芯片区剖面图

图3为具有图2中 Pgrid结构的SIC JBS器件芯片区剖面示意图,各P型离子注入掺杂区2具有相同的纵向厚度h。上图中的芯片区从上至下依次为Ni/Ti/Al金属层1、P型离子注入掺杂区2、SIC n-漂移层3、SIC n+缓冲层4、4H-SIC衬底5以及Ni/Ti/Ag金属层6。

与传统的六边形Pgrid和长条形Pgrid的结构设计相比,在宽度W和间距S相同的情况下,本发明的正八边形结合正方形排列组合的Pgrid结构设计,可以使得器件芯片区的面积利用率更高,获得更大的面积因子,从而提高器件的正向电流密度,并且没有对器件中其他电学特性造成影响。

基本半导体是中国第三代半导体行业领军企业,致力于碳化硅功率器件的研发与产业化。通过引进海归人才和外籍专家,基本半导体建立了一支国际一流的高层次创新团队,并且以创新驱动产业升级,基本半导体矢志推动中国在第三代半导体领域实现弯道超车。

-

半导体

+关注

关注

334文章

27251浏览量

217917 -

碳化硅

+关注

关注

25文章

2743浏览量

49002

发布评论请先 登录

相关推荐

肖特基二极管工作原理 肖特基二极管与普通二极管的区别

肖特基二极管与其他二极管的区别

肖特基势垒二极管的特征有什么

深圳基本半导体碳化硅结势垒肖特基二极管专利

深圳基本半导体碳化硅结势垒肖特基二极管专利

评论