最新消息称微软正开始在Win10上开发基于USB4.0的驱动程序,大量厂商已经开发基于USB4.0的设备,或许不用多久,我们就可以使用上基于USB4.0接口的设备,从而大大的提高传输速度。那么USB4.0是什么?USB4.0的前世今生到底是怎么回事,他和USB3.0、2.0都是什么关系?且听我慢慢道来。

USB4.0统一接口

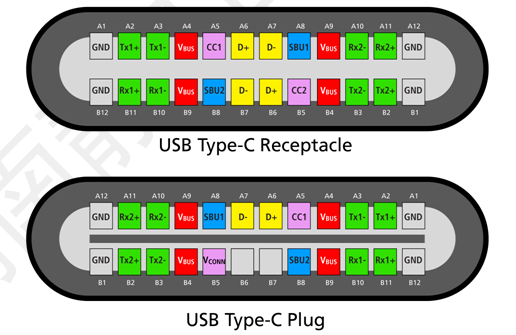

目前市场是我们能听到的或者见到的USB接口有多少种呢?USB2.0、USB3.0、USB3.1、USB3.1 Gen1、USB3.2 Gen2,包括即将发布的USB4.0,除了这些协议规范之外,还有Type-A、Type-C、USB公头母头等等各种不同的概念,但是也许以后这样的日子会一去不复返因为在USB 4.0以后也许就只有一种接口了。

USB历史回顾

回望USB从二十年前的1.0起,截至今天广泛为人所接受的3.0,USB标准总共经历了四个版本的迭代:

1995年,第一代USB接口USB1.0发布,最大特点是支持热插拔(带电插拔)和即插即用(Plug and Play)。USB1.0 低速(Low Speed) 传输速率为 1.5Mbps。

2000年,USB2.0在1.0基础上,速度升级到480mbps,速度是USB1.0的40倍,被称为USB 2.0的高速(High-speed)版本。

2014年,USB3.0面世,速度5.0Gbps(500MB/s),这个速度将较之现在的5Gbps快一倍之多。

由于USB 3.0增加了更多并行模式的物理总线,并利用了双向数据传输模式,而USB 2.0时代是半双工模式。简单来说,数据只需要朝一个方向流动就可以了,简化了等待引起的时间消耗。

随着要传输的数据越来越大,USB规格仍在进化。在更新一代的电脑里,USB3.1的速度被提升到了10Gbps,而达到这种传输速度的USB接口,被称之为USB3.1 Gen2。

USB4.0以USB3.2/2.0架构为基础打造,重新定义多终端设备共享和单路高速链路连接方案,具备自动扩展数据分配能力,多种数据传输时互不影响,并可最大限度高效利用带宽,双通道环境下最高可达40Gbps。USB 4.0速度是USB 3.0的8倍。

光从字来理解也不够生动,那我们来看图说话标识一下。

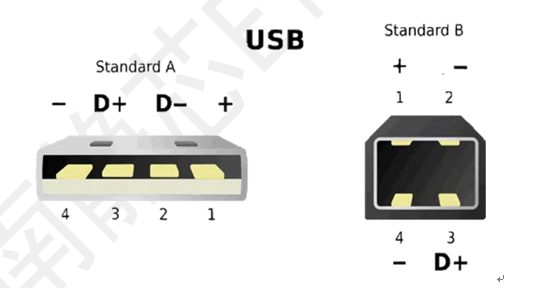

前面说的那些都是USB的协议版本,它代表的是版本的迭代,新的协议版本越高代表着传输速度会越快,至于上图中的接口外观出现了两种的类型一个Type-A、B和C三种类型。在AB两个版本里面各有三个级别一个标准版本,一个是mini版本和微接口版本。这就是为什么我们见到的USB接口为啥这么多的原因,协议不同接口不同就会多生出一个接口类型,但其实这都是属于USB接口范畴。

USB 3.0和USB 3.1 Gen1

其实上面的USB接口命名已经很多了,但是这个时候一个大佬可能是觉得这种命名不符合它的身份,为了彰显其魅力,并且为了体现它的先进性他把接口名称描述为USB3.1 Gen1,这个公司就是苹果,其在Macbook Pro电脑上使用了全新的USB Type-C接口,然后描述的是新一代的 USB 3.1 Gen1,大家都知道苹果公司的号召力的确不一般,因为它的这个改名举动,大量的厂商也开始玩起来这种换汤不换药的文字游戏,也纷纷改名。这迫使USB协会最终把USB3.0规范改名为USB3.1 Gen1,也就是说你用的USB3.0和USB 3.1 Gen1其实从传输速度和使用的协议来说是一模一样的东西。

总结:

1.USB 3.0接口通常为蓝色,一定会有5个以上的触点,而USB 2.0接口的触点不会超过5个;

2.USB 3.1 Gen1就是USB 3.0换了个马甲;

3.不要见到USB Type-C就以为它会更快,速度请认准USB 3.1 Gen2.

各个接口的实际传输速率

更高的传输标准

随着USB的传输数据的要求越来越高,比如外接显卡或者是通过USB接口外接高清显示器,这些要求对于USB传输的速率要求更高,即使是USB3.1都被提升到了10Gbps/秒也不能挡住对高速率和高功率版本输出的要求,这个时候又推出了USB3.1 Gen2,也有称为SuperSpeed+ USB,在USB3.1 Gen1的速度上翻了一倍,达到20Gbps/秒。

但是对于科技进步的探索,人类是永无止尽的,由于intel大力的推广雷电3接口技术,该技术该技术允许串接多台设备,并最终达到总40Gbps/秒的带宽,同时这一接口还能同时传输显示信号,并且能传送不超过100w的电力。也就是说雷电3接口可以保证在同一根线下面能够实现传输视频数据和电力输送功能,那么USB4.0直接也照办了这个协议,也就是说USB4.0不仅实现了速率的提升,还实现了雷电3协议所能提供的能力,真是集强大能力为一身啊。并且接口同一采用Type-C接口来实现接口的外观统一。

当然以上技术的实现,主要还是得感谢intel将私有化的Thunderbolt协议公开给大家来使用,才真正的促使了USB4.0的诞生。

因为USB4.0直连CPU的PCIE总线,最高传输速率能达到40Gbps,同时还能传输Displayport视频信号和USB PD快充电流的新一代USB外设传输协议,它本质上是Intel的Thunderbolt3技术,但同时也支持USB协议,因此它能完美向下兼容Thunderbolt3、USB3.2、USB3.1及USB2.0协议,这也就是为USB4.0即将开始大规模普及奠定了普及推广的基石。可以预见的是在未来我们所有的使用设备外接接口将会被USB 4.0所统一。

-

接口

+关注

关注

33文章

8563浏览量

150991 -

usb

+关注

关注

60文章

7927浏览量

264403 -

USB4

+关注

关注

1文章

141浏览量

6366

发布评论请先 登录

相关推荐

深入了解Java泛型——从前世今生到PECS原则

400Hz中频电源前世今生未来

带你揭秘:功率放大器的前世今生~

USB-C 与 USB-A 的区别

USB 4.0静电保护方案

求助,关于STM32F1 USB库Custom HID时钟问题求解

嵌入式系统的前世今生

cx3怎么能设置到usb3.0模式下?

FPGA中竞争与冒险的前世今生

探索世界军用无人机的前世今生

机器人的前世今生

浅析USB4.0的前世今生

浅析USB4.0的前世今生

评论