一、故障建模的基本概念

故障建模是生产测试的基础,在介绍故障建模前需要先理清集成电路中几个容易混淆的概念:缺陷、故障、误差和漏洞。

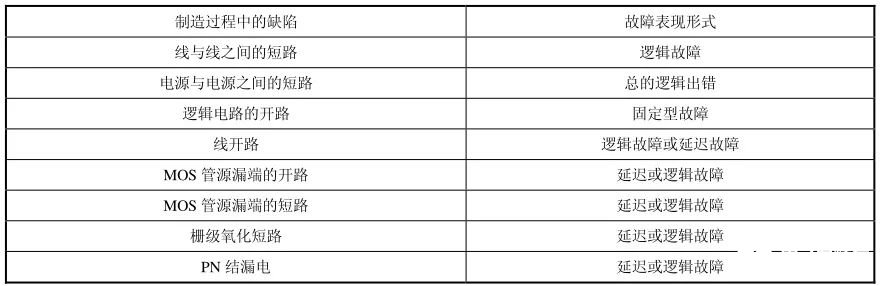

缺陷是指在集成电路制造过程中,在硅片上所产生的物理异常,如某些器件多余或被遗漏了。故障是指由于缺陷所表现出的不同于正常功能的现象,如电路的逻辑功能固定为1或0。误差是指由于故障而造成的系统功能的偏差和错误。漏洞是指由于一些设计问题而造成的功能错误,也就是常说的bug。表1列出了一些制造缺陷和相应的故障表现形式。

表1 制造缺陷和故障表现形式

在实际的芯片中,氧化层破裂、晶体管的寄生效应、硅表面不平整及电离子迁移等都可能造成一定程度的制造缺陷,并最终反映为芯片的功能故障。

故障建模是指以数学模型来模拟芯片制造过程中的物理缺陷,便于研究故障对电路或系统造成的影响,诊断故障的位置。为什么要进行故障建模呢?这是因为,电路中可能存在的物理缺陷是多种多样的,并且由于某些物理缺陷对于电路功能的影响过于复杂,不能被充分地理解,分析的难度很大。而故障化模型中的一个逻辑故障可以描述多种物理缺陷的行为,从而回避了对物理缺陷分析的复杂度。

二、常见故障模型

1.数字逻辑单元中的故障模型

在数字逻辑中常用的故障模型如下。

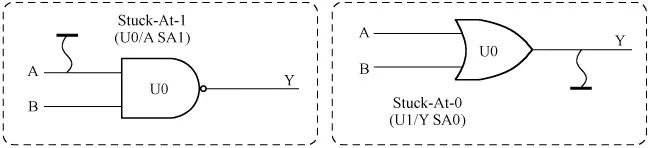

(1)固定型故障(SAF,Stuck At Fault)

这是在集成电路测试中使用最早和最普遍的故障模型,它假设电路或系统中某个信号永久地固定为逻辑0或者逻辑1,简记为SA0(Stuck-At-0)和SA1(Stuck-At-1),可以用来表征多种不同的物理缺陷。如图1所示,对于器件U0来说,SA1模拟了输入端口A的固定在逻辑1的故障,对于U1来说,SA0模拟了输出端口Y固定在逻辑0的故障。

图1 固定型故障

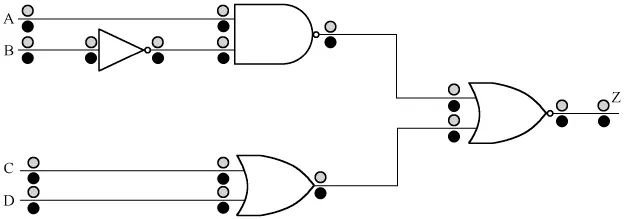

对于图2所示的组合电路,共包含2×(Npins+Nports)=2×(11+5)=32个固定型故障。

图2 固定型故障举例

下面的例子说明了故障合并的含义。对于图3所示的传输电路,端口A的SA0故障和端口Z的SA0故障等效,同样的端口A的SA1故障和端口Z的SA1故障等效,因此在考虑测试矢量集的时候可以合并故障,只需要从子故障集合{A:SA0,Z:SA0}和{A:SA1,Z:SA1}中各选择一个故障类型。

图3 故障的合并

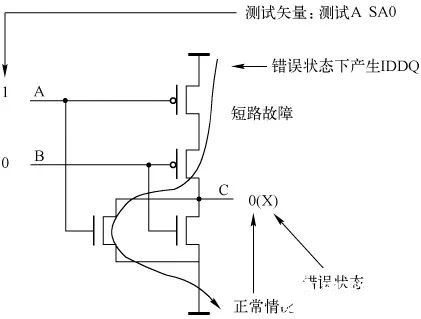

(2)晶体管固定开/短路故障(Stuck-open/Stuck-short)

在数字电路中,晶体管被认为是理想的开关元件,一般包含两种故障模型——固定开路故障和固定短路故障,分别如图4和图5所示。在检测固定开路故障的时候,需要两个测试矢量,第一测试矢量10用于初始化,可测试端口A的SA0故障,第二个测试矢量00用来测试端口A的SA1故障。对于固定短路故障的时候需要测量输出端口的静态电流。

图4 晶体管固定开路故障

图5 晶体管固定短路故障

(3)桥接故障(Bridging Faults)

桥接故障指节点间电路的短路故障,通常假象为电阻很小的通路,即只考虑低阻的桥接故障。桥接故障通常分为3类:逻辑电路与逻辑电路之间的桥接故障、节点间的无反馈桥接故障和节点间的反馈桥接故障。

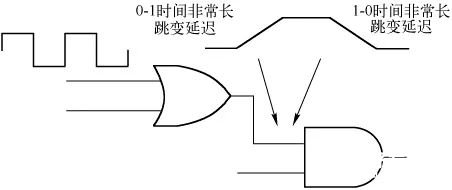

(4)跳变延迟故障(TF,Transition Delay Fault)

跳变延迟故障见图6,是指电路无法在规定时间内由0跳变到1或从1跳变到0的故障。在电路上经过一段时间的传输后,跳变延迟故障表现为固定型故障。

图6 跳变延迟故障

(5)传输延迟故障(Path Delay Fault)

传输延迟故障不同于跳变延迟故障,是指信号在特定路径上的传输延迟,通常与测试该路径相关AC参数联系在一起,尤其是关键路径。

2.存储器的故障模型

存储器的故障模型和数字逻辑中的故障模型有着显著的不同,虽然固定、桥接及晶体管固定开/短路故障模型对于数字逻辑有很好的模拟效果,但是用这些故障类型来确定存储器功能的正确性却是不充分的。除单元固定、桥接故障外,存储器故障还包括耦合、数据保留、临近图形敏感故障。

(1)单元固定故障(SAF,Stuck-At Fault)

单元固定故障指的是存储器单元固定在0或1。为了检测这类故障需要对每个存储单元和传输线进行读/写0和1的操作。

(2)状态跳变故障(TF,Transition Delay Fault)

状态跳变故障是固定故障的特殊类型,发生在对存储单元进行写操作的时候,不发生正常的跳变。这里需要指出的是跳变故障和固定故障不可相互替代,因为跳变故障可能在发生耦合故障时发生跳变,但是固定故障永远不可能改变。为了检测此类故障必须对每个单元进行0-1和1-0的读/写操作,并且要在写入相反值后立刻读出当前值。

(3)单元耦合故障(CF,Coupling Fault)

这些故障主要针对RAM,发生在一个单元进行写操作时,这个单元发生跳变的时候,会影响到另一个单元的内容。单元耦合可能是反相类型(CFin,inversion,单元内容反相)、等幂类型(CFid,idempotent,仅当单元有特定数据时单元的内容改变)或者简单的状态耦合(CFst,state,仅当其他位置有特定的数据时单元内容改变)。为了测试CF故障,要在对一个连接单元进行奇数次跳变后,对所有单元进行读操作,以避免可能造成的耦合故障。

(4)临近图形敏感故障(NPSF,Neighborhood Pattern Sensitive Faults)

这是一个特殊的状态耦合故障,见图7。此类故障意味着在特定存储单元周围的其他存储单元出现一些特定数据时,该单元会受到影响。

图7 临近图形敏感故障

(5)地址译码故障(ADF,Address Decode Fault)该故障主要有4类:

▪ 对于给定的地址,不存在相对应的存储单元;

▪ 对于一个存储单元,没有相对应的物理地址;

▪ 对于给定的地址,可以访问多个固定的存储单元;

▪ 对于一个存储单元,有多个地址可以访问。

(6)数据保留故障(DF,Data Retention Fault)

数据保留故障是指存储单元不能在规定时间内有效保持其数据值而出现的故障。这是一类动态的故障,对于SRAM来说相当重要,可以模拟DRAM数据刷新中数据固定和SRAM静态数据丢失等故障,有时对可编程的ROM和Flash存储器也十分重要。

三、ATPG基本原理

在抽象出有效故障模型的基础上,就可以开发各种自动测试产生(ATPG,Automatic Test Pattern Generation)向量了。目前,常用的ATPG算法有伪随机算法和AD-Hoc算法,对于组合逻辑来说还有D算法、PODEM算法和FAN算法。

利用软件程序可以实现ATPG算法,达到测试向量自动生成的目的。这里的测试向量是指为了使特定故障能够在原始输出端被观察到,而在被测电路原始输入端所施加的激励。通过软件程序,可以自动完成以下两项工作:

▪ 基于某种故障类型,确定当前测试矢量能够覆盖多少物理缺陷;

▪ 对于特定的抽象电路,工具能够自动选择能够匹配的故障模型。

这里涉及故障覆盖率的概念,故障覆盖率表示测试矢量集对于故障的覆盖程度:

故障覆盖率=被检测到的故障数目/被测电路的故障总数

可见,ATPG的优点是明显的。首先,它是一个自动的过程,所以它可以减少向量生成的时间,并且生成的向量可以用故障覆盖率的标准来衡量好坏;其次,ATPG是根据各类故障模型来生成向量的,因此一旦在测试机上发现错误,可以直接根据故障模型来追踪错误,能够很好地定位和诊断;另外,ATPG生成向量的有效性非常高,这里的有效性是指每个时钟周期所增长的故障覆盖率,节约了时钟周期也就是节约了测试程序,最终表现出是测试成本的节约。

另一种观点不利于ATPG的发展,有些人认为如果过于依赖ATPG,就会造成前端的设计必须与ATPG的设计要求相匹配,可能造成的后果是破坏原有的设计流程。还有支持问题,成功的ATPG需要包括库和EDA软件的支持。

四、ATPG的工作原理

ATPG采用故障模型,通过分析芯片的结构生成测试向量,进行结构测试,筛选出不合格的芯片。其中,最常用的故障模型就是固定故障模型。这在前面的存储器测试中提到过,下面就以这个模型来说明ATPG的工作原理。

该故障假设芯片的一个节点存在缺陷,假设SA0表示节点恒为低电平,相对地,SA1表示节点恒为高电平,即使控制目标节点的别的信号线都正常。例如,对于一个与门,只要将输入都变为1,就可以建立Stuck-At-0故障模型,如果输出为0则说明存在该故障。通过在芯片内建立这个故障模型,可以在芯片的顶层输入端口加上激励,在芯片的输出端口获取实际响应,根据希望响应与实际响应是否相同,来判断芯片是否存在制造缺陷。为了实现这样的目标,必须要求目标节点输入是可控制的,节点的输出是可观察的,并且目标节点不受别的节点影响,扫描链的结构为此提供了一切。对于ATPG软件来说,它的工作包括以下步骤。

(1)故障类型的选择

ATPG可以处理的故障类型不仅仅是阻塞型故障,还有延时故障和路径延时故障等,一旦所有需要检测的故障类型被列举,ATPG将对这些故障进行合理的排序,可能是按字母顺序、按层次结构排序,或者随机排序。

(2)检测故障

在确定了故障类型后,ATPG将决定如何对这类故障进行检测,并且需要考虑施加激励向量的测试点,需要计算所有会影响目标节点的可控制点。

(3)检测故障传输路径

寻找传输路径可以说是向量生成中最困难的,需要花很多时间去寻找故障的观测点的传播。因为通常一个故障拥有很多的可观测点,一些工具一般会找到最近的那一个。不同目标节点的传输路径可能会造成重叠和冲突,当然这在扫描结构中是不会出现的。

五、ATPG工具的使用步骤

目前,市场上的ATPG工具已经可以支持千万门级组合逻辑和全扫描电路的测试矢量生成。最有名的就是Synopsys的TetraMAX和Mentor的Fastscan。

例如Synopsys的TetraMAX,它支持全扫描设计和局部扫描设计,支持多种扫描风格,支持IEEE 1149.1标准。设计步骤如下。

① 将含扫描结构的门级网表输入到ATPG工具。

② 输入库文件。必须与门级网表相对应并且能被ATPG工具识别。

③ 建立ATPG模型。输入库文件后,ATPG工具将根据库文件和网表文件建立模型。

④ 根据STIL文件做DRC检测。STIL文件是标准测试接口文件,包含扫描结构的一系列信息和信号的约束。

⑤ 生成向量。这里需要选择建立哪种故障模型。

⑥ 压缩向量。这一步骤可以节约将来芯片测试时候的工作站资源和测试时间。

⑦ 转换ATPG模式的向量为ATE所需要格式的测试向量。

⑧ 输出测试向量和故障列表。

其中,故障列表为将来测试诊断用,可以发现芯片的制造缺陷,生成向量以后需要进行实际的电路仿真,确定故障覆盖率满足要求。

责任编辑:gt

-

芯片

+关注

关注

455文章

50714浏览量

423139 -

集成电路

+关注

关注

5387文章

11530浏览量

361632

发布评论请先 登录

相关推荐

MESFET集成电路应用-概述

集成电路(IC)常用基本概念

关于数字电路的基本概念和学习内容

集成电路的检测及故障查寻

模拟集成电路与系统图书

MESFET集成电路应用

集成电路故障建模的基本概念与ATPG工具的使用步骤

集成电路故障建模的基本概念与ATPG工具的使用步骤

评论