在完成MOS管芯片在制作之后,需要给MOS管芯片加上一个外壳,这就是MOS管封装。该封装外壳主要起着支撑、保护和冷却的作用,同时还可为芯片提供电气连接和隔离,从而将MOS管器件与其它元件构成完整的电路。

而不同的封装、不同的设计,MOS管的规格尺寸、各类电性参数等都会不一样,而它们在电路中所能起到的作用也会不一样;另外,封装还是电路设计中MOS管选择的重要参考。封装的重要性不言而喻,今天我们就来聊聊MOS管封装的那些事。

MOS管封装分类

按照安装在PCB板上的方式来划分,MOS管封装主要有两大类:插入式(Through Hole)和表面贴装式(Surface Mount)。

插入式就是MOSFET的管脚穿过PCB板的安装孔并焊接在PCB板上。常见的插入式封装有:双列直插式封装(DIP)、晶体管外形封装(TO)、插针网格阵列封装(PGA)三种样式。

插入式封装

表面贴裝则是MOSFET的管脚及散热法兰焊接在PCB板表面的焊盘上。典型表面贴装式封装有:晶体管外形(D-PAK)、小外形晶体管(SOT)、小外形封装(SOP)、方形扁平式封装(QFP)、塑封有引线芯片载体(PLCC)等。

表面贴装式封装

随着技术的发展,目前主板、显卡等的PCB板采用直插式封装方式的越来越少,更多地选用了表面贴装式封装方式。

1、双列直插式封装(DIP)

DIP封装有两排引脚,需要插入到具有DIP结构的芯片插座上,其派生方式为SDIP(Shrink DIP),即紧缩双入线封装,较DIP的针脚密度高6倍。

DIP封装结构形式有:多层陶瓷双列直插式DIP、单层陶瓷双列直插式DIP、引线框架式DIP(含玻璃陶瓷封接式、塑料包封结构式、陶瓷低熔玻璃封装式)等。DIP封装的特点是可以很方便地实现PCB板的穿孔焊接,和主板有很好的兼容性。

但由于其封装面积和厚度都比较大,而且引脚在插拔过程中很容易被损坏,可靠性较差;同时由于受工艺的影响,引脚一般都不超过100个,因此在电子产业高度集成化过程中,DIP封装逐渐退出了历史舞台。

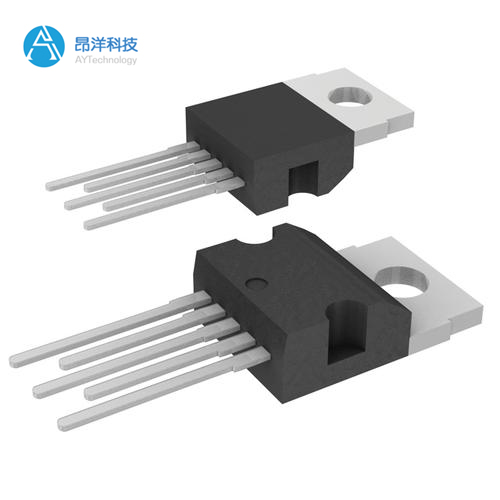

2、晶体管外形封装(TO)

属于早期的封装规格,例如TO-3P、TO-247、TO-92、TO-92L、TO-220、TO-220F、TO-251等都是插入式封装设计。

TO-3P/247:是中高压、大电流MOS管常用的封装形式,产品具有耐压高、抗击穿能力强等特点。

TO-220/220F:TO-220F是全塑封装,装到散热器上时不必加绝缘垫;TO-220带金属片与中间脚相连,装散热器时要加绝缘垫。这两种封装样式的MOS管外观差不多,可以互换使用。

TO-251:该封装产品主要是为了降低成本和缩小产品体积,主要应用于中压大电流60A以下、高压7N以下环境中。

TO-92:该封装只有低压MOS管(电流10A以下、耐压值60V以下)和高压1N60/65在采用,目的是降低成本。

近年来,由于插入式封装工艺焊接成本高、散热性能也不如贴片式产品,使得表面贴装市场需求量不断增大,也使得TO封装发展到表面贴装式封装。TO-252(又称之为D-PAK)和TO-263(D2PAK)就是表面贴装封装。

TO封装产品外观

TO252/D-PAK是一种塑封贴片封装,常用于功率晶体管、稳压芯片的封装,是目前主流封装之一。

采用该封装方式的MOSFET有3个电极,栅极(G)、漏极(D)、源极(S)。

其中漏极(D)的引脚被剪断不用,而是使用背面的散热板作漏极(D),直接焊接在PCB上,一方面用于输出大电流,一方面通过PCB散热;所以PCB的D-PAK焊盘有三处,漏极(D)焊盘较大。其封装规范如下:

TO-252/D-PAK封装尺寸规格

TO-263是TO-220的一个变种,主要是为了提高生产效率和散热而设计,支持极高的电流和电压,在150A以下、30V以上的中压大电流MOS管中较为多见。

除了D2PAK(TO-263AB)之外,还包括TO263-2、TO263-3、TO263-5、TO263-7等样式,与TO-263为从属关系,主要是引出脚数量和距离不同。

TO-263/D2PAK封装尺寸规格

3、插针网格阵列封装(PGA)

PGA(Pin Grid Array Package)芯片内外有多个方阵形的插针,每个方阵形插针沿芯片的四周间隔一定距离排列,根据管脚数目的多少,可以围成2~5圈。安装时,将芯片插入专门的PGA插座即可,具有插拔方便且可靠性高的优势,能适应更高的频率。

PGA封装样式

其芯片基板多数为陶瓷材质,也有部分采用特制的塑料树脂来做基板,在工艺上,引脚中心距通常为2.54mm,引脚数从64到447不等。

这种封装的特点是,封装面积(体积)越小,能够承受的功耗(性能)就越低,反之则越高。这种封装形式芯片在早期比较多见,且多用于CPU等大功耗产品的封装,如英特尔的80486、Pentium均采用此封装样式;不大为MOS管厂家所采纳。

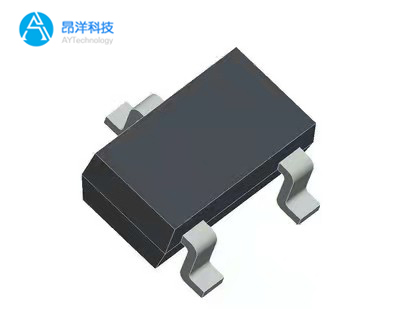

4、小外形晶体管封装(SOT)

SOT(Small Out-Line Transistor)是贴片型小功率晶体管封装,主要有SOT23、SOT89、SOT143、SOT25(即SOT23-5)等,又衍生出SOT323、SOT363/SOT26(即SOT23-6)等类型,体积比TO封装小。

SOT封装类型

SOT23是常用的三极管封装形式,有3条翼形引脚,分别为集电极、发射极和基极,分别列于元件长边两侧,其中,发射极和基极在同一侧,常见于小功率晶体管、场效应管和带电阻网络的复合晶体管,强度好,但可焊性差,外形如下图(a)所示。

SOT89具有3条短引脚,分布在晶体管的一侧,另外一侧为金属散热片,与基极相连,以增加散热能力,常见于硅功率表面组装晶体管,适用于较高功率的场合,外形如下图(b)所示。

SOT143具有4条翼形短引脚,从两侧引出,引脚中宽度偏大的一端为集电极,这类封装常见于高频晶体管,外形如下图(c)所示。

SOT252属于大功率晶体管,3条引脚从一侧引出,中间一条引脚较短,为集电极,与另一端较大的引脚相连,该引脚为散热作用的铜片,外形如下图(d)所示。

常见SOT封装外形比较

主板上常用四端引脚的SOT-89 MOSFET。其规格尺寸如下:

SOT-89 MOSFET尺寸规格(单位:mm)

5、小外形封装(SOP)

SOP(Small Out-Line Package)是表面贴装型封装之一,也称之为SOL或DFP,引脚从封装两侧引出呈海鸥翼状(L字形)。材料有塑料和陶瓷两种。

SOP封装标准有SOP-8、SOP-16、SOP-20、SOP-28等,SOP后面的数字表示引脚数。MOSFET的SOP封装多数采用SOP-8规格,业界往往把“P”省略,简写为SO(Small Out-Line)。

SOP-8封装尺寸

SO-8为PHILIP公司率先开发,采用塑料封装,没有散热底板,散热不良,一般用于小功率MOSFET。

后逐渐派生出TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)等标准规格;其中TSOP和TSSOP常用于MOSFET封装。

常用于MOS管的SOP派生规格

6、方形扁平式封装(QFP)

QFP(Plastic Quad Flat Package)封装的芯片引脚之间距离很小,管脚很细,一般在大规模或超大型集成电路中采用,其引脚数一般在100个以上。

用这种形式封装的芯片必须采用SMT表面安装技术将芯片与主板焊接起来。该封装方式具有四大特点:

①适用于SMD表面安装技术在PCB电路板上安装布线;

②适合高频使用;

③操作方便,可靠性高;

④芯片面积与封装面积之间的比值较小。

与PGA封装方式一样,该封装方式将芯片包裹在塑封体内,无法将芯片工作时产生的热量及时导出,制约了MOSFET性能的提升;而且塑封本身增加了器件尺寸,不符合半导体向轻、薄、短、小方向发展的要求;另外,此类封装方式是基于单颗芯片进行,存在生产效率低、封装成本高的问题。

因此,QFP更适于微处理器/门陈列等数字逻辑LSI电路采用,也适于VTR信号处理、音响信号处理等模拟LSI电路产品封装。

7、四边无引线扁平封装(QFN)

QFN(Quad Flat Non-leaded package)封装四边配置有电极接点,由于无引线,贴装表现出面积比QFP小、高度比QFP低的特点;其中陶瓷QFN也称为LCC(Leadless Chip Carriers),采用玻璃环氧树脂印刷基板基材的低成本塑料QFN则称为塑料LCC、PCLC、P-LCC等。

是一种焊盘尺寸小、体积小、以塑料作为密封材料的新兴表面贴装芯片封装技术。

QFN主要用于集成电路封装,MOSFET不会采用。不过因Intel提出整合驱动与MOSFET方案,而推出了采用QFN-56封装(“56”指芯片背面有56个连接Pin)的DrMOS。

需要说明的是,QFN封装与超薄小外形封装(TSSOP)具有相同的外引线配置,而其尺寸却比TSSOP的小62%。根据QFN建模数据,其热性能比TSSOP封装提高了55%,电性能(电感和电容)比TSSOP封装分别提高了60%和30%。最大的缺点则是返修难度高。

采用QFN-56封装的DrMOS

传统的分立式DC/DC降压开关电源无法满足对更高功耗密度的要求,也不能解决高开关频率下的寄生参数影响问题。

随着技术的革新与进步,把驱动器和MOSFET整合在一起,构建多芯片模块已经成为了现实,这种整合方式同时可以节省相当可观的空间从而提升功耗密度,通过对驱动器和MOS管的优化提高电能效率和优质DC电流,这就是整合驱动IC的DrMOS。

瑞萨第2代DrMOS

经过QFN-56无脚封装,让DrMOS热阻抗很低;借助内部引线键合以及铜夹带设计,可最大程度减少外部PCB布线,从而降低电感和电阻。

另外,采用的深沟道硅(trench silicon)MOSFET工艺,还能显著降低传导、开关和栅极电荷损耗;并能兼容多种控制器,可实现不同的工作模式,支持主动相变换模式APS(Auto Phase Switching)。

除了QFN封装外,双边扁平无引脚封装(DFN)也是一种新的电子封装工艺,在安森美的各种元器件中得到了广泛采用,与QFN相比,DFN少了两边的引出电极。

8、塑封有引线芯片载体(PLCC)

PLCC(Plastic Quad Flat Package)外形呈正方形,尺寸比DIP封装小得多,有32个引脚,四周都有管脚,引脚从封装的四个侧面引出,呈丁字形,是塑料制品。

其引脚中心距1.27mm,引脚数从18到84不等,J形引脚不易变形,比QFP容易操作,但焊接后的外观检查较为困难。PLCC封装适合用SMT表面安装技术在PCB上安装布线,具有外形尺寸小、可靠性高的优点。

PLCC封装是比较常见,用于逻辑LSI、DLD(或程逻辑器件)等电路,主板BIOS常采用的这种封装形式,不过目前在MOS管中较少见。

PLCC封装样式

主流企业的封装与改进

由于CPU的低电压、大电流的发展趋势,对MOSFET提出输出电流大,导通电阻低,发热量低散热快,体积小的要求。MOSFET厂商除了改进芯片生产技术和工艺外,也不断改进封装技术,在与标准外形规格兼容的基础上,提出新的封装外形,并为自己研发的新封装注册商标名称。

1、瑞萨(RENESAS)WPAK、LFPAK和LFPAK-I封装

WPAK是瑞萨开发的一种高热辐射封装,通过仿D-PAK封装那样把芯片散热板焊接在主板上,通过主板散热,使小形封装的WPAK也可以达到D-PAK的输出电流。WPAK-D2封装了高/低2颗MOSFET,减小布线电感。

瑞萨WPAK封装尺寸

LFPAK和LFPAK-I是瑞萨开发的另外2种与SO-8兼容的小形封装。LFPAK类似D-PAK,但比D-PAK体积小。LFPAK-i是将散热板向上,通过散热片散热。

瑞萨LFPAK和LFPAK-I封装

2、威世(Vishay)Power-PAK和Polar-PAK封装

Power-PAK是威世公司注册的MOSFET封装名称。Power-PAK包括有Power-PAK1212-8、Power-PAK SO-8两种规格。

威世Power-PAK1212-8封装

威世Power-PAK SO-8封装

Polar PAK是双面散热的小形封装,也是威世核心封装技术之一。Polar PAK与普通的so-8封装相同,其在封装的上、下两面均设计了散热点,封装内部不易蓄热,能够将工作电流的电流密度提高至SO-8的2倍。目前威世已向意法半导体公司提供Polar PAK技术授权。

威世Polar PAK封装

3、安森美(Onsemi)SO-8和WDFN8扁平引脚(Flat Lead)封装

安美森半导体开发了2种扁平引脚的MOSFET,其中SO-8兼容的扁平引脚被很多板卡采用。安森美新近推出的NVMx和NVTx功率MOSFET就采用了紧凑型DFN5(SO-8FL)和WDFN8封装,可最大限度地降低导通损耗,另外还具有低QG和电容,可将驱动器损耗降到最低的特性。

安森美SO-8扁平引脚封装

安森美WDFN8封装

4、恩智浦(NXP)LFPAK和QLPAK封装

恩智浦(原Philps)对SO-8封装技术改进为LFPAK和QLPAK。其中LFPAK被认为是世界上高度可靠的功率SO-8封装;而QLPAK具有体积小、散热效率更高的特点,与普通SO-8相比,QLPAK占用PCB板的面积为6*5mm,同时热阻为1.5k/W。

恩智浦LFPAK封装

恩智浦QLPAK封装

5、意法(ST)半导体PowerSO-8封装

意法半导体功率MOSFET芯片封装技术有SO-8、PowerSO-8、PowerFLAT、DirectFET、PolarPAK等,其中PowerSO-8正是SO-8的改进版,此外还有PowerSO-10、PowerSO-20、TO-220FP、H²PAK-2等封装。

意法半导体Power SO-8封装

6、飞兆(Fairchild)半导体Power 56封装

Power 56是Farichild的专用称呼,正式名称为DFN 5×6。其封装面积跟常用的TSOP-8不相上下,而薄型封装又节约元件净空高度,底部Thermal-Pad设计降低了热阻,因此很多功率器件厂商都部署了DFN 5×6。

Fairchild Power 56封装

7、国际整流器(IR)Direct FET封装

Direct FET能在SO-8或更小占位面积上,提供高效的上部散热,适用于计算机、笔记本电脑、电信和消费电子设备的AC-DC及DC-DC功率转换应用。与标准塑料分立封装相比,DirectFET的金属罐构造具有双面散热功能,因而可有效将高频DC-DC降压式转换器的电流处理能力增加一倍。

Direct FET封装属于反装型,漏极(D)的散热板朝上,并覆盖金属外壳,通过金属外壳散热。Direct FET封装极大地改善了散热,并且占用空间更小,散热良好。

国际整流器Direct FET封装

IR Direct FET封装系列部分产品规格

内部封装改进方向

除了外部封装,基于电子制造对MOS管的需求的变化,内部封装技术也在不断得到改进,这主要从三个方面进行:改进封装内部的互连技术、增加漏极散热板、改变散热的热传导方向。

1、封装内部的互连技术

TO、D-PAK、SOT、SOP等采用焊线式的内部互连封装技术,当CPU或GPU供电发展到低电压、大电流时代,焊线式的SO-8封装就受到了封装电阻、封装电感、PN结到PCB和外壳热阻等因素的限制。

SO-8内部封装结构

这四种限制对其电学和热学性能有着极大的影响。随着电流密度的提高,MOSFET厂商在采用SO-8尺寸规格时,同步对焊线互连形式进行了改进,用金属带、或金属夹板代替焊线,以降低封装电阻、电感和热阻。

标准型SO-8与无导线SO-8封装对比

国际整流器(IR)的改进技术称之为Copper Strap;威世(Vishay)称之为Power Connect技术;飞兆半导体则叫做Wireless Package。新技术采用铜带取代焊线后,热阻降低了10-20%,源极至封装的电阻降低了61%。

国际整流器的Copper Strap技术

威世的Power Connect技术

飞兆半导体的Wirless Package技术

2、增加漏极散热板

标准的SO-8封装采用塑料将芯片包围,低热阻的热传导通路只是芯片到PCB的引脚。而底部紧贴PCB的塑料外壳是热的不良导体,故而影响了漏极的散热。

技术改进就是要除去引线框下方的塑封化合物,方法是让引线框金属结构直接或加一层金属板与PCB接触,并焊接到PCB焊盘上,这样就提供了更多的散热接触面积,把热量从芯片上带走;同时也可以制成更薄的器件。

威世Power-PAK技术

威世的Power-PAK、法意半导体的Power SO-8、安美森半导体的SO-8 Flat Lead、瑞萨的WPAK/LFPAK、飞兆半导体的Power 56和Bottomless Package都采用了此散热技术。

3、改变散热的热传导方向

Power-PAK的封装虽然显著减小了芯片到PCB的热阻,但当电流需求继续增大时,PCB同时会出现热饱和现象。所以散热技术的进一步改进就是改变散热方向,让芯片的热量传导到散热器而不是PCB。

瑞萨LFPAK-i封装

瑞萨的LFPAK-I封装、国际整流器的Direct FET封装均是这种散热技术的典型代表。

总结

未来,随着电子制造业继续朝着超薄、小型化、低电压、大电流方向的发展,MOS管的外形及内部封装结构也会随之改变,以更好适应制造业的发展需求。另外,为降低电子制造商的选用门槛,MOS管向模块化、系统级封装方向发展的趋势也将越来越明显,产品将从性能、成本等多维度协调发展。

而封装作为MOS管选型的重要参考因素之一,不同的电子产品有不同的电性要求,不同的安装环境也需要匹配的尺寸规格来满足。实际选用中,应在大原则下,根据实际需求情况来做抉择。

有些电子系统受制于PCB的尺寸和内部的高度,如通信系统的模块电源由于高度的限制通常采用DFN5*6、DFN3*3的封装;在有些ACDC的电源中,使用超薄设计或由于外壳的限制,适于装配TO220封装的功率MOS管,此时引脚可直接插到根部,而不适于使用TO247封装的产品;也有些超薄设计需要将器件管脚折弯平放,这会加大MOS管选用的复杂度。

lw

-

封装

+关注

关注

127文章

8142浏览量

143851 -

MOS管

+关注

关注

108文章

2469浏览量

68241 -

瑞萨

+关注

关注

36文章

22323浏览量

87181

发布评论请先 登录

相关推荐

MOS管的封装类型

MOS管的封装类型

评论