(文章来源:网络整理)

该行业正在不断刷新纳米芯片的记录,这无疑将为我们带来更多的未来计算可能性。为此,来自世界各地的研究人员正在不断努力。最近,一个国际研究小组在其报告中表示,它在纳米芯片的制造方面取得了突破性进展,或者它将对纳米芯片的生产以及全球所有纳米技术实验室产生重大影响。

据报道,该研究团队由纽约大学工程学院化学与生物分子工程教授Riedo领导。他们表明,使用加热到100摄氏度以上的探针进行光刻比二维半导体要好(例如,制造金属二硫化钼(MoS2)的方法更便宜,并且有望成为替代方法)。到今天的电子束光刻。

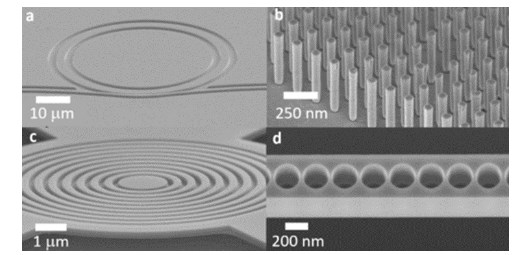

该团队将这种新的制造方法称为热扫描探针光刻(t-SPL),它比当今的电子束光刻(EBL)更具优势:首先,热光刻技术取得了重大进展。一维晶体管的质量抵消了肖特基势垒,并阻碍了金属和二维衬底的结点处的电子流动。与EBL不同,热光刻技术使芯片设计人员可以轻松地对半导体尺寸进行成像,然后在需要时对电极进行构图。此外,热扫描探针光刻(t-SPL)制造系统有望从一开始就节省成本。最后,通过使用平行热探针,热制造方法可以轻松地扩展到大规模工业生产。

Elisa Riedo教授和博士生Liu Xiangyu他们使用热扫描探针光刻技术和SwissLitho的NanoFrazor设备在纽约大学Tandon工程学院的PicoForce实验室生产高质量的2D芯片。

Riedo博士希望t-SPL最终能够从实验室转移到工厂进行批量生产。为了实现这一愿景,研究人员仍然需要继续努力,以快速推进材料科学和芯片设计。有一天,这些t-SPL工具的分辨率将小于10纳米,并且将在标准环境条件下使用120伏电源运行。

实际上,Riedo在热测试方面的经验可以追溯到十年以上,首先是在IBM Research-Zurich,然后是纽约城市大学研究生中心(CUNY)的高级科学研究中心(ASRC)。

(责任编辑:fqj)

-

纳米芯片

+关注

关注

0文章

50浏览量

14471 -

光刻技术

+关注

关注

1文章

146浏览量

15814

发布评论请先 登录

相关推荐

美投资8.25亿美元建设NSTC关键设施,重点发展EUV光刻技术

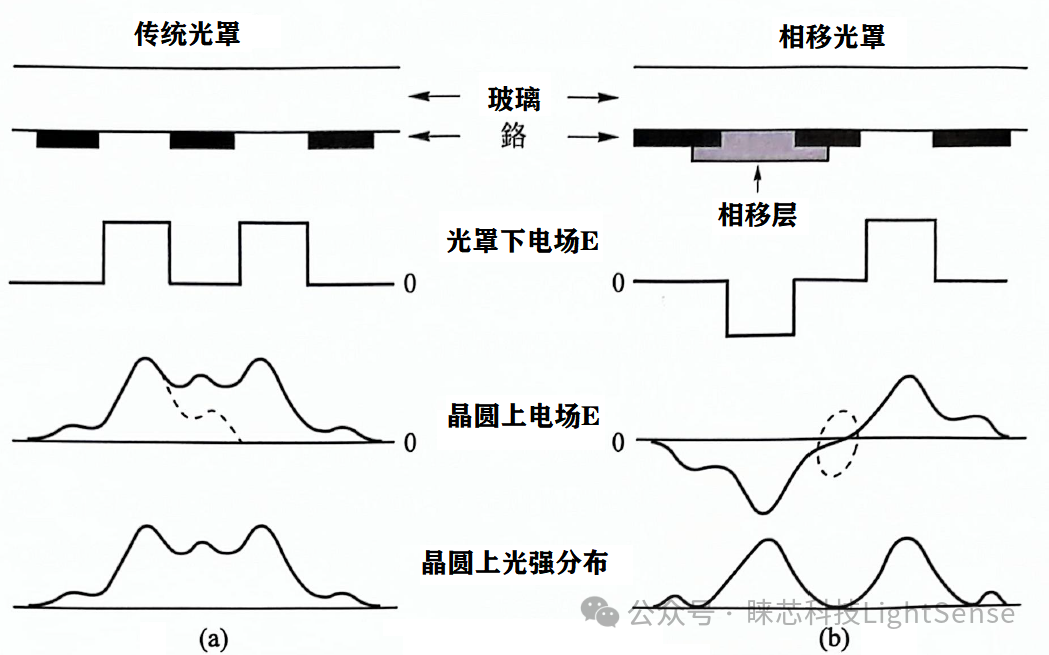

光刻工艺中分辨率增强技术详解

新思科技发布1.6纳米背面布线技术,助力万亿晶体管芯片发展

日本大学研发出新极紫外(EUV)光刻技术

据新华社等多家媒体报道!畅能达科技实现散热技术重大突破!

光刻机的基本原理和核心技术

光刻机的发展历程及工艺流程

美光计划部署纳米印刷技术,降低DRAM芯片生产成本

佳能预计到2024年出货纳米压印光刻机

新光刻技术将会对纳米芯片的发展产生重大影响

新光刻技术将会对纳米芯片的发展产生重大影响

评论