中芯国际的该项专利通过在第一鳍部层和源漏掺杂层之间形成阻挡层,阻挡层中的第一离子填充阻挡层材料的原子间隙,使得源漏掺杂层中的源漏离子无法进入到阻挡层的原子晶格间隙中,从而抑制源漏掺杂层中的源漏掺杂离子进入第一鳍部层,减小了短沟道效应,提高了鳍型半导体器件的性能。

集微网消息, 作为国内最大的晶圆代工厂,中芯国际在2019年向美国泛林半导体公司购买了大量半导体设备,如蚀刻机、CVD(化学气相沉积)等,极大加速了14nm和12nm工艺的生产能力。与此同时,中芯国际大力发展7nm工艺,加速国内芯片发展。

在半导体制造领域,根据摩尔定律,半导体器件一直向着更高的元件密度,以及更高的集成度方向发展,并广泛应用于工业体系中。然而传统的平面器件由于对沟道电流的控制能力弱,会产生短沟道效应而导致漏电流,从而影响半导体器件的电学性能。为避免硅基平面场效应晶体管由于尺寸减小带来的短沟道效应等缺陷,鳍式晶体管(FinFET)将沟道和栅极制备成类似于鱼鳍(Fin)的竖直形态,将半导体衬底、阻挡层、栅极、源极和漏极分别放置于鳍式结构的表面与侧壁,为了减小源漏掺杂层与后续形成的插塞之间的接触电阻,现有技术多采用提高源漏掺杂层的掺杂浓度的方式,使得沟道区中具有源漏掺杂离子,导致了短沟道效应,所形成的半导体器件性能较差,很难应用于工业生产中。

在这种情况下,中芯国际公司早在2018年5月25日就提出一项名为“半导体器件及其形成方法”的发明专利(专利号:201810516529.7),申请人为中芯国际集成电路制造(上海)有限公司。该专利主要提供了一种鳍式半导体器件及其形成方法,以提高半导体器件的性能。

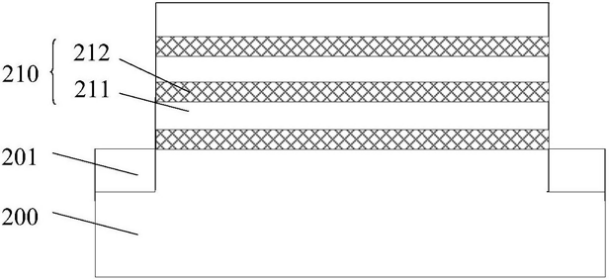

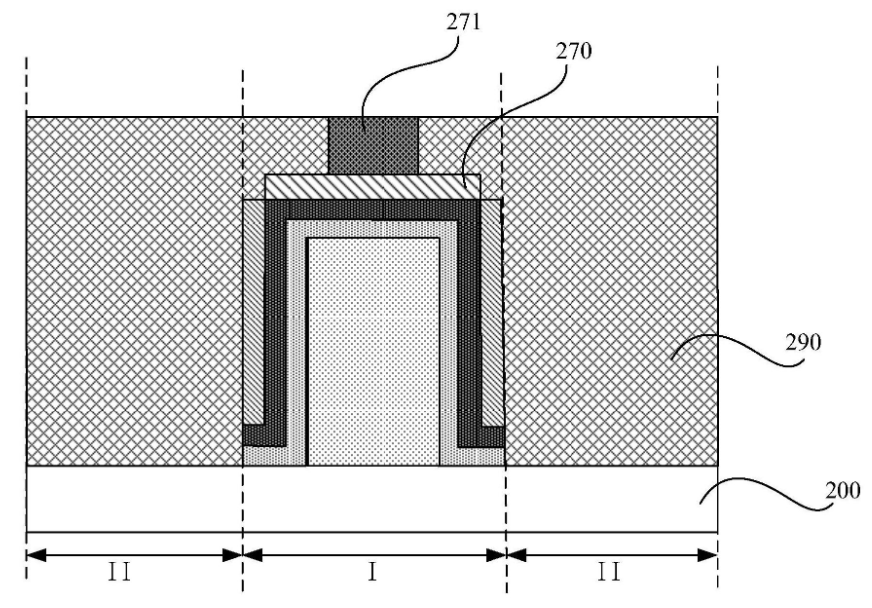

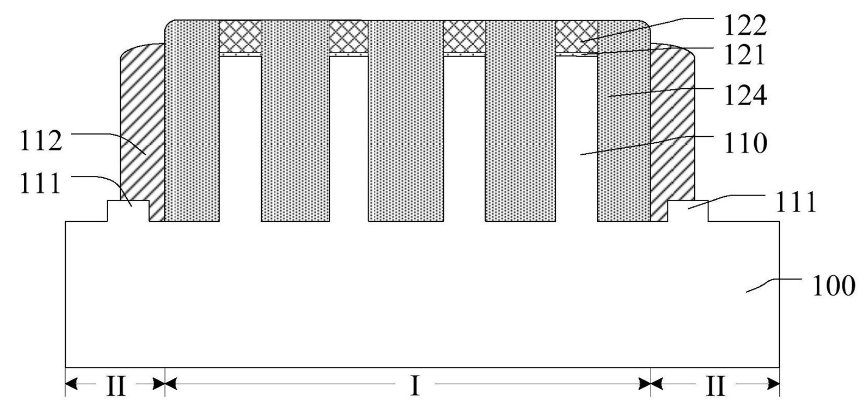

图1 鳍式半导体器件初始结构

图1中首先提供了半导体衬底200,可为单晶硅、多晶硅、非晶硅或者其他硅、锗、锗化硅、砷化镓等半导体材料。在衬底200上具有鳍部210,鳍部210包括多层沿半导体衬底表面法线方向重叠的第一鳍部层211、以及位于相邻两层的第二鳍部层212,这两层鳍部材料为单晶硅或者单晶锗硅。在图1中,半导体衬底200上形成隔离结构201,覆盖鳍部结构210的部分侧壁,同时隔离结构201的顶部表面低于鳍部210的顶部表面。

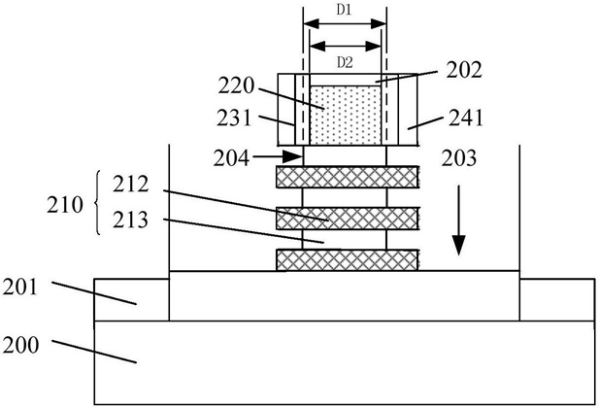

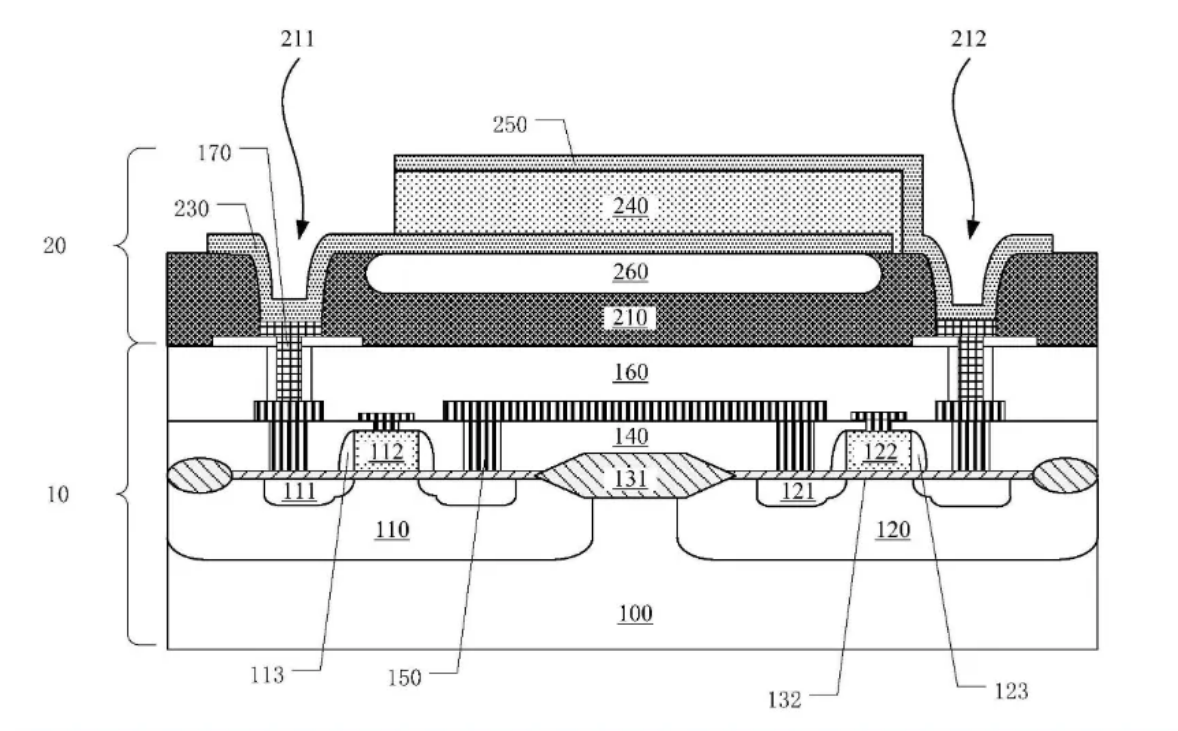

图2 鳍式半导体中间结构

在图2中,半导体的伪栅极结构本体包括伪栅极层220、位于其顶部表面的保护层202以及覆盖伪栅极结构本体侧壁的侧墙,包括第一侧墙231和第二侧墙241。其中第一侧墙231在离子注入形成轻掺杂区的过程中保护伪栅极结构,并且能定义轻掺杂区的位置,第二侧墙241位于伪栅极结构220和第一侧墙231两侧,覆盖第一侧墙231侧壁表面。为定义后续形成的栅极结构和源漏掺杂层之间的距离,在伪栅极结构两侧的鳍部内形成第一凹槽203,从而为后续形成源漏掺杂层提供空间。同时去除侧壁部分凹陷,形成凹槽204,并保证第一宽度D1小于所述第二宽度D2,从而使得后续形成的半导体器件的沟道距离变长,载流子通道变大。

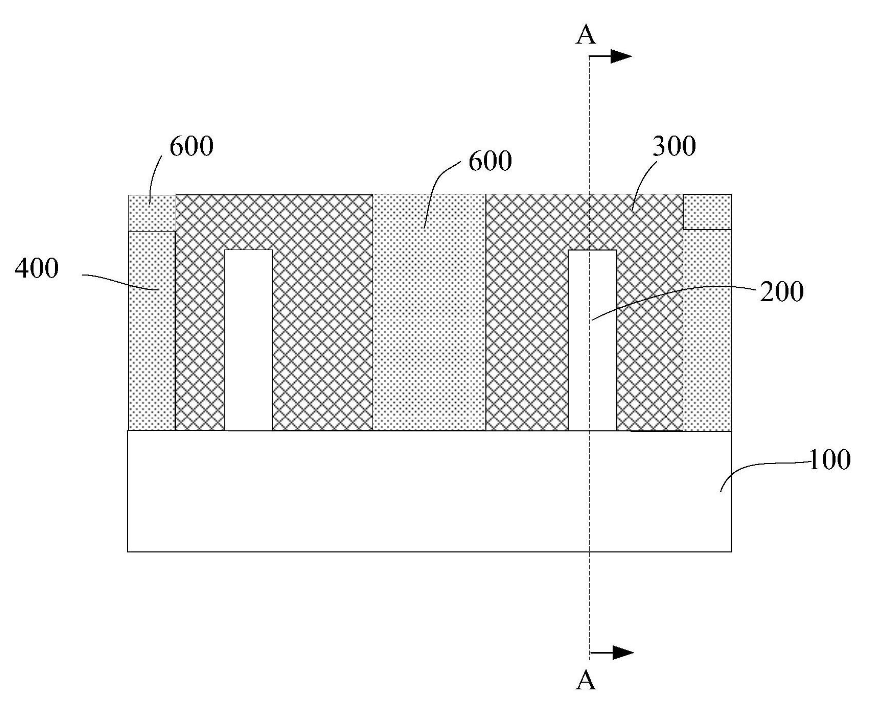

最后,此专利通过在第一鳍部层和源漏掺杂层之间形成阻挡层,阻挡层中的第一离子填充阻挡层材料的原子间隙,使得源漏掺杂层中的源漏离子无法进入到阻挡层的原子晶格间隙中,从而抑制源漏掺杂层中的源漏掺杂离子进入第一鳍部层,减小了短沟道效应,提高了鳍型半导体器件的性能。

单原子层沟道的鳍型场效应管是国内半导体领域竞相研究的热点内容,而中芯国际提出的此项有关鳍型半导体的制作工艺与方法具有很强的指导意义,希望国内企业能够在这方面向单原子层沟道方向进行努力突破,实现半导体领域的创新发展。

-

半导体

+关注

关注

334文章

27471浏览量

219577 -

中芯国际

+关注

关注

27文章

1418浏览量

65397

发布评论请先 登录

相关推荐

中国半导体专利申请激增,万年芯134项专利深耕行业

p型半导体是怎么形成的

东芯半导体闪耀2024年上海国际嵌入式展

KOWIN存储芯璀璨亮相南京国际半导体大会

中芯国际获非易失性存储装置及其制作方法专利

中芯国际鳍式半导体器件及其形成方法专利

中芯国际鳍式半导体器件及其形成方法专利

评论