(文章来源:网络整理)

我们经常看到报道上说芯片制程达到了14nm、7nm、5nm,最近中芯国际在没有ASML的EUV光刻机的情况下,实现了7nm的制程,有很多人对此感到很兴奋。同时也有人问,半导体的多少纳米制程,到底是指晶体管间距多少纳米,还是晶体管的大小是多少纳米?要回答这个问题,我们得从一个晶体管单位的组成说起。

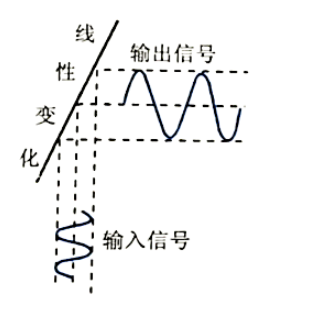

晶体管工作的时候,电流从源极(Source)流入漏极(Drain),中间绿色的那堵墙叫作栅极(Gate),相当于一个闸门,它负责控制源极和漏极之间电流的通断。而电流通过栅极(Gate)时会损耗,栅极的宽度就决定了损耗的大小。表现在芯片上,就是芯片的发热和功耗,栅极越窄,芯片的功耗就越小。

栅极的最小宽度(栅长,就是上面右图Gate的宽度)就是多少nm工艺中的数值了。在实际芯片制程工艺中,越小的制程工艺,不但对制造工艺和设备有更高的要求,其芯片性能也会受到极大的影响。当宽度逼近20nm的时候,栅极对电流的控制能力就会急剧下降,从而发生“漏电”的问题。

漏电会导致芯片的功耗上升,更会使电路发生错误,信号模糊。为了解决信号模糊的问题,芯片又不得不提高核心电压,使得功耗更大。这对于更小工艺制程来说,是一个矛盾。

为了解决这个问题,台积电和三星等芯片制造企业,提出了FinFET工艺。这种工艺,简单来说,就是将芯片内部平面的结构,变成了立体的,把栅极形状改制,增大接触面积,减少栅极宽度的同时降低漏电率,而晶体管空间利用率大大增加。

FinFET(鳍式场效应晶体管),是一种新型的晶体管,这种被称为CMOS的工艺优势很明显,很快就被大规模应用于手机芯片上。

然而,在5nm以下的制程芯片中,影响芯片性能的除了漏电问题之外,更大的是量子效应的影响,这时芯片的特性更难控制,科学家们要寻求新工艺才能使芯片更进一步。

业内正在发展的一种新技术叫做环绕式栅极技术(Gate-All-Around),简称为GAA横向晶体管技术(GAAFET)。这项技术的特点是实现了栅极对沟道的四面包裹,源极和漏极不再和基底接触,而是利用线状(可以理解为棍状)或者平板状、片状等多个源极和漏极横向垂直于栅极分布后,实现MOSFET的基本结构和功能。

(责任编辑:fqj)

-

芯片

+关注

关注

455文章

50689浏览量

423028 -

晶体管

+关注

关注

77文章

9679浏览量

138051

发布评论请先 登录

相关推荐

晶体管与场效应管的区别 晶体管的封装类型及其特点

麻省理工学院研发全新纳米级3D晶体管,突破性能极限

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

晶体管处于放大状态的条件是什么

芯片晶体管的深度和宽度有关系吗

PNP晶体管符号和结构 晶体管测试仪电路图

什么是达林顿晶体管?达林顿晶体管的基本电路

芯片7纳米制程指的是晶体管间距还是晶体管大小7纳米

芯片7纳米制程指的是晶体管间距还是晶体管大小7纳米

评论