全加器逻辑表达式

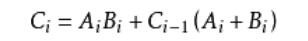

一位全加器的表达式如下:

Si=Ai⊕Bi⊕Ci-1

第二个表达式也可来用一个异或门来代替或门对其中两个输入信号进行求和:

其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci。一位全加器可以处理低位进位,并输出本位加自法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

全加器的逻辑功能

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数![]() 和

和![]() ,还有一个来自前面低位送来的进位数

,还有一个来自前面低位送来的进位数![]() .这三个数相加,得出本位和数(全加和数)

.这三个数相加,得出本位和数(全加和数)![]() 和进位数

和进位数![]() .这种就是“全加“,下表为全加器的逻辑状态表。

.这种就是“全加“,下表为全加器的逻辑状态表。

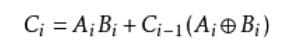

全加器可用两个半加器和一个“或“门组成。

如上图(a)所示。![]() 和

和![]() 在第一个半加器中相加,得出的结果再和

在第一个半加器中相加,得出的结果再和![]() 在第二个半加器中相加,即得出全加和

在第二个半加器中相加,即得出全加和![]() 。两个半加器的进位数通过”或“门输出作为本位的进位数

。两个半加器的进位数通过”或“门输出作为本位的进位数![]() 。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

全加器

+关注

关注

10文章

62浏览量

29149

发布评论请先 登录

相关推荐

热点推荐

高速CMOS逻辑4位二进制全加器CDx4HC283和CDx4HCT283的技术解析

高速CMOS逻辑4位二进制全加器CDx4HC283和CDx4HCT283的技术解析 今天来深入探讨一下德州仪器(TI)的CD54HC283、CD74HC283、CD54HCT283

探索MC14008B 4位全加器:特性、参数与应用

探索MC14008B 4位全加器:特性、参数与应用 在电子设计的世界里,加法器是构建数字电路的基础组件之一。今天,我们就来深入了解一款经典的4位全加器——MC14008B。 文件下载

深入解析MC14008B 4 - 位全加器:性能与应用

全加器,具备快速的内部先行进位输出功能,适用于二进制加法和其他算术应用场景。其快速并行进位输出位使得在与系统

CDx4HC283和CDx4HCT283:高速CMOS逻辑4位二进制全加器的详细解析

CDx4HC283和CDx4HCT283:高速CMOS逻辑4位二进制全加器的详细解析 在电子设计领域,加法器是数字电路中最基本的运算单元之一,用于实现二进制数的加法运算。今天要给大家介绍

高速CMOS逻辑4位二进制全加器CDx4HC283与CDx4HCT283的深度解析

高速CMOS逻辑4位二进制全加器CDx4HC283与CDx4HCT283的深度解析 在电子设计领域,逻辑器件是构建复杂电路系统的基石。今天,我们将深入探讨德州仪器(TI)的CD54HC283

德州仪器 4 位二进制全加器:满足多样化需求的理想选择

: SN74S283N.pdf 卓越特性助力设计升级 高速进位前瞻 这些全加器的一大亮点就是拥有快速进位功能,实现了 4 位的全进位前瞻

高速CMOS逻辑4位二进制全加器CDx4HC283和CDx4HCT283技术详解

高速CMOS逻辑4位二进制全加器CDx4HC283和CDx4HCT283技术详解 在电子设计领域,加法器是实现数字运算的基础元件之一。今天我们要深入探讨的是TI公司的CD54HC283

布尔表达式及范围检查

一个常用的布尔表达式是用于判断变量是否位于某个范围内,

例如,检查一个图形坐标是否位于一个窗口内:

bool PointInRectangelArea (Point p, Rectangle

发表于 12-12 07:08

关于E203内核高性能乘法器优化(三)

4:2压缩器优化

一般的4:2压缩器是由两级3:2压缩器串接起来的,而3:2压缩器的实质就是全加器,其结构如下:

表达式如下:

代码实现:

module full_adder( input a

发表于 10-23 07:43

labview如何使用VISA串口资源查找的正则表达式提取串口的资源名称?

如图,如何利用VISA资源查找的正则表达式从很多串口当中提取想要的目标串口(Quectel USB AT Port这个串口)?

发表于 07-07 17:20

Cubeide1.18.1在线调试改变\"现场表达式\"中的值提示找不到地址,为什么?

Cubeide1.18.1在线调试时,在\"现场表达式\"中添加全局变量,然后改变其数值,Console窗口提示:

Failed to read all registers

发表于 06-12 06:50

干货分享 | 零基础上手!TSMaster图形信号表达式实操指南

TSMaster软件支持在图形里面的信号表达式功能,主要用于多信号表达式运算和显示的场景。本文将以A2L中的标定变量为例,介绍如何使用图形中的信号表达式

Cubeide1.18.1在线调试改变\"现场表达式\"中的值提示找不到地址,怎么解决?

Cubeide1.18.1在线调试时,在\"现场表达式\"中添加全局变量,然后改变其数值,Console窗口提示:

Failed to read all registers

发表于 06-06 08:27

Cubeide1.18.1在线调试改变\"现场表达式\"中的值提示找不到地址怎么解决?

Cubeide1.18.1在线调试时,在\"现场表达式\"中添加全局变量,然后改变其数值,Console窗口提示:

Failed to read all registers

发表于 04-27 06:18

全加器逻辑表达式_全加器的逻辑功能

全加器逻辑表达式_全加器的逻辑功能

评论