全加器的定义

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

全加器逻辑图原理

两个多位二进制数相加时,除了最低位以外,其他每一位相加时都需要考虑低位的进位,即将加数、被加数和低位的进位3个数相加,这种加法运算称为全加运算,实现全加运算的电路叫做全加器。

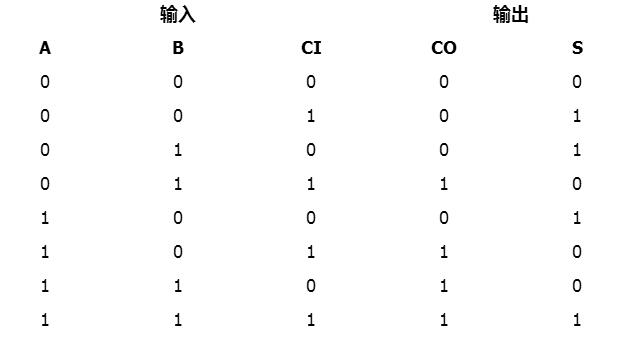

全加器的真值表如表1所示。A、B、CI分别为加数、被加数和低位的进位,S为本位和输出,CO为向相邻高位的进位输出。

表1 全加器真值表

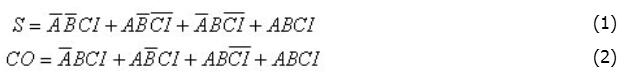

根据真值表写出输出逻辑函数式:

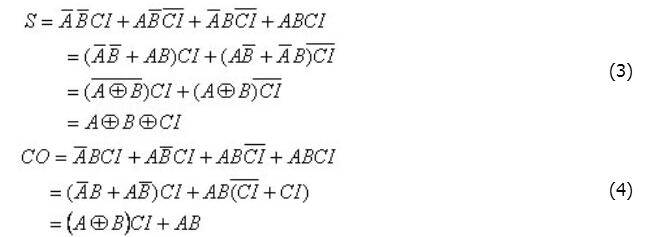

将函数式进行化简和转换

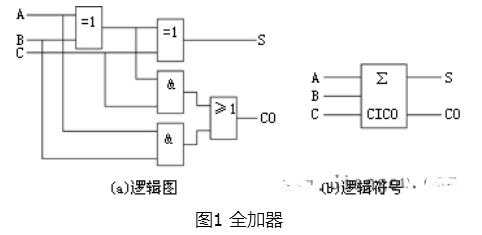

画出全加器的逻辑图,如图1所示。

全加器的输入端有几个

全加器的输入端有三个,分别为A、B、C(低位的进位);两个输出S(和);C(运算产生的进位)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

全加器

+关注

关注

10文章

62浏览量

28496

发布评论请先 登录

相关推荐

半加器和全加器的区别是什么

半加器(Half Adder)和全加器(Full Adder)是数字电路中的基本组件,用于执行二进制加法运算。它们的主要区别在于功能和输入输出的数量。 1. 功能差异 半加器 : 半加器只能处理两个

半加器和全加器的功能特点

的加法运算。半加器的设计目的是计算两个输入位的和,但不包括进位。半加器有两个输入端(A和B)和一个输出端(和S),以及一个进位输出

差分放大电路同相输入和反相输入怎么看

差分放大电路是一种具有高输入阻抗、高增益和高抗干扰能力的放大电路,广泛应用于模拟信号处理领域。差分放大电路的输入端有两个,分别是同相输入

如何判断同相输入端和反相输入端

和两个输入端口,即同相输入端(Non-inverting Input)和反相输入端(Inverting Input)。正确区分和判断这两个

与非门的闲置输入端如何处理

在数字电路设计中,与非门(NAND gate)是一种基本的逻辑门,它具有两个或多个输入端和一个输出端。当所有输入端都为高电平时,输出

比较器输入端和输出端的关系

比较器是一种电子设备,用于比较两个电压或电流信号的大小。比较器的输入端和输出端之间的关系是其核心功能之一。 比较器的基本原理 比较器是一种模拟电路,其基本原理是将两个输入信号进行比较,

差分放大电路单端输入和双端输入的区别

差分放大电路是一种常见的模拟电路,广泛应用于信号放大、滤波、比较等场合。差分放大电路根据输入方式的不同,可以分为单端输入和双端输入两种形式。

具有快速进位的高速CMOS逻辑 4位二进制全加器CDx4HC283和CDx4HCT283数据表

电子发烧友网站提供《具有快速进位的高速CMOS逻辑 4位二进制全加器CDx4HC283和CDx4HCT283数据表.pdf》资料免费下载

发表于 04-28 11:01

•0次下载

ttl门多余的输入端如何处理 ttl多余的输入端可以悬空吗

ttl门多余的输入端如何处理 ttl多余的输入端可以悬空吗 TTL门是一种常见的数字逻辑门。TTL门通常具有多个输入

ttl和cmos多余输入端如何处理

对于CMOS电路而言,多余的输入端是不会影响电路的运行的,因为CMOS电路使用的是恒定电流源和MOSFET器件,不存在浮置输入问题。

全加器的逻辑表达式怎么推

全加器是计算机中常用的一种逻辑电路,用于实现二进制加法运算。全加器接受两个输入位和一个进位位,并输出一个和位和一个进位位。它的逻辑表达式可以通过推导和分析得出。 首先,让我们回顾一下二进制加法的规则

全加器的定义_全加器的输入端有几个

全加器的定义_全加器的输入端有几个

评论