(文章来源:EEWORLD)

当芯片制程低于7nm时,半导体的基本元件之一互连线正在发生根本性的变化。一些最明显的变化发生在最低的金属层。随着又多又小的晶体管被封装到一个芯片上,越来越多的数据被处理并在芯片上、或芯片之间移动,用于制造这些互连的材料、结构本身以及利用这些结构的整个方法都在改变。

在最基本的层次上,所面临的挑战是确保不同层之间的良好连接。问题在于,自130纳米以来一直被用于互连线的铜在很大程度上已经失去了动力。因此,在10nm制程时,英特尔做出了一个转变。本地互连层——M0和M1——与以前的技术一样,包含了钴,而不是铜,其余的层使用传统的铜金属。其他人也正在探索这个想法。

一般来说,铜仍然用于其他和传统的后端(BEOL)层。钴主要用于在这里的衬底,虽然钌也获得了重视。其他材料也在探索中,还有一种新技术叫做埋入式电源轨(buried power rails)。

这比听起来要复杂得多。铜的问题之一是,在最先进的节点它可以扩散到周围的材料。这需要一个阻挡层,但是随着缩放继续到5nm和3nm,这些阻挡层需要更薄,同时也需要导电。这些阻挡层大多是共形的人造材料,即使让它们具有足够的一致性也会产生问题。

布鲁尔科学公司的技术研究员James Lamb:“如果你试图在1纳米或2纳米处放置一个阻挡层,因此要使薄膜可靠,它必须非常一致。”任何微小的错误都会造成巨大的影响。如果这个势垒是1纳米厚,而你在一个点上少了几个原子,那它就不再是势垒了。这被推到了近乎完美的地步。在纳米尺度的最极端,你必须要有一层没有空隙或孔洞的薄膜。”

在制造业中引进任何新材料都是一个缓慢的过程。代工厂对他们的流程是很保守的。但随着价格的上涨,以及芯片在汽车AI等安全关键应用程序或超大规模数据中心内关键任务应用程序中使用间的延长,每一个新节点上的保守性都在增长。淘汰掉衬层(liner,又称包覆层)可以节省整个工艺步骤,但也会对整体设计产生影响,并可能对这些非常昂贵的芯片的整体可靠性产生影响。

Brozek:“衬层和障碍层通常阻力很大。“每个人都在寻找一种不需要衬层的新材料,而这正是驱动钴和钌等新材料的动力。”对于钴,你仍然需要一个成核层和一个衬层。对于钌,你可以尝试做无障碍,或衬里是溅射接触层可以对钌进行培养。没有衬层也可以培养钌。钌比铜更具有电阻性,但如果你考虑到你不需要屏蔽金属,这实际上是更好的。然而,可靠性还没有得到证实。目前还不清楚它在所有布局配置中的表现。用金属填充直线更简单。你可以说你所有的线条都是笔直完美的。你能负担得起锯齿形和双向图案,然后用金属填充吗?

CMP也会有同样的表现吗?所有这些都需要调查。一些失效模式只出现在大规模生产中,你可以观察到工具的可靠性和更差的弯角,以及其他有趣的事情。在生产过程中,以及芯片加工后,如何对其进行测试,是晶圆厂正在努力争取的一项任务。”这也增加了设计的总成本,并不是所有在最先进的节点上工作的公司都认为这是必要的开支。

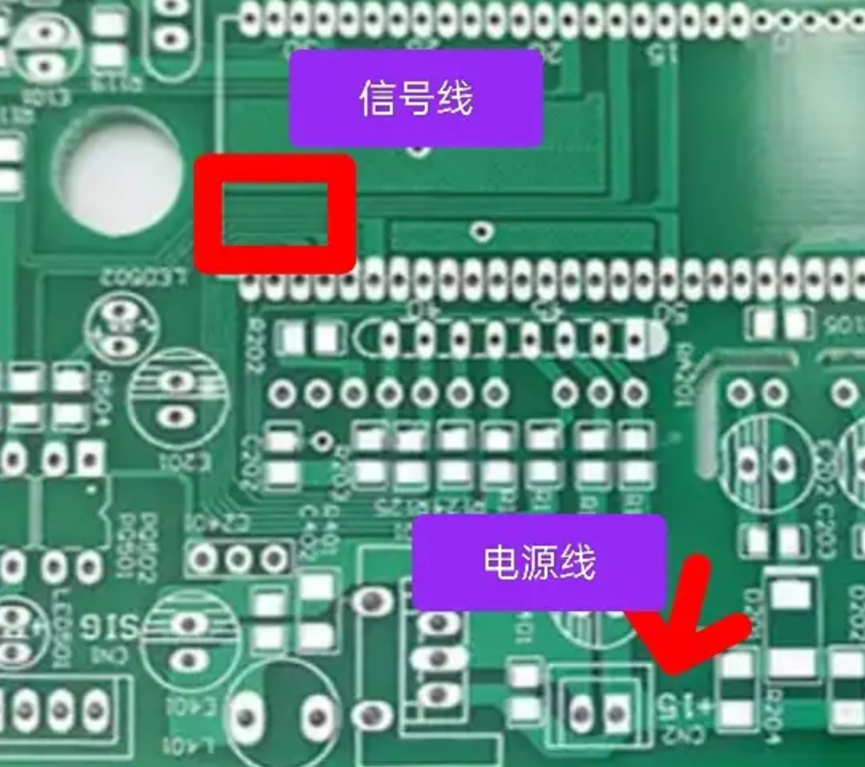

众所周知,晶体管可以放大,但电线却不能,这就是为什么对于某些重要的功能而言,较粗的电线并不罕见。但在最先进的节点,已没有空间容纳更粗的电线。这会导致更高的电阻,更多的热量,增加IR下降。根据Boullart的说法,埋入式电源线将整个过程从中线移至线的前端,从而降低了轨道的高度。

Imec表示,将展弦比高达7且临界尺寸为18nm的钌线作为动力轨,在氧化过程中从FEOL处分离出来,而不是metal 1 layer。达到低电阻率(8.8µohms /厘米)。针对3 nm的设计,研究机构会使用通过减金属蚀刻(subtractive metal etch)的12nm钌线,它的长宽比为3.8和低于500欧姆/µm的线路电阻。

这可能会对性能和密度产生重大影响。实际上,这种方法就像在晶体管下面挖隧道。正如Arm发现,在与Imec一起进行本项目工作时,背面供电的埋入式钌电力轨的IR降比正面供电的埋入式电力轨高7倍。

然而,也有一些意外。Arm的首席研究工程师Brian Cline表示,使用tap cells连接到鳍上,最终可能成为其他设备的障碍。“我们还发现,用来开发这些设备的设计工具会以奇怪的方式失效,特别是,这些工具无法识别metal0以下的电力轨道。”

(责任编辑:fqj)

-

芯片

+关注

关注

456文章

50948浏览量

424715 -

半导体

+关注

关注

334文章

27517浏览量

219768

发布评论请先 登录

相关推荐

说一说半导体微型互联世界里的大变化

说一说半导体微型互联世界里的大变化

评论