相信没有人不认识华为的,那么华为作为全球第一大通信设备商,你知道华为的基站是怎么设计出来的吗?它都用了哪些芯片?PCB电路设计结构如何?带着一堆问题,我们拆解了华为RRU3908,一个户外无线基站,它的每个射频前端输出功率为20/40瓦。

该基站的双工器似乎是虹膜耦合腔滤波器,与一些腔间耦合。输入和输出的耦合是T,是谐振器上的一个连接部分,而不是耦合回路。频率由电容帽调节。滤波器是宽信号的带通。

如果能看到该过滤器的响应速度,那就更好了。

中央处理单元

网络通信由飞思卡尔MPC8321 PowerQUICC2 CPU处理,CPU运行在200 MHz,拥有2x 256 MB Hynix DDR2 RAM。它使用一个PMC QuadPHY 10gb控制器用于两个光学输入/输出。

ADC和DAC单比特流的解码和编码由3 Altera Cyclone III FPGA和定制的华为SD6151RBI控制器处理。

该华为基站采用德州仪器TMS320系列DSP处理器对单比特流进行处理。TMS320C6410是一个只计算整数的定点DSP, TMS320CT16482 1 GHz DSP CPU计算浮点数。

信号接收部分

输入信号来自两条失相线,首先由Skyworks SKY73021-11 1.7 - 2.2 GHz下变频混频器处理,得到2.2 GHz到550 MHz的频率。

一个SIPAT锯过滤器用于隔离。

根据信号来源或类型的不同,假设在信号线分成3G ADC线或4G ADC线之前使用的是模拟设备AD8376可变增益放大器。

3G线路模拟到数字转换由模拟设备AD6655-10处理,这是一个14位150 MSPS芯片,专门针对3G基站。

4G线有一些组件如有双向HSWA + 1110领域射频开关,为双通道MAX2039E / dowoconversion混合器和通过一个额外的恢复期HSWA + 1110领域射频开关是由模拟装置ad9230 - 11 - 200 ADC芯片数200个。

所有的定时都是由模拟设备AD9516-3处理,这是一个14输出时钟发生器与内置在2 GHz本地振荡器。

信号传输部分

Altera Cyclone III FPGA的单比特数据流由2个模拟设备TxDAC AD9788处理,TxDAC AD9788指定用于16位800 MSPS。

为了使信号的频率上升到广播载波频率,使用了2个模拟装置ADL5375-05上变频调制器。它们的范围从400mhz到6ghz。

然后信号通过5级陶瓷谐振器带通滤波器发送。

信号相位可以从晶体管和EMC技术的设置和佛罗里达RF实验室HPJ2F混合耦合器切换。

信号发送到功放前的前置放大器为飞思卡尔MMG3004NT1高线性放大器,可在400mhz ~ 2.2 GHz范围内放大17 dB。

为了控制信号强度,MCL 31R5数字步进衰减器位于输出连接器前。这是一个31.5 dB衰减器,可以在0.5 dB的步骤从一个6位串行控制接口。

功率放大器采用两个阶段,第一个阶段是英飞凌PTMA180402FL 40瓦射频LDMOS,通过Xinger II XC1900A-03S混合耦合器,将两个90度非相位信号馈送给输出级晶体管NXP BLF6G20LS-140 140瓦射频LDMOS。

输出在Xinger II XC1900A-03S混合耦合器中重新组合,然后通过循环器进入双工器。

-

芯片

+关注

关注

456文章

51127浏览量

426110 -

华为

+关注

关注

216文章

34526浏览量

252555 -

基站

+关注

关注

17文章

1402浏览量

66878

原文标题:华为基站拆解曝光:PCB设计+高频走线,完美的像艺术品!

文章出处:【微信号:EngicoolArabic,微信公众号:电子工程技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

华为支付接入规范

华为连续九年领跑全球基站天线市场

华为连续九年蝉联全球基站天线市场份额第一

你知道吗?这四种关机重启情况,有更好解决办法

关于定位系统技术你知道多少?

如果你要填报电子专业,这些问题最好提前知道(附院校排名名单)

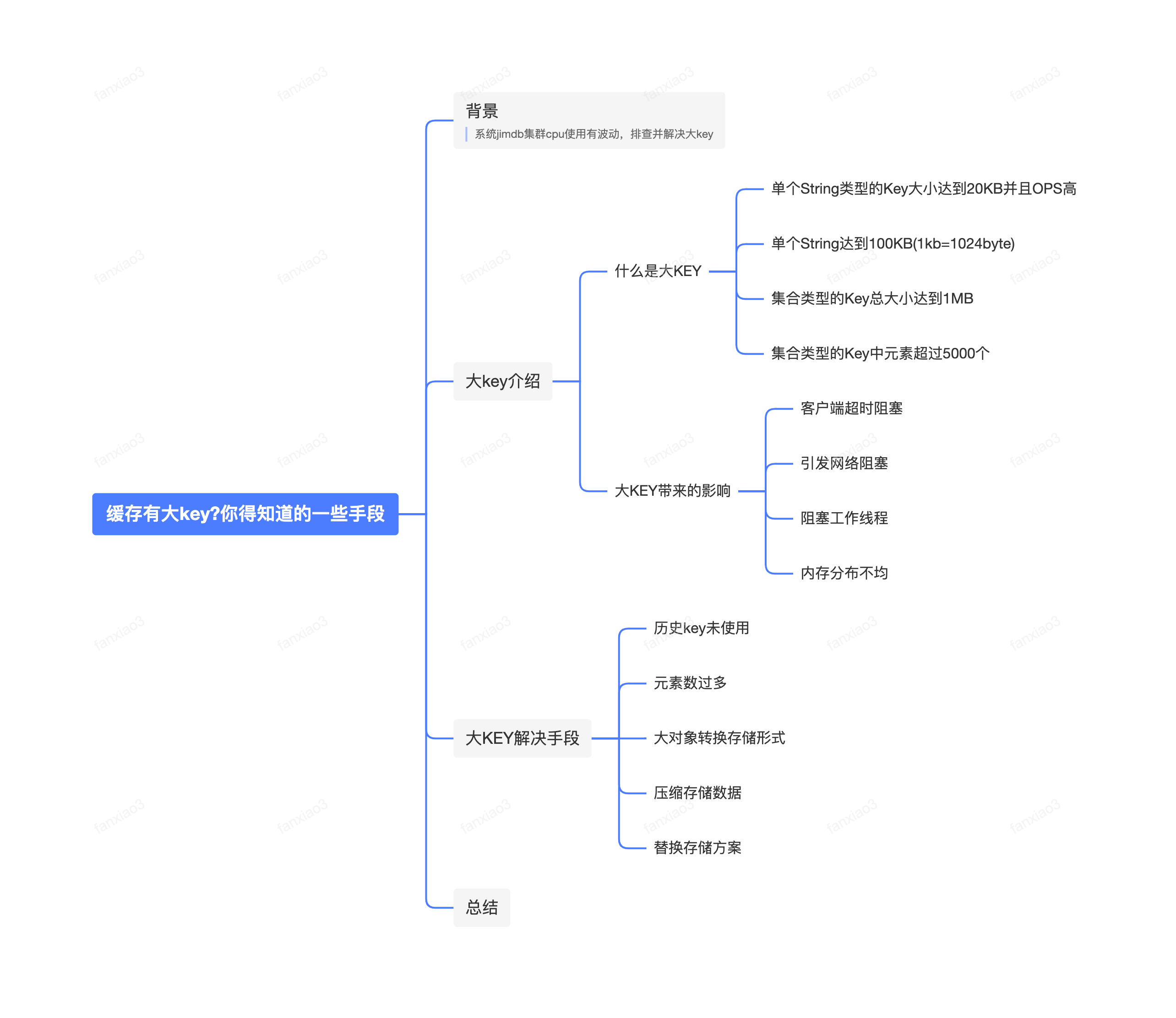

缓存有大key?你得知道的一些手段

电容6大特性参数,你知道几个?

你知道华为的基站是怎么设计出来的吗?

你知道华为的基站是怎么设计出来的吗?

评论