今天我们来学习一下Innovus中分析clock tree的小工具——CCOPT Clock Tree Debugger,简称CTD 看这名字就知道,这工具是用来Debug clock tree。大家知道,CTS在PR流程中,占据着极其重要的地位,tree build好以后,你的design就完成了一半。通常这是一个需要反复尝试的过程,我们需要根据clock tree现在的状况,去调整各个参数。如果能有一个图形化的工具帮助我们更加形象直观地观察到整个clock tree的状况,那对我们的Debug是非常有帮助的。而这次要介绍的Clock Tree Debugger就是起到这个作用。 话不多说,切入正题,我们可以通过打开GUI上Clock下面的CCOPT Clock Tree Debugger来打开它,

或者输入命令ctd_win,

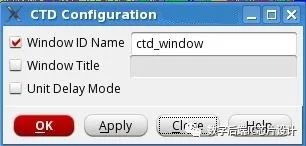

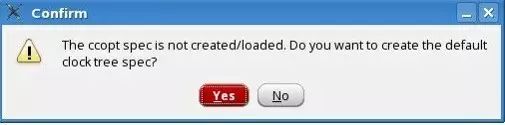

Window ID Name代表内部CTD的窗口标记,只是一个记号,CTD默认可以打开六个窗口,大概是起到防止重复的作用吧。Window Title则可以显性地指定CTD窗口的显示名字。Unit Delay Mode在后文会提到。 使用CTD之前,我们必须首先创建clock tree的spec,如果没有创建,CTD会弹出一个warning窗口

进入到CTD的主界面窗口,整个工具可以分为7个部分:MenuBar(菜单栏),ToolBar(工具栏),Key Panel(按键板),Control Panel(控制板),Browser(浏览器),Clock Tree Viewer(时钟树视角),World Viewer(全局视角),下面我们来分别学习一下这每个部分的作用。

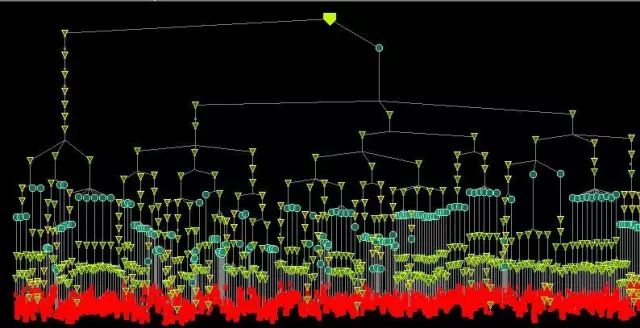

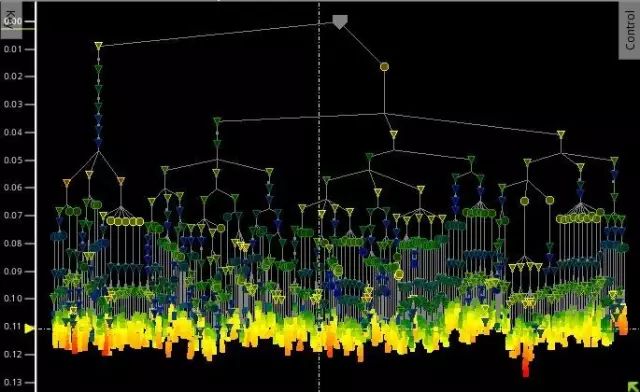

Clock Tree Viewer

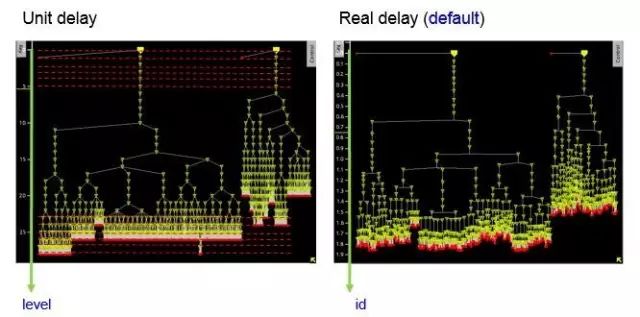

首先来看Clock Tree Viewer, 这是最主要的部分,显示了Clock Tree的结构。在CTD中,Clock tree以倒Y字形结构不断地往下分叉,直到trace到clock sink端为止。结构显示也分为两种模式。Unit Delay和Real Delay,可以在菜单栏Visibility中选择切换。如下图所示:

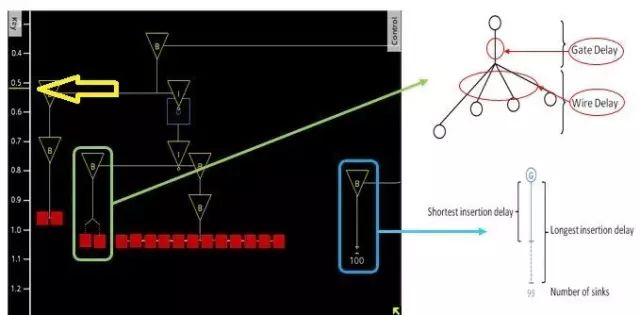

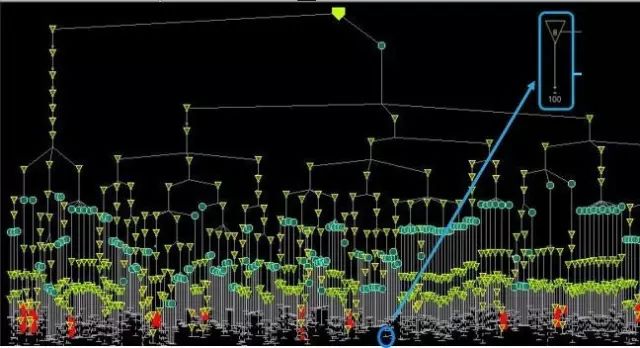

Unit Delay按照clock tree中的level划分排列,左边的纵坐标显示clock tree上所有cell的级数,同一个level的clock cell处在同一水平线上。Unit Delay只能从层级上简单地反应整个tree的结构,并不能按照真实的clock tree的指标参数显示。 Real Delay按照clock tree的实际insertion delay来显示clock tree的信息,这是默认的显示设置,相对而言更加真实,左边的纵坐标显示着clock tree上cell的insertion delay信息。因此path的长短不一,也让我们可以很直观地观察出整个tree的skew情况。 我们来看具体insertion delay是如何计算显示的。前面说过,整个tree以倒Y字形向下分叉,下左图中,看似平整的直线其实放大了看也是有斜度的。那一段Y字形分别代表着Gate Delay和Wire Delay,如下右图红圈所示。鼠标移至对应的clock cell,左边纵坐标轴上就会显示对应的insertion delay数值,如下图黄色箭头所示,如果你想在CTD上查询具体的Gate Delay和Wire Delay,暂时我们没有直接显示的方式,只能通过Ruler工具去纵坐标上量取对应的值。 我们也可以选中clock buffer, 右键将sink collapse起来,这样,所有所有clock sink便会以数字的形式简单显示在CTD上,当然它会将最长和最短的path以实虚线的形式分隔开来,如右下图蓝圈所示:

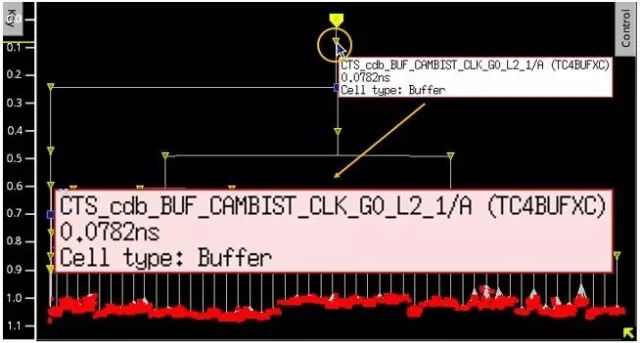

如果鼠标长时间停留在某个clock cell上,CTD就会自动弹出一个小窗口,显示该clock cell的名字以及insertion delay等数值

Menu Bar

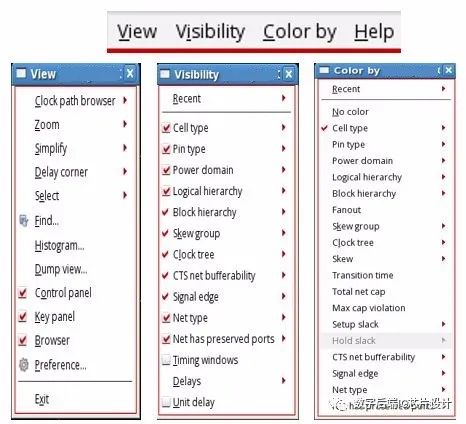

Menu Bar(菜单栏):CTD上菜单栏并不多,一共有4列,Help选项就不介绍了

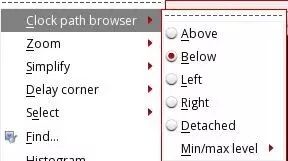

先看View菜单,它主要控制CTD上整个界面上的显示要素 (1)Clock path browser:主要控制Clock path browser的显示位置,默认在显示在主界面下方,Clock path browser的功能后面会介绍到

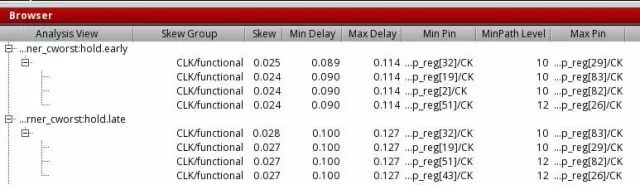

Min/Max level代表着显示到Clock path browser中的多少个skew group的数值信息,默认只显示Skew最大的skew group,level越大,可以显示的skew group也越多,如下图所示:

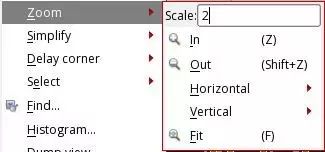

(2)Zoom:就是平常使用放大缩小功能,不过多介绍了

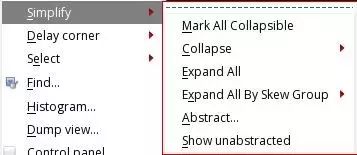

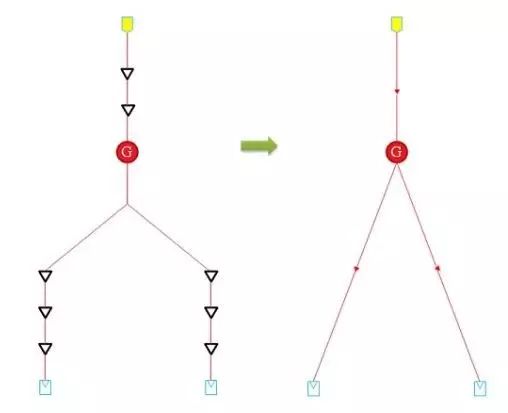

(3)Simplify:该功能可以将clock tree的显示简单化,将一些不想看的东西用缩略图表示。

Collapse可以将Sink,ICG,Buffer等cell不展开显示,只以一个简单数字和虚线表示连接关系,下图蓝圈表示该buffer驱动了100个clock sink

Expand就起相反作用,将前面收缩显示的东西又全部展开

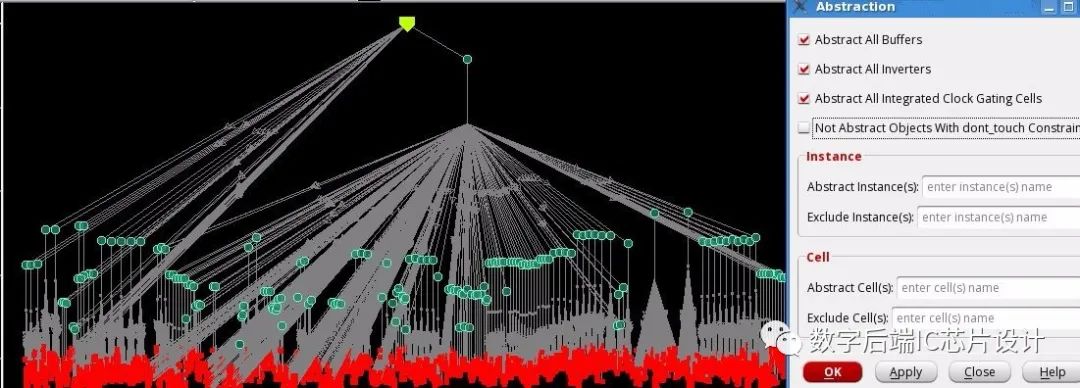

Abstract则是一种各简单抽象的显示图了,它放弃了倒Y字形的叉状显示图,而是直接采用类似飞线的连接方式,在这种情况下,它并不关注clock tree上insertion delay了。

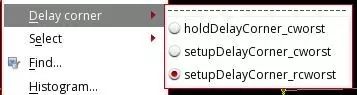

(4)Delay corner:该选项很简单,就是切换不同的corner下面,tree的显示情况。可以按快捷键"d"切换至下一corner,按“D”则是切回defalut的corner。需要注意的是CCOPT默认只工作在你的primary corner下面

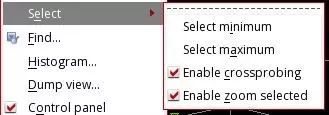

(5)Select: 该功能能实现一些特殊的“选择”功能

Select minimum和Select Maximum:分别可以选择当前control菜单下,最小和最大的sink,比如我选择了Transition time的control界面,那么点击Select Minimum或Select Maximum,工具就会自动地帮我们选中最小或者最大的transition sink。如下图中的黄色虚线所示:

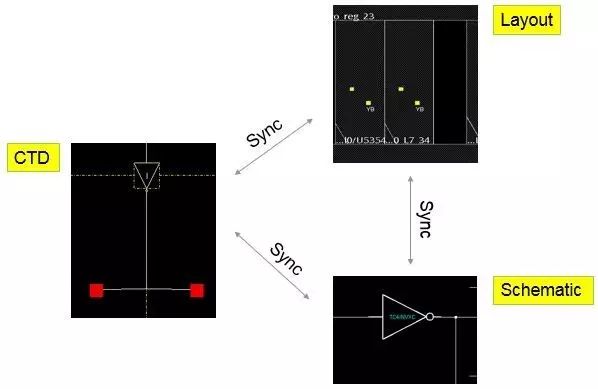

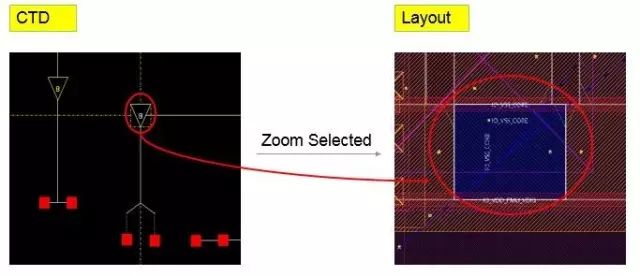

Enable crossprobing: crossprobing是一个非常好用的功能,从名字就能知道,它起着交叉显示的作用。它很好地同步了CTD,innovus layout和Schematic view三个显示界面。在CTD上执行Selection,Highlight等操作,会自动在Layout和Schematic view上同步执行相同的操作,我们看下面三张图: CTD上选中一个buffer,Innovus layout界面和schematic view界面上也会选中该buffer

CTD上Highlight这个选中的buffer,Innovus layout界面和schematic view界面上也会Highlight该buffer

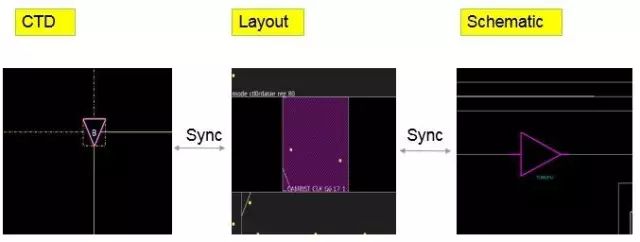

Enable Zoom Selected:打开该功能的话,在CTD上选中某个Object后,Innovus layout界面会自动放大该Object.

(6)Find窗口就是平时经常使用的搜索Object界面 【图形界面介绍

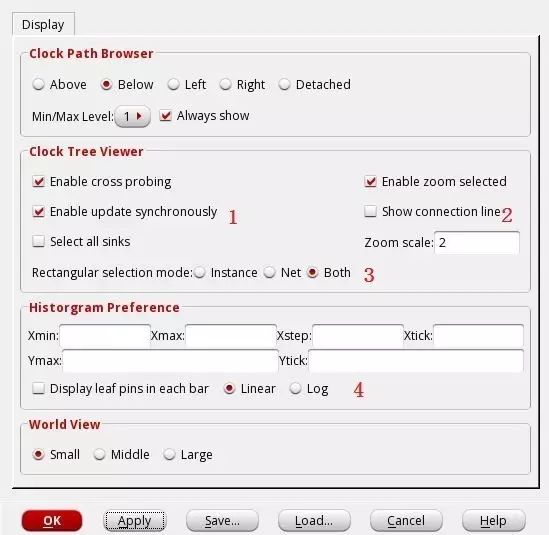

(8)Dump view:可以讲当前的clocktree截图下来,这个很简单就可以理解 (9)Control panel,Key panel,Browser则分别可以控制三个面板的显示与否。后面会分别介绍这三个面板 (10)Preference: 设置选项,大部分前面都介绍过。

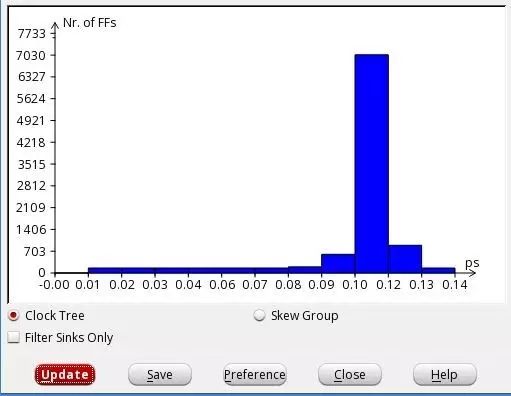

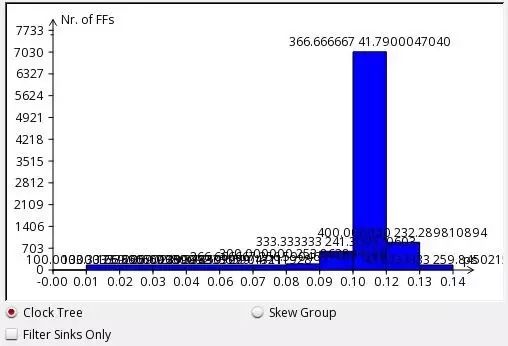

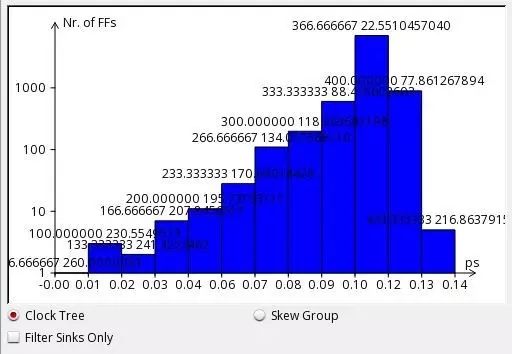

Enable update synchronously:当你对clock tree上的net或者cell做eco时,clock tree viewer上会直接更新。Show connection line:打开后可以显示飞线Rectangular selection mode:在clock tree上框选一块区域时,指定在layout view上应该显示instance或者netDisplay leaf pins in each bar:在柱状图中显示每个柱条的实际数值,Linear是代表Y轴显示数字线性增长,Log是代表Y轴显示数字指数增长。Linear:

Log:

-

CTD

+关注

关注

1文章

3浏览量

2597

原文标题:心似双丝网,中有千千结——Clock Tree Debugger(一)

文章出处:【微信号:IC_Physical_Design,微信公众号:数字后端IC芯片设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

图片转PCB图的小工具

介绍一下STM32L151的clock tree

什么是Clock Tree

Linux Device Tree的基本概念

分析clock tree的小工具——CCOPT Clock Tree Debugger(二)

分析clock tree的小工具——CCOPT Clock Tree Debugger(一)

分析clock tree的小工具——CCOPT Clock Tree Debugger(一)

评论