电子系统需要实施隔离,它的作用是保护人员和设备不受高电压的影响,或者仅仅是消除PCB上不需要的接地回路。在各种各样的应用中,包括工厂和工业自动化、医疗设备、通信和消费类产品,它都是一个基本设计元素。 近日,ADI接口与隔离产品中国区业务拓展专家陈捷先生做客ADI智库在线课程直播,从隔离技术的前景展望看集成电路发展到 EMI 挑战及目前主要解决方法延展至ADI新一代具有低辐射发射的isoPower的产品综述。

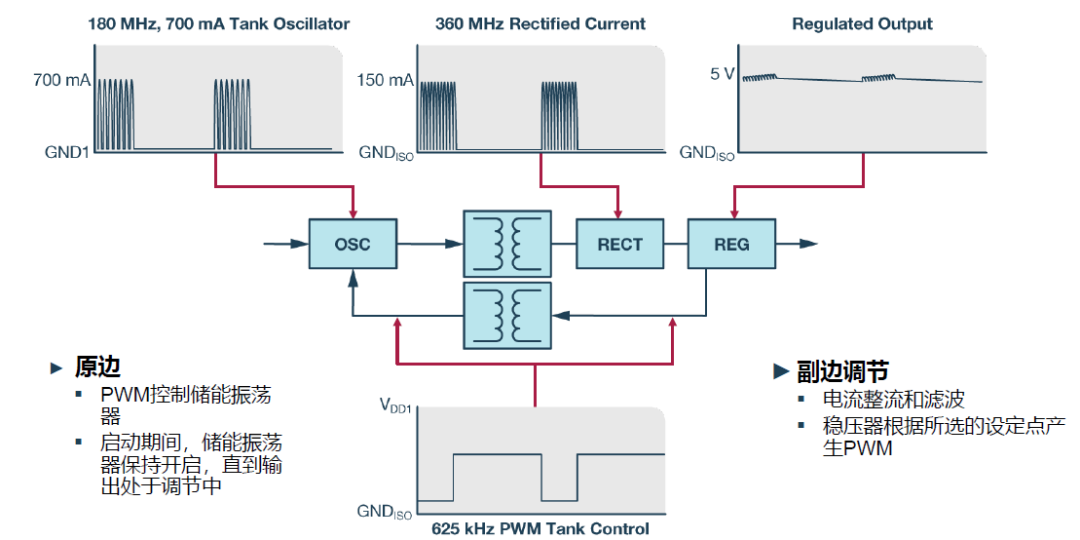

全面考虑产品设计的EMC挑战 众所知周,芯片级隔离电源的进步可以大大降低设计的复杂性,减少元路件数量,同时通过多个隔离电源实现空间受限应用。辐射发射一直是一个挑战,使用50MHz至200MHz的频率来减小变压器尺寸会带来辐射的增加:

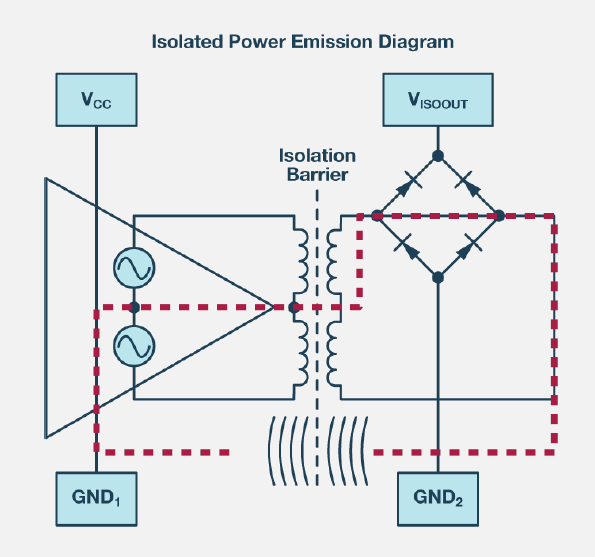

无返回途径:这些电流不能穿过隔离栅,没有返回的物理途径,会形成偶极天线,进而产生辐射

环路面积:VISOOUT和GND2引脚连接到平面会增加环路面积和辐射

拼接电容:为减少偶极辐射,需要为高频共模电流提供一个低阻抗返回路径

挑战:辐射发射增加

产品上市前,必须符合EMC规定。将变压器和所需的电路集成到更小的封装中会产生EMI,因此需要采用复杂且成本高昂的RE抑制技术,以满足电磁兼容性(EMC)法规的要求。据报道,50%的产品首次EMC测试都以失败告终。这可能是因为缺乏相关知识,且未能在产品设计阶段的早期应用EMC设计技术。想要最大限度地缩短设计时间和降低项目成本,在项目开始时就进行EMC设计是至关重要的。组件的选择和放置也很重要。将符合行业标准的器件纳入选择和设计可以提高合规性。

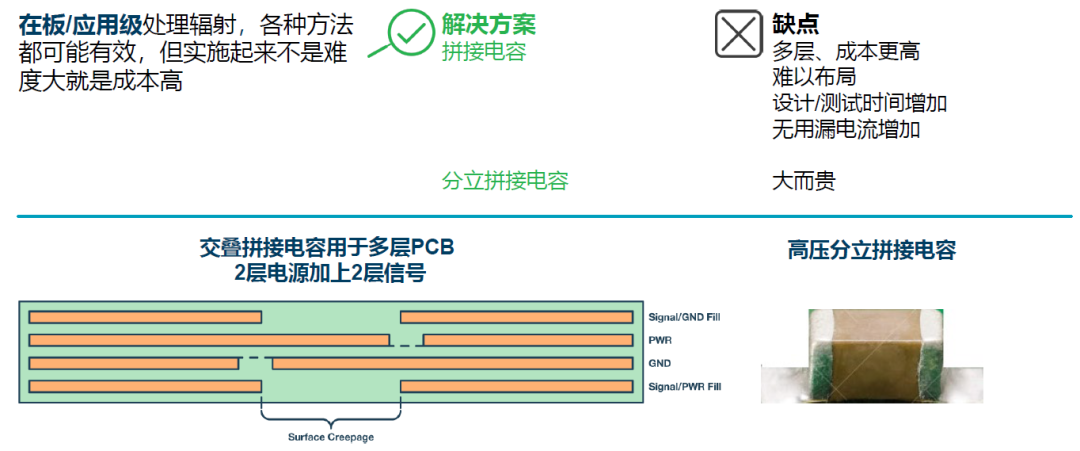

EMC抑制技术亟需更好的方法 与使用分立式变压器的传统方法相比,将变压器和电路集成到芯片级封装中可减少组件数量,进而大大节省PCB空间,但可能会引入更高的辐射发射。辐射发射抑制技术会使PCB的设计更加复杂,或需要额外组件,因此可能会抵消集成变压器所节省的成本和空间。例如,在PCB级别抑制辐射发射的一种常见方法是为CM电流形成一个从次级端至初级端的低阻抗路径,从而降低RE水平。要实现这一点,可以在初级端和次级端之间使用旁路电容。该旁路电容可以是分立式电容,也可以是嵌入式夹层电容。

分立式电容是最简单的解决方案,可能是有引线或表面安装组件。它还具有适用于2层PCB的优点,但分立式电容价格昂贵且体积庞大,会占用宝贵的PCB空间,特别是在可能堆叠了多个组件的隔离栅旁。 另一个不是很理想的解决方案是使用嵌入式旁路电容,当PCB中的两个面重合时就会形成该电容。此类电容具有一些非常有用的特性,原因在于平行板电容的电感极低,因此在更大的频率范围内都有效。它可以提高发射性能,但因为需要自定义层厚来获得正确的电容,且PCB需要四层或更多层,所以设计复杂性和成本都会增高。此外,还必须通过隔离的方式,确保内部重叠层的间距满足相关隔离标准所规定的最低距离标准。 无论是分立式还是嵌入式,使用旁路电容都不是理想的抑制技术。它虽然可以帮助减少辐射发射,却要以增加组件、采用复杂的PCB布局和提高瞬态敏感性为代价。理想的抑制技术不需要采用旁路电容,因此可以降低成本和PCB设计的复杂性。

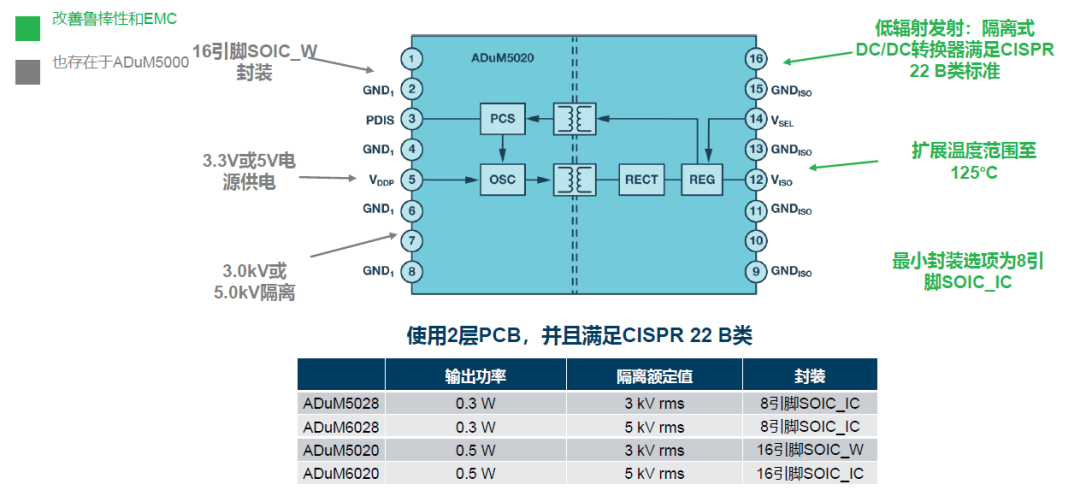

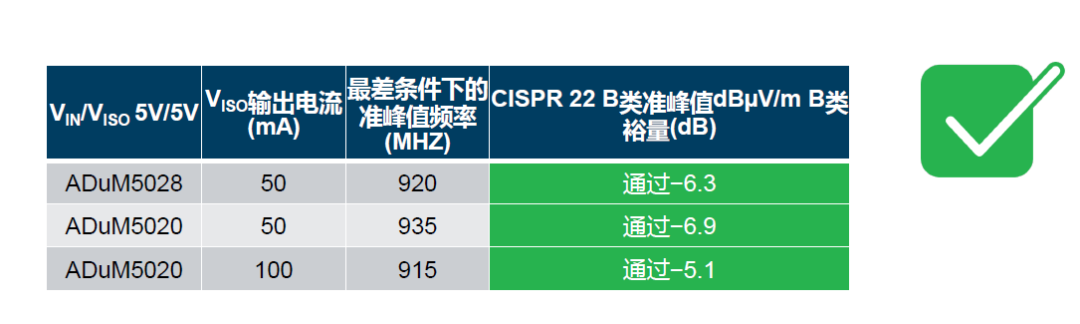

ADI新一代isoPower系列产品 新一代isoPower系列产品采用创新的设计技术,可以避免产生大量辐射发射,甚至在没有旁路电容的2层板上也不例外。ADuM5020和ADuM5028在以大幅裕量满足CISPR22/EN55022B类限制的同时,可以分别跨隔离栅提供500mW和330mW功率。

ADuM5020采用16引脚宽体SOIC封装,而对于ADuM5028,可以选择的最小封装是8引脚SOIC。ADuM5020/ADuM5028提供3V和5V两种电源选项,以及3kV rms额定隔离。 为了减少辐射发射,ADuM5020/ADuM5028具有出色的线圈对称性和线圈驱动电路,有助于将通过隔离栅的CM电流传输最小化。扩频技术也被用来降低某一特定频率的噪声浓度,并将辐射发射能量扩散到更广泛的频段。在次级端使用低价铁氧体磁珠会进一步减少辐射发射。在RE合规测试期间,这些技术可以改善峰值和准峰值测量水平。

-

变压器

+关注

关注

159文章

7328浏览量

134876 -

emc

+关注

关注

169文章

3872浏览量

182862 -

隔离电源

+关注

关注

6文章

278浏览量

36268

原文标题:给您一个方法简化电源隔离设计,轻松满足EMI目标

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何利用具身智能优化产品设计

如何提高产品的EMC性能

EMC的三大规律解读

EMC磁环厂家:电磁干扰的隐形守护者

深圳比创达电子EMC|EMC电磁兼容性:原理实践,电子设备稳定运行.

EMC研发体系建设与技能培训:从经验向流程化设计的转型

全面考虑产品设计的EMC挑战

全面考虑产品设计的EMC挑战

评论