“工欲善其事必先利其器”,做好数模混合验证必须了解EDA工具的工作原理。EDA仿真器是在干两件事情(时间和数值),即在什么样的时间,该出什么样的数值(表现);数字和模拟的差别在要解的方程组是完全不同的。

1.数字仿真器

Event Driven的逻辑方程是顺序和并发执行的,有很清晰的信号流和事件发生顺序,可以同一个时刻多个Event并发执行,但是不会回头计算,所以它快。由于时间和数值都是离散的,所以不容易出现不收敛性的问题。完成代码编程后,应该知道有哪些Event要发生,等待那个时刻的反馈,如果没有其他事情抵消掉(就不发生了),就只和逻辑方程打交道。问题是现实世界(对象是Transistor),并非是非黑即白的0,1世界,所以它的精度会低些;只要做好协议和纠错功能,倒是不会出错的。所以 SOC的顶层,如果用数字仿真器,也是因为它快。

2.模拟仿真器

需要解决模拟大环境、大矩阵( System Matrix),而且要在仿真的每一步都站在全局的角度,看各种需求是否被满足。模拟仿真器考虑的是真实的信号(电压和电流)与系统。KCL、KVL,节点电流为0,回路电压为0,往往用简单逻辑方程理不清楚,必须建立大型的矩阵。任何一个Analog环境里的元素/器件(Element)都直接影响到其他元件,正所谓的“牵一发而动全身”。即使EDA工具可以对Analog电路做分割(Partition),以减小矩阵的规模。

Analog仿真器每往下走一步,都先试一试是否满足Tolerance要求,满足则往下继续;不符合,修改后再试,直到最终各种要求满足;但是想满足所有限制,有时候是比较困难的,所以大规模模拟仿真会经常出现Convergence Issue,即仿真不收敛,这就需要考虑是否需要修改仿真设置与参数,或者考虑电路哪里有薄弱点,再进行反复迭代。由于时间和数值都是连续量且相互影响,所以Analog仿真很慢,但比较精确,故高性能的Analog IC,都离不开Analog仿真器。

SPICE是一个解非线性常微分方程的工具,其快速仿真(Fast Spice,XPS)可以将整个电路分成几个独立的小块单独求解矩阵,然后再把各块联接起来。这样速度比原来Spice快上几十倍,而精度差别在Spice的5%-10%之内。

3.数模混合仿真

当DUT同时包含模拟电路(schematic)和数字电路(RTL)或者模拟模型(Verilog-AMS,SystemVerilog)的时候,仿真会同时使用模拟仿真器和数字仿真器,进行数模混合仿真。模拟电路和Verilog-AMS模型中的Analog Statement部分,会由模拟仿真器进行矩阵计算,有较高的精度。数字电路和模拟模型中的离散部分,则有数字仿真器进行Event-Driven的逻辑方程计算。最终模拟和数字仿真器相互协调完成对DUT的整体仿真。。当信号需要在模拟(连续时间域)和数字(离散时间域)进行穿梭时,则需要通过Connect Module(CM)。对于从数字到模拟的转换,CM定义了信号的具体电特性,例如:阻抗,上升沿下降沿速率,电压钳位等等。对于从模拟到数字的转换,CM决定了量化精度和采样率。由此可见,Connect Module的设置对混合仿真的速度和准确性都有很大的影响。

典型的混合信号交互过程融合了包含迭代算法和后向步长功能的模拟求解器和沿前向计算的数字求解器。这种功能组合定义了模拟的即时方程求解和数字的事件驱动求解,必须在系统的DC工作点和瞬态Trans分析中协同工作。

A、DC 工作点分析

模拟的静态工作点和数字在零时刻的初始化工作。在数模混仿工具上的顺序是:

1)运行所有离散的初始化

2)在零时刻执行所有离散initial模块

3)在零时刻执行所有离散always模块

4)模拟迭代得到所有电压电流结果

B、Trans工作点分析

模拟部分从0时刻工作点计算出发,按时间步长重复计算。模拟仿真器用Spice,由牛顿-拉夫逊迭代技术反复迭代;数字求解逻辑方程。如果他们两个各自运行/没有数据交换,那就在下一个步长重复。一般而言,每次模拟求解器的时间轴先向前移动,数字仿真器在后面跟上,这是因为数字仿真器只能向前,而模拟仿真器允许退回操作(重新计算之前时间点的数值)。因此如果数字在追赶的过程中,有离散数据或者事件变化了,模拟仿真器需要退回到数字改变数据的时间点,重新和数字同步。

总之,无论是DC还是Trans瞬态工作点分析,混合信号的同步过程都可以概括为防止任意一个仿真器计算出另外一个仿真器不能够接受的敏感数据。

Model介绍

“对于先进的数模混合验证而言,行为建模对模拟设计的高级抽象起到了至关重要的作用。”-Alberto Sangiovanni-Vincentelli,美国工程院院士。

基于模型的模拟验证方法,是唯一能够验证复杂模拟设计的验证方法,可以帮助模拟设计工程师进行模拟集成电路设计验证。----Ken Kundert博士,Spectre的发明者。

可见Model是非常重要的。在这里,我们以独特的视角、丰富的设计经验,做数模混合信号里面Model的全面剖析。做Model的目的是什么?Model有哪些级别?与Model相关的概念有哪些?现有EDA工具中有哪些和Model相关的产品?这些都是我们应该关注的。

1.Model的本质目的

Model的本质目的是为了“洞见”(就是明察),清楚的看到、而且提前看到。“明察、清楚”是对“精度”的要求;“提前”是对时间的要求。所以做Model的本质目标就是“时间和精度”。谁在控制“时间”和“精度”?显然是仿真器。所以搞清楚仿真器之后,通常事半功倍。

2.Model的级别

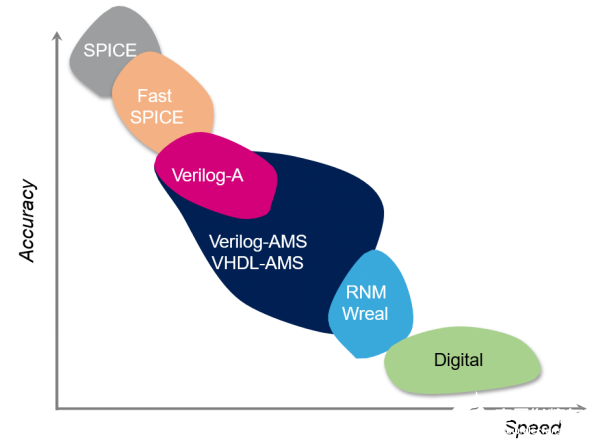

仿真器所需的“时间”和“精度”怎么协调?想快就向Digital仿真器靠拢;想准就向Analog靠拢。做Model不是做加法、就是做减法。做Analog出身的熟悉Schematic,对Schematic的加法得到:Critical Part Model、BA Model;对Schematic的减法得到:VerilogA;VerilogAMS;Real Number Model(RNM);Verilog;Reference Model等。

图1 Model的等级

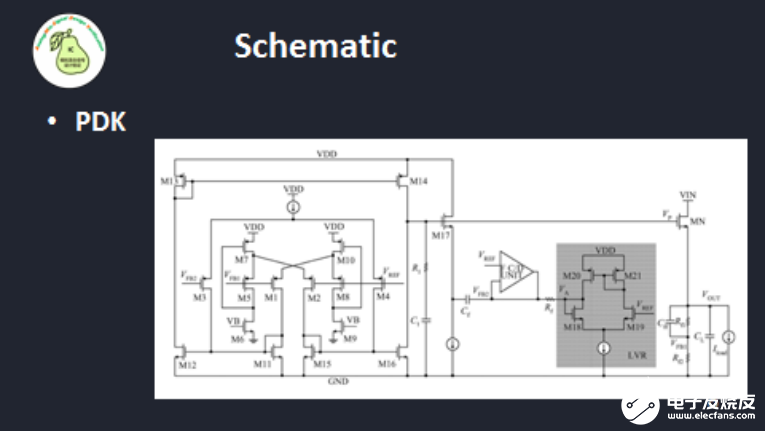

图2 Schematic

工艺给出PDK,用EDA工具直接仿真,这不也是Model嘛!它通过EDA工具把环境和数据设置好,Schematic直接用就行了。所以划分Model等级的时候它可以作为Golden标准。

1) 对schematic的加法

PDK总能cover到我们想要的么?什么情况下Schematic Model做加法呢?

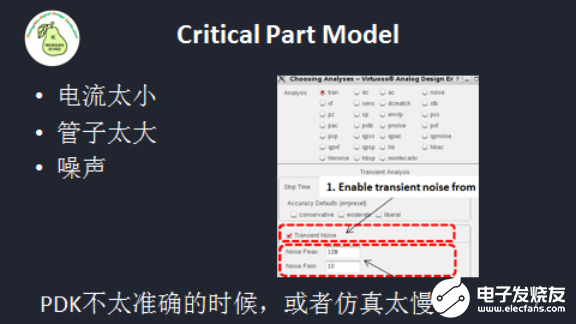

图3 Critical Part Model

A、Critical Part Model

工艺PDK也是一种Model,它是经Fab验证的较精准的Model。PDK上给出常用的范围内的数据是比较准确的,当超出时,例如电流太小时,PDK曲线上的数据)会导致Model和实际的silicon之间不吻合。当Analog要求处理的数据是连续的,即各种大小的电流、尺寸都满足时,对数学表达式的要求就比较复杂,导致仿真器会更慢。当要求低功耗减小电流的时,必须考虑PDK建Model时数据的真实性;而不是表达式外推憶断(extrapolate)的虚假数值而已。相反,对大管子,(powerFET)本身的走线电阻、电容形成的网络,对其Model也要相应调整。

又例如,对于器件的噪声,Cadence的仿真工具有trans noise,ac noise等模型,但trans noise 一开启,仿真时间就上涨了。所以仿真器有Option可以设置某个时间点turn on,还是turn off噪声,来分析电路中关键的、敏感的节点。到那时整体速度还是慢。为了能够快速的得到噪声的影响结果,可以用VerilogA/VerilogAMS去写一个随机变化的噪声源的Model,而不用打开trans noise,就可以得到有noise时候芯片的一个预判。这就是所谓的Critical Part Model。

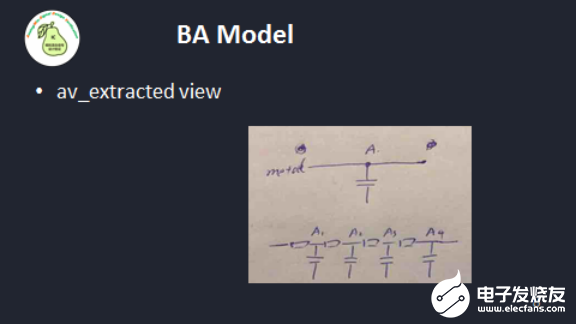

图4 后仿真Model

B、BA Model

Layout后,EDA(LVS,DRC)工具帮你提取R、C和RC等寄生参数,做(av_extracted view)参数提取后仿真(BA sim),不过仿真就更慢了。而Layout都出来了,把一些不重要的block换成schematic甚至Model,这时只关心重要block的性能。如果只提取C,而不提取R的话,这时整个电路的仿真时间并不会增加多少。因为提取R,则大大的增加了求解矩阵的复杂程度,所以仿真时间也长了很多。

对Schematic做加法的目的在于提高精度。这是高性能的模拟IC、模拟IC占很大比重的混合IC所在乎的。如果再加上Thermal Model, Package Model, Board Model, Transmission Line Model 等,就是更精准的实际IC应用环境了。如果关心速度和时间,就需要对所设计的芯片一层层地对Schematic做各种减法。

2)对schematic的减法

显然对Schematic做加法的弊端就在于其速度。如果关心速度,就需要做减法的Model。

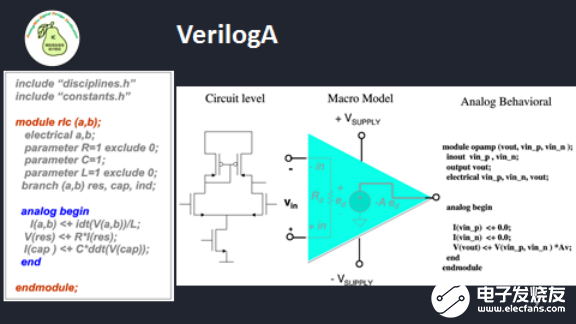

图5 VerilogA Model

A、VerilogA

如果不涉及工艺PDK,VerilogA比Schematic要快。VerilogA Model和VerilogAMS相比,它是纯Analog仿真器,但引入digital时、接口处理不好会导致收敛性问题,缺点还是慢。习惯了Verilog的人,去看纯VerilogA的程序,当Control等信号太多的时候,有时候会觉得VerilogA太啰嗦。

图6 VerilogAMS

B、VerilogAMS

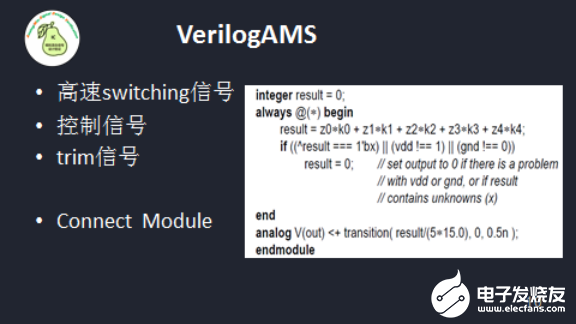

VerilogA还是纯Spice的模拟仿真器,纯模拟仿真器的劣势是矩阵求解要多控制信号。这些控制信号又给Analog仿真器增加了负担,Analog最讨厌高频扰动信号,尤其是方波。所以AMS横空出世,于是高速Switching信号、控制信号、trim信号都Model化。于是像cross,above!,和Analog的transition,timer等关键字,把这A-2-D,D-2-A的事情做了。

为了把Analog和digital仿真器做成Mix-signal的仿真器,需要引入Connect Module,当然它提高了做Model人的经验要求。因为它和仿真器契合度太低,就不可能提高仿真的速度,即使降低了精度要求。有的时候A到D, D到A写不好会相互缠绕和给仿真器带来不收敛问题。

图7 RNM--Wreal

C、Real Number Model(RNM)

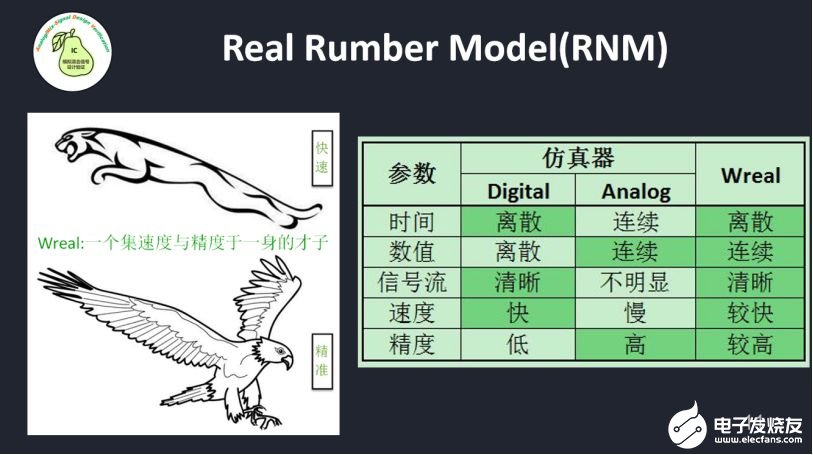

Real Number Model(RNM)是解决混合仿真快和准的手段:用实数来表示电气信号,用离散Solver替代模拟Solver,在更抽象层级上端口间传送的电压/电流信号可以描述为单个实数。在VerilogAMS, System Verilog(SV) 和VHDL中RNM得到支持。

在VAMS中”wreal”的定义就是“A real valued wire”,言简意赅,一个能够做wire,又能连续变化的variable。作用是做model和用来做verification。

仿真器怎么处理一根wreal的线呢?因为wreal在时间上是离散的:它只根据离散的event来变化;故它用digital solver来解决问题。而同时又有Analog的痕迹的(它不是0,1,x,z时是一串串浮点数,和连续变化的模拟信号非常接近的)。用wreal做RNM(下表绿色填充色为优势点),它将Digital和Analog仿真器两者的优点给综合到了一起,并在仿真速度和精度之间取得了折中(Wreal的Analog痕迹保证了精度,它数字化处理的机会保证速度)。还可以把random,coverage、assertion-based verification等概念利用到Analog 信号上,集速度和精度于一身。

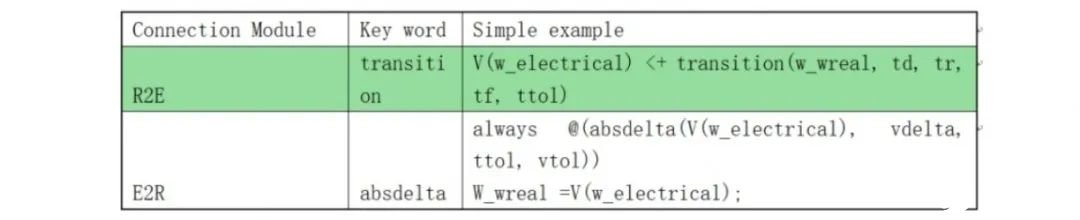

Wreal和electrical如何通信呢?由R2E (wreal to electrical), and E2R(Electrical to wreal)实现。他们转换关系总结如下表:

表3 RNM--Connection Module 2

RNM的缺点是在离散域要定义一些基本模块。因为标准的模拟建模语言中的内嵌函数(上升时间/转换/积分/微分和模拟滤波)离散实数域没有,需要按时间步长格式去实现。

Wreal由于忽略了阻抗效应的,只用于没有直接强反馈的模块的输入输出传输,所以在处理Inout端口时候比较吃力。所以在用SystemVerilog写的RNM中,支持用户自定义的Nettype (User Defined Nettype),Cadence利用这个标准引入了EEnet。在这个自定义的Nettype中,包含三个实数变量,分别用来表示电压,电阻和电流,进而实现戴维南或者诺顿等效。当多个EEnet连接到一起时,就形成了一个局域的电压源,电流源和电阻的网络。因为该网路只有有限节点,而且只求解当前状态,因此可以在一次运算中根据基尔霍夫电流和电压定律求解出连接点的电压,和流入/出各个模块的电流。由于求解EEnet构成的局域网络不需要进行迭代,因此可以有数字仿真器来进行数值求解。进而EEnet提供在离散模型中对loading effect的建模,从而在不牺牲速度的情况下提高模型精度。

D、Verilog

很多人都懂Verilog,不再详细介绍。

图9 Reference Model

E 、Reference Model

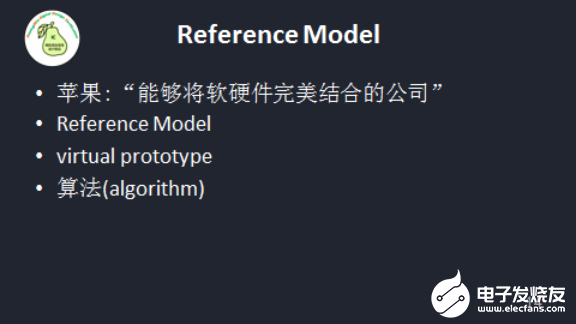

对于模拟IC了解Verilog就够了,但做数字的对Verilog形成的Model仍不满意。如何打通软件和硬件之间的联系?让一个软件工程师去懂硬件描述语言,显然太苦了,对Verilog进行再抽象就很有必要,很多验证工程师熟悉UVM,搞出Reference Model,或者系统工程师的Virtual Prototype或算法模型Model就是进一步的做减法而得到的Model。System Verilog,System C,都有支持你需求的描述Model,实现硬、较件工程师的一次跨界。

图10 不同建模类型的速度精度对比图

上述Model做减法(VerilogA、VerilogAMS、RVM、Verilog和Reference Model),一步步脱离Analog,一步步走进Digital,甚至硬件迈向软件,这就是Model做减法的魔力。可以参见图16经典的不同仿真模型的速度与精度对比图。

作者简介

邵亚利,模拟混合信号设计验证专家。浙江大学本硕,“模拟混合信号设计验证”公众号(yaliDV)创始人。曾就职于德州仪器(TI),现就职于亚德诺(ADI)半导体公司。ADI(Analog Devices) 是全球领先的高性能模拟技术公司,凭借杰出的检测、测量、电源、连接和解译技术,搭建连接现实模拟世界和数字世界的智能化桥梁。

责任编辑:pj

-

仿真器

+关注

关注

14文章

1020浏览量

84145 -

Model

+关注

关注

0文章

342浏览量

25229 -

Schematic

+关注

关注

1文章

13浏览量

11369

发布评论请先 登录

相关推荐

DLPC3478的Display模式和 Light Control模式,在DMD微镜的控制上的本质区别是什么呢?

深度解析:M12 接头 A 与 D 在性能参数上的本质区别及选型要点

仿真器与Model的本质区别

仿真器与Model的本质区别

评论