【在此特别鸣谢原文作者邵亚利】【芯人类】EDA 是芯片之母是IC 设计最上游、最高端的产业。也是中国集成电路产业最薄弱的环节。为向集成电路专业师生和从业者中系统介绍EDA技术的前沿进展,芯人类将分多期全文引入《电子报》EDA前沿技术专栏。专栏特邀行业多位专家,全面系统地介绍国内外EDA 的状况和国产EDA 的发展。本文为电子报授权发表。包含混合SOC的设计,验证和实现的方法流程三方面内容,并重点介绍了验证所需要了解的仿真器原理,和行为级建模相关的知识。共分三次发表。

片上系统(SOC)混合信号含量越来越高

集成电路从模拟电路开始,后来数字电路蓬勃发展,而今为了能够满足多种场合的不同复杂应用,例如高集成/低成本/可移动/多接口等要求,混合信号片上系统SOC(System On Chip)日益流行。SOC中的数模混合信号含量已经从10%~20%增加到50%或更高。

例如,在以数字为主的SOC中,离不开连接真实世界的ADC(Analog-to-Digital-Converter),DAC(Digital-To-Analog-Converter),还有提供高速时钟的PLL(Phase-Locked-Loop)以及射频收发器,存储器接口等。在以模拟为主的SOC中,也增加了Control/Trim/Calibration等数字逻辑,来补偿PVT(Process, Voltage, Temperature)的变化,提高性能指标和良率。数模电路甚至在不同层次中紧密结合。

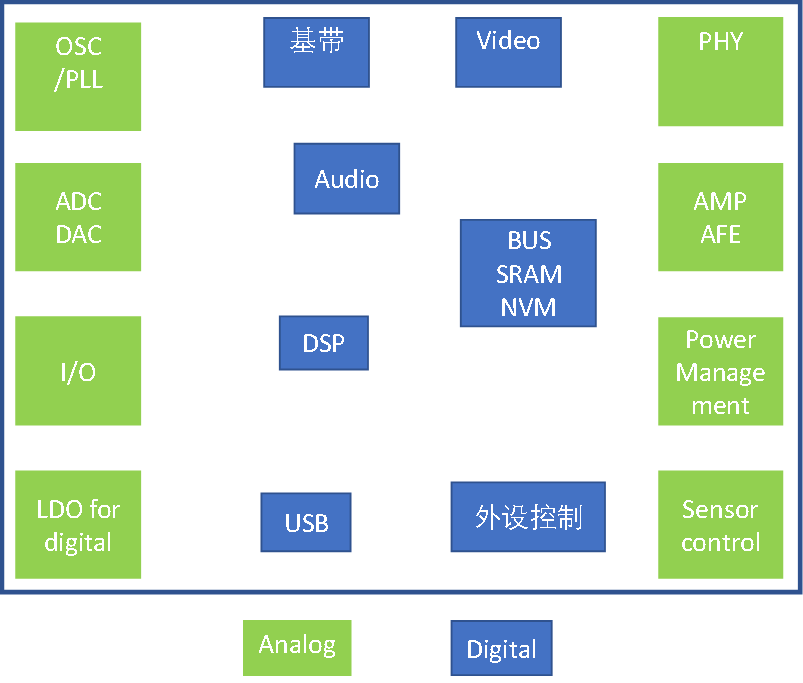

图1 混合信号SOC典型框图

这张图是一颗混合SOC芯片,蓝色部分是数字部分,通常有微处理器、基带(BB)、总线、SRAM (缓存,或者叫内存)、有NVM(非易失性存储器),比如说像FLASH、EEPROM,或者OTP,还有Video, Audio, USB,以及外设的一些接口控制电路,像SPI、I2C、HDMI接口或者UART、GPIO、PWM控制等。

绿色部分是模拟或者模拟为主的混合模块,通常有OSC/PLL振荡器,有作为数字和外界的窗口ADC或者DAC,有逻辑控制的GPIO作为通用的I/O接口,为了给数字电路供电有LDO,因为数字电路需要比较稳定的电源。

右边第一个是PHY,是协议物理层,通常它本身也是一个数模混合的模块,它既有数字电路也有模拟电路,把它放在这里就表示需要模拟工程师对它进行重点的关注。还有作为对微弱信号处理的放大器和模拟前端AFE(Analog Front End),AFE将模拟信号经过放大处理,把它输入到ADC或者数字电路当中。Power Management是经常会用到的一个模块,包括BUCK,BOOST或Charge Pump等模块,另外就是传感器的控制电路。前面这几个模块每个芯片都不一样,有可能有,有可能没有。但是左边这一列,基本上每个SOC芯片都会有。

数模混合SOC设计常用流程与工具

既然数模混合SOC市场需求越来大,那么如何设计与实现一款混合SOC呢?本章节主要探讨数模集成电路设计常用的流程与工具。

1.以数字为主的SOC设计流程

常用文档编辑工具,从高级描述开始,采用Verilog, System Verilog或者C语言,去设计数字电路并制作Test Bench(TB)和层次化的模型,再用仿真工具去仿真模型,然后通过标准单元库,自动综合成门级电路,生成网表,再对网表进行布图并生成三个文件(GDS、Netlist和Timing信息的SDF),设计告一段落。

在验证阶段需要模拟的Model,供数字控制模拟或者模拟返回到数字的模拟验证。也需要固件的二进制码供给TB对SOC进行仿真。

2.以模拟为主的SOC设计流程

区别于写代码,模拟IC设计通常是以电路图来做设计,电路图中包括电阻电容/MOS管等基本元件,和相关拓扑连接关系。模拟工程师通常先设计子模块,电路图的顶层则是由一个模拟顶层的线路图和一个空的数字模块构成。

顶层仿真开始阶段用Digital的RTL的IP模块和Firmware组合,加之模拟电路,进行Analog On Top的仿真。仿真验证通过后,RTL进行PR,再由Schematic Verilog-in组成最终顶层的线路图,结合数字的SDF的Timing约束,完成PR后的仿真。

从后端看,顶层仿真后进行Analog layout将等在Digital PR完成,然后Stream-in进来一起形成TOP的Layout,即使有些IP可能不会给底层的GDS,通过Phantom View形成TOP的Layout,再对它进行LVS。

3.数模集成电路设计的常见工具

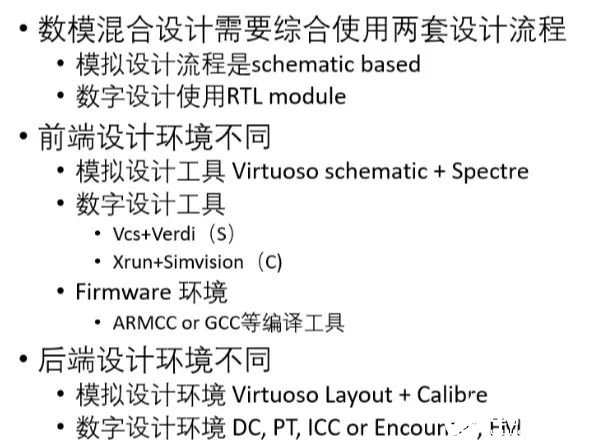

图2 数模混合设计与实现的常见工具

数模混合验证需要在顶层同时整合两套设计流程。模拟工程师熟悉的流程是Schematic Based,数字设计师使用RTL module。

通常熟悉Cadence Virtuoso schematic + Spectre的是模拟设计者。数字设计工具Synopsys用VCS+Verdi,Cadence用的是Xrun+Simvison,此外还要搭建Firmware的设计环境。当然,写程序和编译还要用到ARM CC或者像GCC之类的工具。

后端设计,模拟往往用Virtuoso Layout,再加上Calibre,做LVS和DRC;数字设计要用DC综合,时序分析PT(Prime Time),布图用ICC(或Encounter),还有FM(形式验证),Patten(测试矢量的自动生成)工具。

4.数模混合SOC并行协同设计流程

公开的/工业标准的数据库的出现,例如Open Access(OA),对数模混合SOC方法学的开发与应用做出了重要贡献。OA是一种层次化的数据库,能同时存储数字和模拟,从而不需要将数据从一种格式转换到另外一种格式。公共数据库是同步混合信号设计的基本要求,否则在以前单独的模拟或者数字方法学中,每个区域对对方而言都是黑盒子,就非常容易出错,甚至是低级错误,因为复杂的功能,不同的Background, 模糊的“Common Sense”,都增加了芯片出bug的风险,一些简单错误可能会导致很严重的后果,例如功能不正常,过长的流片后的debug时间,昂贵的再流片成本,更重要的是Delay的研发周期,错失的市场窗口。

通过OA数据库的支持,数字和模拟之间完全透明,从而诞生了数模混合并行协同设计的流程,它可以同时汲取数模流程中的优点,回避其缺点,从而最高效率地设计混合SOC。

以下表格对比和总结了以上三种数模混合IC的设计验证与实现流程。

表1 数模混合IC的设计/验证/实现流程

混合SOC验证的挑战与方法介绍

验证是在流片前,保证芯片的设计满足客户应用的指标要求。数模混合SOC的验证面临很多挑战,Time To Market的压力,芯片的研发周期Schedule在不断被压缩,成本也越来越低,且IC人才又相对有限。验证更需要一些对应的技巧与流程规范来达到验证目的。

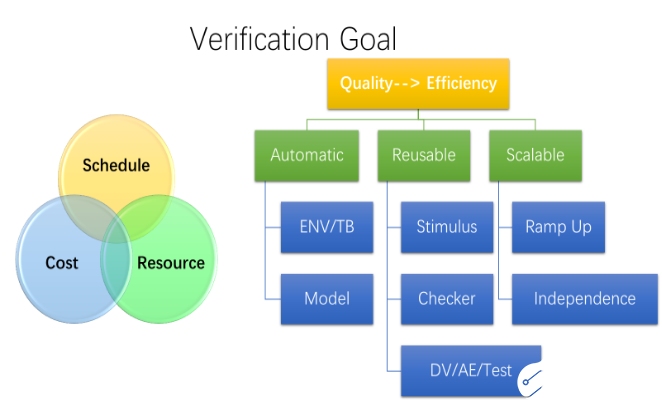

一个好的验证,需要达到什么目的呢?首先是最起码保证芯片的质量,以便First Silicon Sample。在保证质量的基础上,需要提高效率。主要有三个维度:首先是Automatic,如何让验证环境自动化产生,Test Bench自动产生,甚至Model自动产生等;其次是Reusable,例如Stimulus,Checker等,又或是DV/AE(Application Engineer)和TE(Test Engineer)之间的Reuse。第三是Scalable,高度集成的数模混合验证,通常需要很多人参与。如何让新资源快速的Ramp Up起来缩短适应时间;这么多人工作在同一个项目上,且做到彼此不相互影响,不Block Other’s work, 那就更需要验证环境和整个流程的分配协调,从而保证大家能够“各自为战”。

图3 验证目标

1.混合SOC验证的挑战

混合信号设计的复杂度急剧增长,促使设计队伍需要各种技能的工程师紧密合作;随工艺尺寸变小,需要电路抽象级别更高,以便在系统级进行分析和验证;为缩小数模之间的设计差距,需要更多采纳软硬件结合的自动化方法;数模之间数据交互,需要EDA工具和设计方法学支持,以加速数模混合验证的收敛。但是正如上文所述,数字模拟IC采用了不同的设计流程和工具,加之SOC复杂的功能性能要求,然而模拟工程师和数字工程师的背景却很不相同,任何一个环节出错,都可能造成严重的后果。

图4数模混合设计验证的挑战

图4列出来了目前公认的混合信号SOC所面临的挑战:模拟Spice/Fast Spice在复杂的SOC系统中仿真速度显然不够快,使得如果用最精确的模拟仿真会严重影响研发周期。晶体管-门级协同混合仿真比全Spice仿真要快,但是依然比较慢。对模拟电路去创建模型,则需要人才储备,知识积累,以及模型开发与验证时间。这是混合IC验证面临的前三大挑战。另外还有缺乏模拟混合设计验证IP,功耗意图,为覆盖率(Coverage)产生测试向量,软硬件协同验证等挑战。

另外物联网在低功耗方面的要求越来越高。造成芯片测试成本超过硅片本身,可测性设计就应该在设计过程中考虑。为此在保证正常功能与性能不降低的同时,增加片内自建的测试电路(Scan,IDDQ等),会使芯片尺寸增大10%左右,加上冗余修复等电路,都为提高产品品质和Debug提供了良好的基础,但也增大了数模混合的验证难度,因为不仅要验证正常功能,还需要验证可测试性功能。

2.混合SOC验证的方法流程

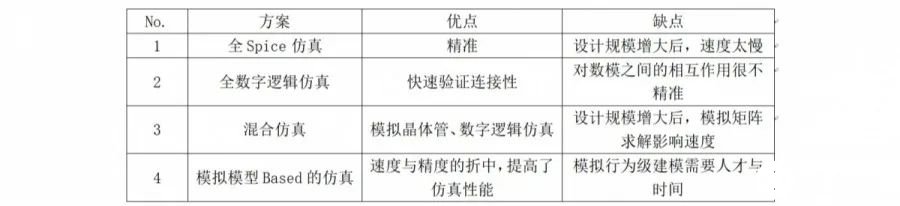

为了模拟和数字仿真同步的、平行的运行,解决混合信号验证的问题,有以下几项选择方案:

表2 混合SOC仿真验证方案

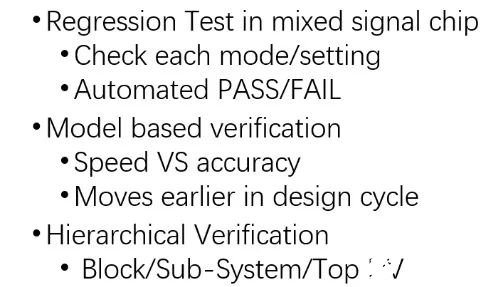

显然这四种方案各有优缺点,经常需要几种方案交互使用。这就诞生了基于Model的验证方法,以及层次化的验证技巧。

行为建模使得仿真在速度与精度之间做了非常好的折中,极大的提高了仿真效率;而且也能够让验证在项目的早期就介入其中,与设计并行,缩短整体研发周期。所以接下来本文第五部分将重点介绍Model知识。

层次化的验证方法,是将Block级设计者与验证者的工作,纳入了整体验证考量因素之中。哪些性能指标是应该在Block级进行验证,无须在Sub-System再验证,是需要有经验的工程师进行验证规划的。层次化的验证,重点强调每个级别上验证的侧重点的不同,使其形成一种整体的互补策略。同时也在层次化的Reuse验证部分的相同环节,减少Test Case 中Stimulus与Checker的创建。

图5数模混合SOC验证的方法

芯片的PVT变化,加之数字Random的概念,要求混合SOC必须做Regression测试,以便能够遍历所有的Mode和Setting,同时自动化的检查PASS或者FAIL的仿真结果,以应对设计变化时候的快速验证迭代。基于覆盖率Coverage和断言Assertion的指标驱动验证(MDV),是数模混合验证的重要内容。这在纯数字验证中,已经作为Sign Off标准。数字覆盖率主要有代码覆盖率,有限状态机覆盖率,功能覆盖率和结构覆盖率。混合信号的覆盖率通过采用数据分级(bin)的概念,将连续的电压电流等模拟值,转换为离散的用户自定义的范围,从而实现覆盖率的概念。断言Assertion,就是捕捉设计的预期行为,来判断数模混合属性是否满足Spec需求。标准的Assertion语言有PSL和SVA。为了满足混合信号,IC标准委员会正在致力于模拟SVA(ASVA)和System-Verilog的AMS(SV-AMS)。

FPGA验证对于验证数字模块有用,简单的数字模块仿真能够覆盖。复杂的数字模块,比如有上位机软件互动等,可以有效减少仿真验证工作量。对于提前开发软件、烧录工具、自动测试有帮助。对于数模混合部分,FPGA验证环境很难搭建。形式验证和硬件加速目前还没有针对模拟电路大量使用。所以以模拟为主的混合SOC主要以仿真验证为主。

数字验证已经有了比较流行的UVM(Universal Verification Methodology)方法学,混合信号领域的UVM-MS方法扩展包括模拟模块的验证计划,模拟信号的产生,模拟属性的检查和断言技术,以及模拟功能覆盖的分析。

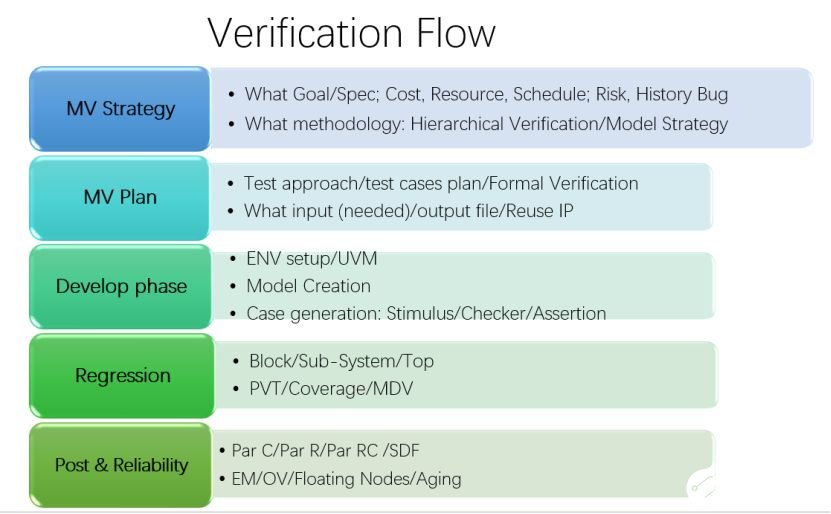

图6 验证流程介绍

最后,从项目研发进度的角度谈一下验证的流程。在项目刚开始阶段,需要考虑混合验证的策略(Strategy),主要包括验证目标是什么,客户要求Spec有哪些,项目周期,开发人员数量与技能等。项目风险在哪里,以前类似产品有哪些Bug。在方法学上采用自上而下与自下而上的结合么?怎么样做层次化的验证?建立Model的策略是什么?

清楚了策略之后,就需要开始具体制定验证计划。包括验证需要哪些Input File,哪些Output result,采用什么样的验证工具与手段,是否需要形式验证等。哪些通过RTL进行,哪些需要通过混合仿真,哪些需要通过晶体管仿真进行。

制定完计划后就是具体的实施阶段。主要包括验证环境(ENV)的搭建,UVM的引入,基于Model验证的Model本身的创建,以及Test Case所涉及的Stimulus,Checker与Assertion。

当Test Case建立完成以后,就需要开始跑Regression,分析Coverage,做MDV验证。

最后还要做一些后仿真。模拟的寄生R,C,的仿真,数字基于SDF的门级仿真。也需要做一些和可靠性相关的检查,例如电子迁移EM,过压OV,浮点Floating Nodes,与老化Aging等检查。

【在此特别鸣谢原文作者邵亚利】

作者简介

邵亚利,模拟混合信号设计验证专家。浙江大学本硕,“模拟混合信号设计验证”公众号(yaliDV)创始人。曾就职于德州仪器(TI),现就职于亚德诺(ADI)半导体公司。ADI(Analog Devices) 是全球领先的高性能模拟技术公司,凭借杰出的检测、测量、电源、连接和解译技术,搭建连接现实模拟世界和数字世界的智能化桥梁。

责任编辑:pj

-

soc

+关注

关注

38文章

4235浏览量

219720 -

数模混合

+关注

关注

0文章

23浏览量

9306 -

LVS

+关注

关注

1文章

37浏览量

9999

发布评论请先 登录

相关推荐

混合SOC验证的挑战与方法介绍

混合SOC验证的挑战与方法介绍

评论