6月11日消息,Moortec今天宣布其深度嵌入式监控产品组合再添新成员 -- 基于台积电N5工艺技术的分布式热传感器(DTS)。Moortec高度微粒化DTS的面积只有一些标准芯片内热传感器解决方案的七分之一,还支持以更快的转换速度在较宽的温度范围内进行高精度测量。凭借十余年为SoC行业提供先进节点热传感解决方案的经验,DTS加强了该公司在创新芯片内技术方面的领先地位。

随着几何尺寸向5纳米及以下发展,设计人员在提供可靠、节能和速度优化的芯片设计方面面临重大挑战。热活动是不可预测的,如果不仔细监控,可能会导致过热和功耗过大,进而影响设备寿命。在CPU核心、高速接口或高效电路旁边或内部进行精确热测量的能力已成为众多应用领域内所用设备的强制性要求。

Moortec首席执行官Stephen Crosher表示:“我们看到市场明显需要对半导体器件进行更严格的热控制。多核架构被应用于人工智能、汽车、消费和许多其他应用,利用高度分布式传感方案,最大限度地降低系统级功耗、优化数据吞吐量并延长产品寿命。我们相信,此次Moortec产品组合的扩展将使我们的客户能够最大限度地提高硅的性能,并进一步加强我们与台积电的长期合作。”

台积电设计基础设施管理部门高级总监Suk Lee表示:“我们很高兴能与Moortec合作,在最先进的台积电N5工艺上开发出这个新的热传感解决方案。我们与Moortec的长期合作将使设计人员能够受益于台积电最新技术所带来的显著的功率和性能提升,借助领先的解决方案,实现硅方面的成功。”

Moortec现在走在为许多高科技产品的任务模式操作提供深入见解的前沿,支持现场遥测、分析和产品级优化解决方案。DTS技术设计工具包于2020年初推出,已被授权给几个主要客户。

责任编辑:gt

-

传感器

+关注

关注

2553文章

51515浏览量

757302 -

台积电

+关注

关注

44文章

5705浏览量

167109 -

纳米

+关注

关注

2文章

699浏览量

37230

发布评论请先 登录

相关推荐

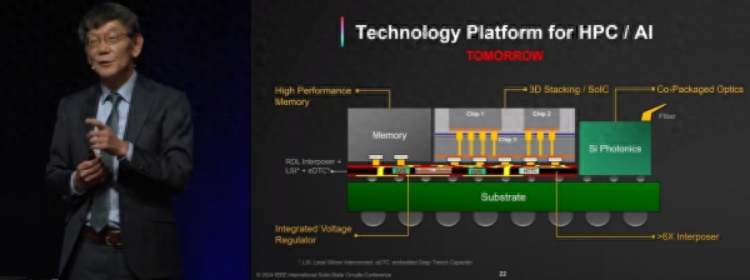

台积电推出“超大版”CoWoS封装,达9个掩模尺寸

最大限度地提高GSPS ADC中的SFDR性能:杂散源和Mitigat方法

Moortec推出基于台积电N5工艺技术的DTS,可最大限度地提高硅性能

Moortec推出基于台积电N5工艺技术的DTS,可最大限度地提高硅性能

评论