寄存器是由触发器组成的,一个触发器是一个一位寄存器。多个触发器就可以组成一个多位的寄存器。由于寄存器在计算机中的作用不同,从而被命名不同,常用的有缓冲寄存器、移位寄存器、计数器等。下面我们就简单的来介绍下这些寄存器的电路结构及工作原理。

1

缓冲寄存器

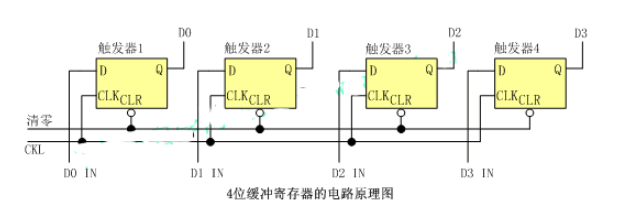

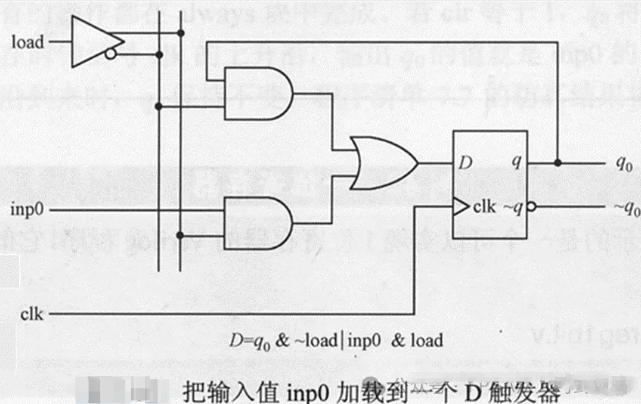

它是用来暂存某个数据,以便在适当的时间节拍和给定的计算步骤将数据输入或输出到其它记忆单元中去,下图是一个并行输入、并行输出的4位缓冲器的电路原理图,它由4个D触发器组成。

启动时,先在清零端加清零脉冲,把各触发器置0,即Q端为0。然后,把数据加到触发器的D输入端,在CLK时钟信号作用下,输入端的信息就保存在各触发器中(D0~D3)。

2

移位寄存器

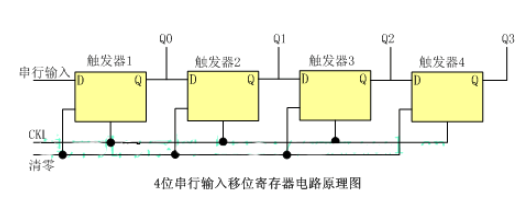

移位寄存器能将所储存的数据逐位向左或向右移动,以达到计算机运行过程中所需的功能,请看下图

启动时,先在清零端加清零脉冲,使触发器输出置0。然后,第一个数据D0加到触发器1的串行输入端,在第一个CLK脉冲的上升沿Q0=Q0,Q1=Q2。Q3=Q0。其后,第二个数据D1加到串行输入端,在第二个CLK脉冲到达时,Q0=Q1,Q1=Q0,Q2=Q3=0。以此类推,当第四个CLK来到之后,各输出端分别是Q0=Q3,Q1=Q2,Q2=Q1,Q3=Q0。输出数据可用串行的形式取出,也可用并行开式取出。

3

计数器

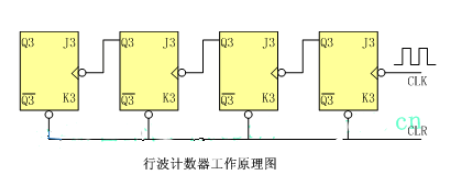

计数器也是由若干个触发器组成的寄存器,它的特点是能够把存款在其中的数据加1或减1。计数器的种类也很多,有行波计数器、同步计数器等,下面我们就以行波计数器向大家作个介绍。

下图就是一个由J-K触发器组成的行波计数器的工作原理图。这种计数器的特点是:第一个时钟脉冲促使其最低有效位加1,使其由0变1;第二个时钟脉冲促使最低有效位由1变0。同时推动第二位,使其由0变1;同理,第二位由1变0时又去推动第三位,使其由0变1,这样有如水波前进一样逐位进位下去。

上图中各位的J、K输入端都是悬浮的,这相当于J、K输入端都是置1的状态,即各位都处于准备翻转的状态。只要时钟脉冲边沿一到,最右边的触发器就会翻转,即Q由0转为1或由1转为0。

上图中的这个计数器是4位的,因此可以计015的数。如果要计更多的数,需要增加位数,如8位计数器可计0255的数,16位则可计0~65535的数。

4

三态门(三态缓冲器)

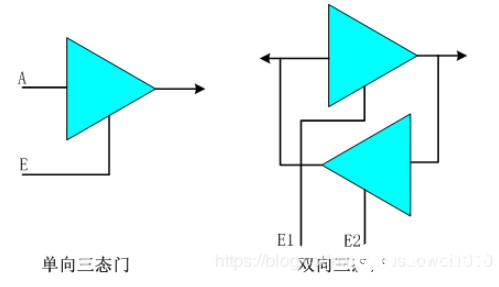

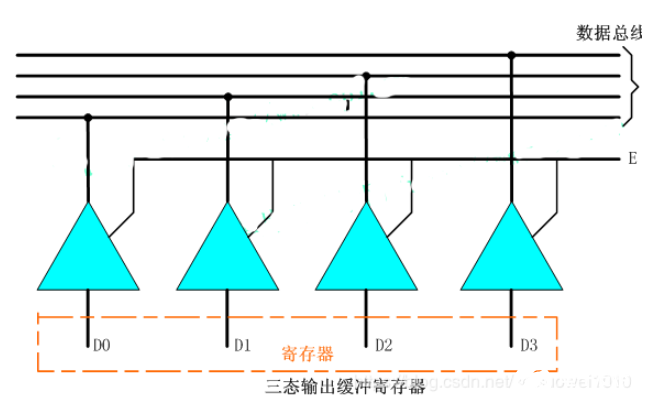

为减少信息传输线的数目,大多数计算机中的信息传输线均采用总线形式,即凡要传输的同类信息都走同一组传输线,且信息是分时传送的。在计算机中一般有三组总线,即数据总线、地址总线和控制总线。为防止信息相互干扰,要求凡挂在总线上的寄存器或存储器等,它的传输端不仅能呈现0、1两个信息状态,而且还应能呈现第三种状态——高阻抗状态(又称高阻状态),即此时好像它们的输出被断开,对总线状态不起作用,此时总线可由其它器件占用。三态门即可实现上述的功能,它除具有输入输出端之外,还有一控制端,请看下图。

当控制端E=1时,输出=输入,此时总线由该器件驱动,总线上的数据由输入数据决定;

当控制端E=0时,输出端呈高阻抗状态,该器件对总线不起作用。当寄存器输出端接至三态门,再由三态门输出端与总线连接起来,就构成三态输出的级冲寄存器。如下图所示就是一个4位的三态输出缓冲寄存器。由于这里采用的是单向三态门,所以数据只能从寄存器输出到数据总线。如果要实现双向传送,则要用双向三态门。

-

寄存器

+关注

关注

31文章

5308浏览量

119978 -

移位寄存器

+关注

关注

2文章

258浏览量

22227

发布评论请先 登录

相关推荐

寄存器间接寻址和寄存器寻址的区别

通用寄存器是什么意思

寄存器的类型和作用

寄存器故障分析

寄存器是什么意思?寄存器是如何构成的?

寄存器寻址和直接寻址的区别

寄存器寻址的实现方式

寄存器有哪几种?可以实现什么功能?

寄存器分为基本寄存器和什么两种

CPU的6个主要寄存器

移位寄存器的工作原理 移位寄存器左移和右移怎么算

labview移位寄存器如何清零

寄存器查看器的功能和使用

寄存器的特性和四大种类

寄存器的特性和四大种类

评论