1、引言

数字移相器是收/发(t/r)组件中用于控制电波束的核心元件,在整机系统中被广泛应用,为减小t/r模块的尺寸和重量,降低成本与功耗,提高开关速度,主要采用的是微波单片集成电路(mmic)工艺制造移相器。

单片移相器是制作在gaas基片上的微波电路,其工作原理和电路功能与传统的微波电路移相器相同,但在设计方法上有很大的不同。这是因为:(1)制作在gaas基片上的所有元件(包括有源器件及无源元件)都是“平面”结构,它们虽然与传统微波电路元件采用的名称相同,但特性不同,需用复杂的模型来描述。(2)由于gaas基片的微波传输特性与传统的微波基片有很大不同,造成以gaas为基片制作的微波电路存在复杂的寄生效应;mmic中各个元件排列又十分紧凑,相互间的耦合寄生也较严重,因此,设计中必须仔细分析修正,进行电磁场验证。除此之外,mmic使用半导体集成技术制成,其特性唯一地由设计与制造决定,无法像传统的微波电路那样调试。

由此可见,单片移相器的设计技术具有较大的特殊性与复杂性,对设计优化的要求很高,尤其是考虑到gaas mmic高昂的制造成本(制版、工艺、测试等),设计必须一次成功,因而,必须在电路模拟时利用计算机cad技术保证设计的准确性,本文将介绍数控单片移相器的cad设计过程,解决cad技术中的难题。

2 、选取合适的元器件模型及电路拓扑

移相器的共性在于结构上都是晶体管作为开关再辅以各种无源元件,通过控制开关使信号在通过无源元件时产生不同的相移,从而实现移相功能,在进行移相器电路的cad输入之前,首先要选取合适的元器件模型和电路拓扑。

2.1 开关器件模型

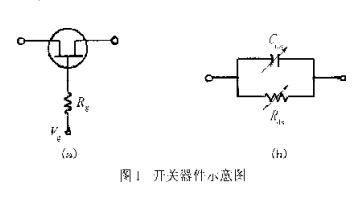

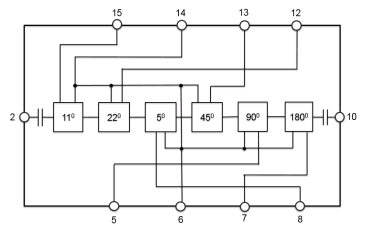

gaas mesfet,phemt都是单片移相器的理想器件,通常工作于无源状态,没有直流功耗,作为开关器件工作,开关器件的源极和漏极作为射频端,栅极作为控制端,由栅极和源极的相对电位决定其导通和关断(图1)。开关导通时,rds很小,cds较大;开关截止时,rds很大,cds较小,栅电阻rg起隔离信号的作用,应取得足够大。

设计者选定工艺加工线后,应使用该制造商提供的器件模型进行电路设计,其可以根据需求自建模型或对模型进行处理和完善。

2.2 无源元件模型

无源元件大体上分为集总元件和分布元件,集总元件主要指电阻、电容、电感;分布元件主要指传输线。通常当设计电路的工作频段非常宽时,才采用传输线作为匹配元件,集总元件在单片移相器电路中普遍使用的有体电阻、薄膜电阻、mim电容、螺旋电感。体电阻主要用于栅极偏置,隔离高频信号,薄膜电阻主要用于电路匹配,mim电容和螺旋电感主要用于匹配、滤波。

2.3 移相器电路拓扑

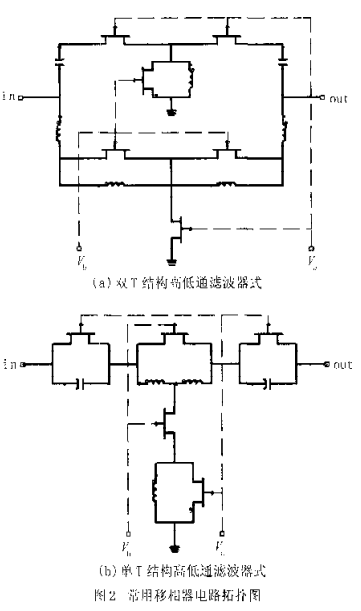

目前普遍采用的单片数字移相器电路有开关线式、反射式、加载线式和高低通滤波器式。设计者根据电性能要求、工艺制造难度及性价比为不同的移相位取合适的电路拓扑。开关线式、反射式、加载线式移相器中均需使用分布参数传输线段,占用相当大的芯片面积,而高低通滤波器式移相器用集总元件组成,可做得十分紧凑,这种电路拓扑适用于宽带电路,用于窄带电路设计时某些电性能可望有较大的改善,因此应用最为普遍。

图2是两种常用移相器电路拓扑图。

3、 移相器的cad设计优化

3.1 选择eda工具

eda软件仿真器是mmic设计者必不可少的工具,在数控单片移相器的设计中,mmic设计软件必须敏捷、准确、具有良好的用户界面,能实现电路仿真、优化、综合、版图设计、电磁场分析等功能,此外还能在基于工艺线的设计环境进行电路设计。

3.2 电路设计

根据电性能指标,每一种移相状态需制定的优化目标有:参考态驻波、移相态驻波、相移、参考态插损、移相态插损、插损波动、相移误差等。比如五位移相器共有32种状态,其优化目标多达近200项。因此合理地设定优化途径极为重要,否则不仅耗费大量机时,优化成效极低,甚至完全得不到结果,多位数字移相器的优化途径为:先优化单个位,再根据单个位的优化结果进行多位级联优化。

首先对各单个位的集总参数电路进行优化,得到各位最佳拓扑及集中参数值。接着通过综合将集总参数电容转为相应的mim电容,将集总参数电感转为螺旋电感或长微带线,将集总参数电阻转为体电阻或薄膜电阻,将连接线转为微带线。完成物体结构的综合后,根据电路设计指标对各位移相器做性能优化。

电路优化时应注意:初始优化的变量不宜太多,变量初值及上下限要合理;频率点由少到多,最后进行全频域为调整:初始值没有把握时,先用随机优化,再换梯度法,适当更换优化方法,同时改变加权值,优化次数适当,不能太少,根据效果修改或更换电路拓扑。

设计数字移相器的单个移相位时,需要根据整体电路的指标制定不同单个位的设计指标,每一个移相位均先分别优化到驻波最小,使在随后完整的移相器优化中各位之间的相互影响尽可能小。

将各单个位级联,按真值表各单个位设在不同的工作状态,从而得到全部移相态。对五位数字移相器而言,共有32种状态,对应输入输出有64个端口,优化变量及优化目标多达数百个,为解决这个难题,我们先将每一个移相位设计好,级连之后的电路分析结果已基本满足整体电路的设计指标,因此,做整体电路优化时,只需要对部分变量做微调。

为给工艺制作过程中的控制精度提供参考,需要对电路参数做灵敏度分析。分析时根据工艺线上可能达到的控制精度取上下限对整个电路做s参数仿真分析,比较电路指标的差异,分析的项目包括基片厚度、基片介电常数、mim电容的厚度,电容介质sin的介电常数及各条微带线的长度和宽度等。

3.3 电磁场验证

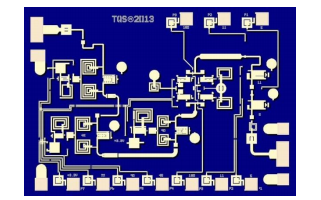

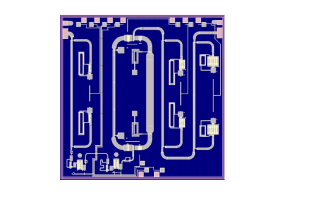

电路物理结构设计完成后,按照物理结构利用eda工具对电路版图布局。添加必要的过渡线、拐弯和t型结等,将版图控制在合理的范围内,尽量扩大各元件距离,减小相互耦合,对于较高应用频段的单片移相器,版图布局引起的寄生效应使电路实际性能与原设计优化结果会有较大偏离,因此必须进行版图布局优化,通常借助全波em分析软件对条件后的版图布局进行整体分析验证。

由于移相器电路器件数目较多,做全版图电磁仿真时端口数过多,仿真起来十分困难,当版图中不同移相位的元件间距较远时,各移相位间的耦合影响不大,只需要对每个移相位单独做电磁仿真。做电磁仿真时应按照加工工艺设置衬底,定义不同的层。

4 、数控单片移相器的开发应用

结合前面的讨论,我们给出gaas mmic数字移相器的设计和制造的一般过程:1、结合工艺制造技术及电路性能最佳要求选取或建立元器件模型,2、根据电性能要求及工艺制造难度对各个不同的单个位选取最佳的电路拓扑;3、根据选定的电路拓扑,对各个不同的单个位利用cad进行优化设计;4、根据电性能指标确定优化目标,根本选定的拓扑确定优化变量;5、根据单个位的优化结果进行多位级联优化;6、根据制造工艺、尺寸和使用时加电要求进行电路版图布局设计及电磁验证;7、制版、进行工艺流程;8、对合格的芯片进行微波电性能测试

如果一次设计不能满足要求,则要在上述过程中找出仿真和实际测试的不吻合处,再次改版设计,实际的设计过程可能是一个反复循环的过程,高性能的cad软件可以加速上述的循环过程,使设计的移相器具有有意的电性能,较高的成品率及尽可能小的芯片面积。

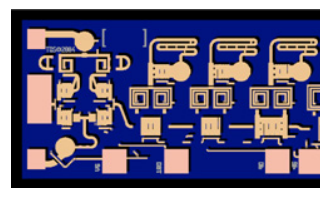

我们使用agilent ads微波设计软件设计了一款x波段单片五位数字移相器,并在我所gaas工艺线上制作完成。电路实测电性能与原设计优化结果基本一致,相移均方根误差小于1.5°,驻波小于1.7,插入损耗小于8db。

5、 结语

cad技术可以缩短移相器的研制周期,提高设计精度,降低成本,本文针对多位单片移相器的特点论述了其cad设计过程及设计难点,为数控单片移相器的研制提供了实用的解决方案,应用这一研究成果,高性能的x波段单片五位数字移相器以及其他系列数字移相器已经开发成功。

责任编辑:gt

-

元器件

+关注

关注

112文章

4689浏览量

91952 -

射频

+关注

关注

104文章

5545浏览量

167528 -

CAD

+关注

关注

17文章

1078浏览量

72342

发布评论请先 登录

相关推荐

CHP4014-98F数字移相器

如何通过串口发送一个小于65535的五位数?

CL102组成五位数码显示器线路图

TGP2102 5位移相器的详细资料数据手册免费下载

TGP2109-SM 6位数字移相器的详细数据手册免费下载

TGP2615 6位数字移相器的详细数据手册免费下载

TGP2105 6位数字移相器的详细数据手册免费下载

HMC644ALC5:GaAs MMIC 5位数字移相器,15-18.5 GHz数据表

HMC936ALP6E:GaAs MMIC 6位数字移相器,1.2至1.4 GHz数据表

HMC648ALP6E:GaAs MMIC 6位数字移相器2.9-3.9 GHz数据表

HMC642ALC5:GaAs MMIC 6位数字移相器,9-12.5 GHz数据表

HMC649ALP6E:GaAs MMIC 6位数字移相器,3-6 GHz数据表

HMC1133LP5E:GaAs MMIC 6位数字移相器,4.8-6.2 GHz数据表

HMC647ALP6E:GaAs MMIC 6位数字移相器,2.5-3.1 GHz数据表

基于CAD技术实现x波段单片五位数字移相器的设计

基于CAD技术实现x波段单片五位数字移相器的设计

评论