芯片封装,简单点来讲就是把制造厂生产出来的集成电路裸片放到一块起承载作用的基板上,再把管脚引出来,然后固定包装成为一个整体。它可以起到保护芯片的作用,相当于是芯片的外壳,不仅能固定、密封芯片,还能增强其电热性能。所以,封装对 CPU 和其他大规模集成电路起着非常重要的作用。

介绍一下几种常见的芯片封装类型。

DIP 双列直插式

DIP 是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路均采用这种封装形式,其引脚数一般不超过 100 个。采用 DIP 封装的 CPU 芯片有两排引脚,需要插入到具有 DIP 结构的芯片插座上。当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。DIP 封装的芯片在从芯片插座上插拔时应特别小心,以免损坏引脚。

DIP 封装结构形式有多层陶瓷双列直插式 DIP,单层陶瓷双列直插式 DIP,引线框架式 DIP(含玻璃陶瓷封接式,塑料包封结构式,陶瓷低熔玻璃封装式)等。

DIP 是最普及的插装型封装,应用范围包括标准逻辑 IC,存储器和微机电路等。

特点:

适合在 PCB(印刷电路板)上穿孔焊接,操作方便。

芯片面积与封装面积之间的比值较大,故体积也较大。

最早的 4004、8008、8086、8088 等 CPU 都采用了 DIP 封装,通过其上的两排引脚可插到主板上的插槽或焊接在主板上。

在内存颗粒直接插在主板上的时代,DIP 封装形式曾经十分流行。DIP 还有一种派生方式 SDIP(Shrink DIP,紧缩双入线封装),它比 DIP 的针脚密度要高六倍。

现状:

但是由于其封装面积和厚度都比较大,而且引脚在插拔过程中很容易被损坏,可靠性较差。同时这种封装方式由于受工艺的影响,引脚一般都不超过 100 个。随着 CPU 内部的高度集成化,DIP 封装很快退出了历史舞台。只有在老的 VGA/SVGA 显卡或 BIOS 芯片上可以看到它们的“足迹”。

PQFP/PFP 封装

PQFP 封装的芯片四周均有引脚,引脚之间距离很小,管脚很细,一般大规模或超大型集成电路都采用这种封装形式,其引脚数一般在 100 个以上。

用这种形式封装的芯片必须采用 SMT(表面组装技术)将芯片与主板焊接起来。采用 SMT 安装的芯片不必在主板上打孔,一般在主板表面上有设计好的相应管脚的焊点。将芯片各脚对准相应的焊点,即可实现与主板的焊接。

PFP 方式封装的芯片与 PQFP 方式基本相同。唯一的区别是 PQFP 一般为正方形,而 PFP 既可以是正方形,也可以是长方形。

特点:

PQFP 封装适用于 SMT 表面安装技术在 PCB 上安装布线,适合高频使用,它具有操作方便、可靠性高、工艺成熟、价格低廉等优点。

现状:

PQFP 封装的缺点也很明显,由于芯片边长有限,使得 PQFP 封装方式的引脚数量无法增加,从而限制了图形加速芯片的发展。平行针脚也是阻碍 PQFP 封装继续发展的绊脚石,由于平行针脚在传输高频信号时会产生一定的电容,进而产生高频的噪声信号,再加上长长的针脚很容易吸收这种干扰噪音,就如同收音机的天线一样,几百根“天线”之间互相干扰,使得 PQFP 封装的芯片很难工作在较高频率下。

此外,PQFP 封装的芯片面积 / 封装面积比过小,也限制了 PQFP 封装的发展。90 年代后期,随着 BGA 技术的不断成熟,PQFP 终于被市场淘汰。

PGA(插针网格阵列)封装

PGA 封装的芯片内外有多个方阵形的插针,每个方阵形插针沿芯片的四周间隔一定距离排列,根据管脚数目的多少,可以围成 2~5 圈。安装时,将芯片插入专门的 PGA 插座。为了使得 CPU 能够更方便的安装和拆卸,从 486 芯片开始,出现了一种 ZIF CPU 插座,专门用来满足 PGA 封装的 CPU 在安装和拆卸上的要求。该技术一般用于插拔操作比较频繁的场合之下。

特点:

⒈插拔操作更方便,可靠性高。

⒉可适应更高的频率。

BGA(球栅阵列)封装

随着集成技术的进步、设备的改进和深亚微米技术的使用,LSI、VLSI、ULSI 相继出现,硅单芯片集成度不断提高,对集成电路封装要求更加严格,I/O 引脚数急剧增加,功耗也随之增大,当 IC 的频率超过 100MHZ 时,传统封装方式可能会产生所谓的“CrossTalk”现象,而且当 IC 的管脚数大于 208 Pin 时,传统的封装方式有其困难度。为满足发展的需要,在原有封装品种基础上,又增添了新的品种——球栅阵列封装,简称 BGA。

BGA 封装的 I/O 端子以圆形或柱状焊点按阵列形式分布在封装下面。

特点:

1.I/O 引脚数虽然增多,但引脚间距远大于 QFP,从而提高了组装成品率。

2. 虽然它的功耗增加,但 BGA 能用可控塌陷芯片法焊接,简称 C4 焊接,从而可以改善它的电热性能。

3. 厚度比 QFP 减少 1/2 以上,重量减轻 3/4 以上。

4. 寄生参数减小,信号传输延迟小,使用频率大大提高。

5. 组装可用共面焊接,可靠性高。

6.BGA 封装仍与 QFP、PGA 一样,占用基板面积过大。

QFP(方型扁平式)封装

该技术实现的 CPU 芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在 100 以上。

特点:

1. 适用于 SMD 表面安装技术在 PCB 电路板上安装布线。

2. 适合高频使用。

3. 操作方便,可靠性高。

4. 芯片面积与封装面积之间的比值较小。

QFN 封装类型

QFN 是一种无引线四方扁平封装,是具有外设终端垫以及一个用于机械和热量完整性暴露的芯片垫的无铅封装。

该封装可为正方形或长方形。封装四侧配置有电极触点,由于无引脚,贴装占有面积比 QFP 小,高度 比 QFP 低。

特点:

1. 表面贴装封装,无引脚设计。

2. 无引脚焊盘设计占有更小的 PCB 面积。

3. 组件非常薄(《1mm),可满足对空间有严格要求的应用。

4. 非常低的阻抗、自感,可满足高速或者微波的应用。

5. 具有优异的热性能,主要是因为底部有大面积散热焊盘。

6. 重量轻,适合便携式应用。

QFN 封装的小外形特点,可用于笔记本电脑、数码相机、个人数字助理(PDA)、移动电话和 MP3 等便携式消费电子产品。从市场的角度而言,QFN 封装越来越多地受到用户的关注,考虑到成本、体积各方面的因素,QFN 封装将会是未来几年的一个增长点,发展前景极为乐观。

LCC 封装

LCC 封装的形式是为了针对无针脚芯片封装设计的,这种封装采用贴片式封装,它的引脚在芯片边缘地步向内弯曲,紧贴芯片,减小了安装体积。但是这种芯片的缺点是使用时调试和焊接都非常麻烦,一般设计时都不直接焊接到印制线路板上,而是使用 PGA 封装的结构的引脚转换座焊接到印制线路板上,再将 LCC 封装的芯片安装到引脚转换座的 LCC 结构形式的安装槽中,这样的芯片就可随时拆卸,便于调试。

COB 封装

COB 封装全称板上芯片封装,是为了解决 LED 散热问题的一种技术。相比直插式和 SMT 其特点是节约空间、简化封装作业,具有高效的热管理方式。

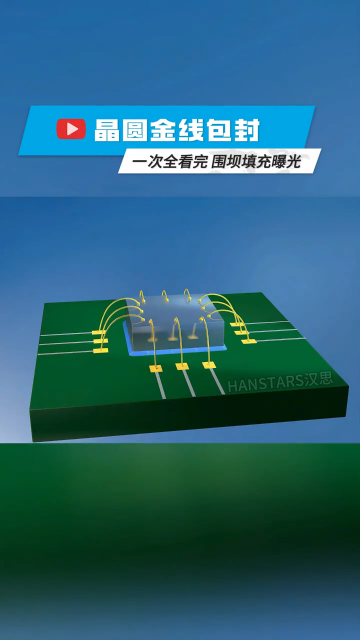

COB 封装是将裸芯片用导电或非导电胶粘附在互连基板上,然后进行引线键合实现其电气连接。如果裸芯片直接暴露在空气中,易受污染或人为损坏,影响或破坏芯片功能,于是就用胶把芯片和键合引线包封起来。

SO 类型封装

SO 类型封装包含有:SOP(小外形封装)、TOSP(薄小外形封装)、SSOP (缩小型 SOP)、VSOP(甚小外形封装)、SOIC(小外形集成电路封装)等类似于 QFP 形式的封装,只是只有两边有管脚的芯片封装形式,该类型的封装是表面贴装型封装之一,引脚从封装两侧引出呈“ L” 字形。

该类型的封装的典型特点就是在封装芯片的周围做出很多引脚,封装操作方便,可靠性比较高,是目前的主流封装方式之一,目前比较常见的是应用于一些存储器类型的 IC。

SIP 封装

SIP 封装是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。与 SOC 相对应。不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而 SOC 则是高度集成的芯片产品。从封装发展的角度来看,SIP 是 SOC 封装实现的基础。

SiP 的应用非常广泛,主要包括:无线通讯、汽车电子、医疗电子、计算机、军用电子等。

3D 封装

3D 晶圆级封装,包括 CIS 发射器、MEMS 封装、标准器件封装。是指在不改变封装体尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上芯片的封装技术,它起源于快闪存储器(NOR/NAND)及 SDRAM 的叠层封装。

3D 封装主要特点包括:多功能、高效能;大容量高密度,单位体积上的功能及应用成倍提升以及低成本。

分类:

一:封装趋势是叠层封(PoP);低产率芯片似乎倾向于 PoP。

二:多芯片封装(MCP)方法,而高密度和高性能的芯片则倾向于 MCP。

三:以系统级封装(SiP)技术为主,其中逻辑器件和存储器件都以各自的工艺制造,然后在一个 SiP 封装内结合在一起。

目前的大多数闪存都采用多芯片封装(MCP,Multichip Package),这种封装,通常把 ROM 和 RAM 封装在一块儿。多芯封装(MCP)技术是在高密度多层互连基板上,采用微焊接、封装工艺将构成电子电路的各种微型元器件(裸芯片及片式元器件)组装起来,形成高密度、高性能、高可靠性的微电子产品(包括组件、部件、子系统、系统)。

责任编辑:tzh

-

芯片

+关注

关注

456文章

50908浏览量

424447 -

cpu

+关注

关注

68文章

10873浏览量

212086 -

DIP

+关注

关注

0文章

241浏览量

30166

发布评论请先 登录

相关推荐

BGA芯片的封装类型 BGA芯片与其他封装形式的比较

常见的PCB元件封装类型

半导体封装技术的类型和区别

贴片电感有哪些封装类型

飞凌嵌入式-ELFBOARD 从七种芯片封装类型,看芯片封装发展史

对芯片封装类型的认识

对芯片封装类型的认识

评论