概述

Zynq UltraScale+ MPSoC 系列基于 Xilinx UltraScale MPSoC 架构,在单个器件中集成了功能丰富的、基于 ARM 的 64 位四核或双核处理系统 (PS) 和 Xilinx 可编程逻辑 (PL) UltraScale 架构。此外,还包括片上存储器、多端口外部存储器接口以及丰富的外设接口,尤其是 16.3 Gbps GTH 收发器,该收发器支持与像 NVMe SSD 驱动器这样的 PCI Express Gen3 存储设备接口。本文展示了通过使用 Design Gateway 的 NVMeG3-IP 内核在 Xilinx 的 ZCU102 评估套件上实现 NVMe 固态硬盘 (SSD) 接口的解决方案,该方案可实现惊人的快速性能:写入速度达 2,319 MB/s,读取速度达 3,347 MB/s。

Zynq UltraScale+ MPSoC ZCU102 评估套件简介

ZCU102 是用于快速原型开发的通用评估板,基于 XCZU9EG-2FFVB1156E MPSoC 器件。该评估板包含高速 DDR4 SODIMM 和组件内存接口、FMC 扩展端口、每秒数千兆位的串行收发器、各种外设接口以及用于用户定制设计的 FPGA 逻辑器件,藉此提供一个灵活的原型开发平台。

图 1:ZCU102 评估套件。(图片来源:Xilinx Inc.)

ZCU102 提供可编程逻辑功能,可用于 5G 无线网络、下一代高级驾驶辅助系统 (ADAS) 和工业物联网 (IIoT) 解决方案等最先进的应用。

总之,对于需要像 NVMe SSD 驱动器这样的高性能、高可靠性外部数据存储的应用来说,都有必要采用合适的解决方案,以充分利用支持 PCI Express Gen3 接口的 GTH 收发器。

NVMe SSD 存储简介

NVM Express (NVMe) 定义了主机控制器通过 PCI Express 访问 SSD 的接口。NVM Express 仅使用两个寄存器(命令发出和命令完成),从而优化了命令发出和完成过程。除此以外,NVMe 支持并行操作,在单个队列中支持多达 64K 的命令。64K 命令条目提高了顺序访问和随机访问两方面的传输性能。

NVMe 驱动器为高速数据存储和计算铺平了道路。借助 PCIe Express Gen3 技术,新型 NVMe SSD 驱动器即可实现高达 40 Gbps 的峰值性能。

此处展示了 NVMe 存储设备示例。

在 ZCU102 上 NVMe 主机控制器的实现

图 2:NVMe 实现。(图片来源:Design Gateway)

按照惯例,NVMe 主机是通过将主机处理器与 PCIe 控制器配合使用来实现的,从而实现与 NVMe SSD 的数据传入与传出。实现 NVMe 协议的目的是,为了与通过较高速总线连接的 PCIe 控制器硬件 CPU 外设进行设备驱动器通信。而数据缓冲和命令队列都需要外部 DDR 内存,以便在 PCIe 控制器与 SSD 之间传输数据。

由于 ZCU102 上的 XCZU9EG-2FFVB1156E FPGA 器件上不含 PCIe Gen3 集成块,因此无法采用传统实现方法。

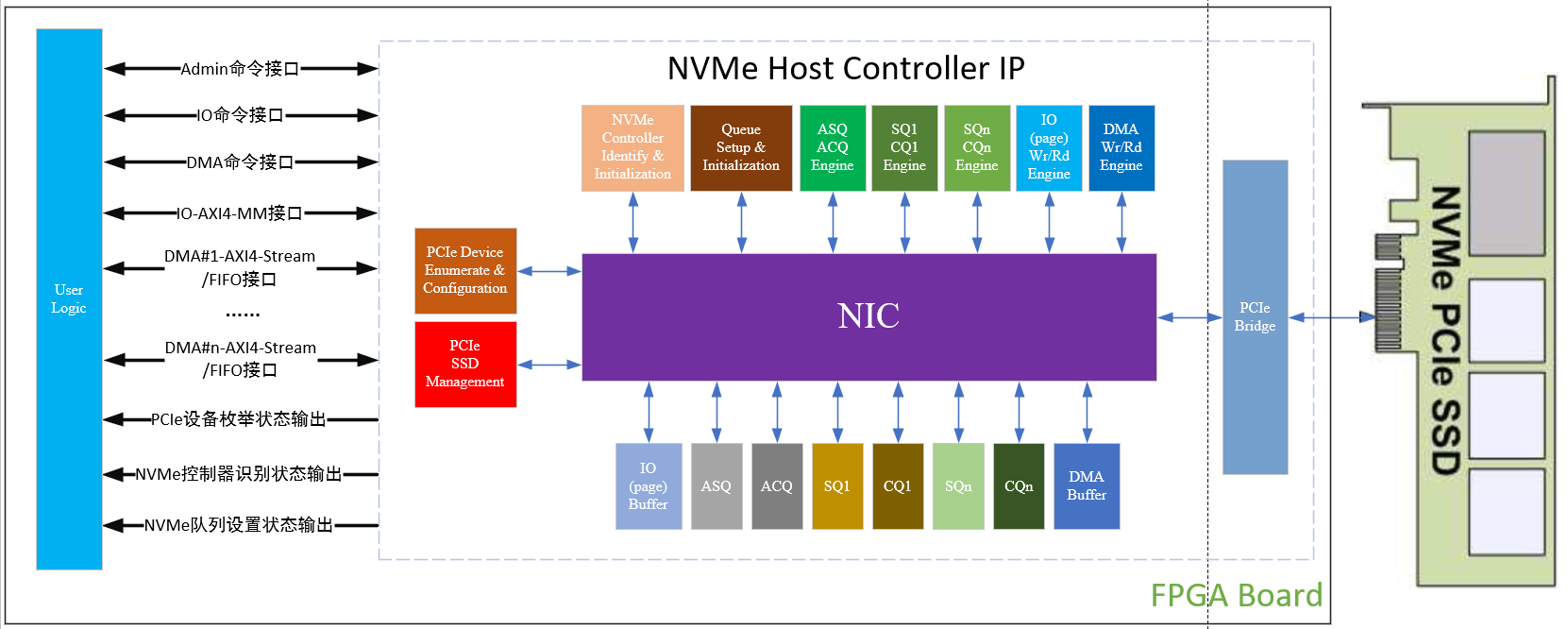

于是,Design Gateway 提出了一种解决方案,即利用 NVMeG3-IP 内核(如图 2 所示)来实现 Zynq UltraScale+ MPSoC 器件(不含 PCIe 集成块)的 NVMe SSD 接口。通过 NVMe 接口,ZCU102 即可构建具有较高性能的多通道 RAID 系统,同时最大限度地降低 FPGA 资源消耗。NVMeG3-IP 内核许可中包含参考设计示例,可帮助设计人员缩短开发时间并降低成本。

Design Gateway 的 NVMeG3-IP 概述

在不具备 PCIe 集成块、CPU 和外部存储器的情况下,具有 PCIe Gen3 IP 软核 (NVMeG3-IP) 的 NVMe IP 内核是访问 NVMe SSD 的理想之选。NVMeG3-IP 包含 PCIe Gen3 IP 软核和 256 KB 存储器。如果您的应用需要具有较高速性能的 NVMe SSD 存储,却又使用了不包含 PCIe 集成块的低成本 FPGA,那么建议您使用该解决方案。

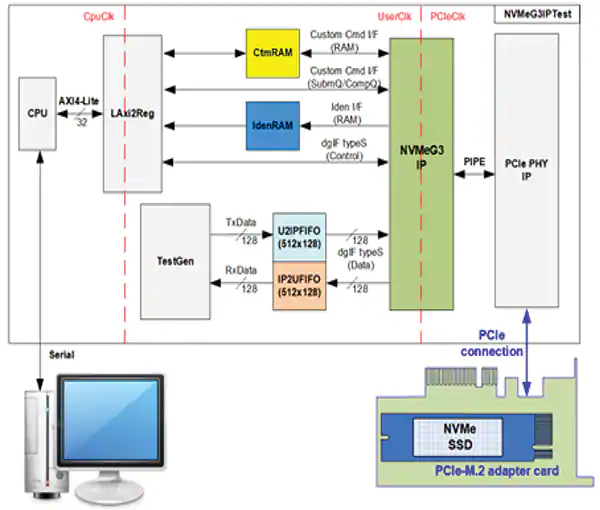

图 3:NVMeG3-IP 框图。(图片来源:Design Gateway)

NVMeG3-IP 特性

NVMeG3-IP 具有许多特性,以下列出了其中一部分特性:

1.实现应用层、事务层、数据链路层以及物理层的某些部分以访问 NVMe SSD,而无需占用 CPU

2. 与配置为 4 通道 PCIe Gen3(128 位总线接口)的 Xilinx PCIe PHY IP 配合操作

3. 包含 256 KB 的 RAM 数据缓冲区

4. 经由 dgIF typeS 的简单用户接口

5. 支持六个命令,即“识别”、“关闭”、“写入”、“读取”、"SMART" 和“刷新”(支持其他命令作为可选项)

6. 支持的 NVMe 器件:

基类代码:01h(大容量存储),子类代码:08h(非易失性),编程接口:02h (NVMHCI)

最小存储器页大小 (MPSMIN):0 (4 KB)

最大数据传输大小 (MDTS):至少 5 (128 KB) 或 0(无限制)

LBA 单元:512 字节 或 4096 字节

7. 用户时钟频率必须大于或等于 PCIe 时钟(Gen3 为 250 MHz)

8. 可用参考设计:

带有 AB17-M2FMC 适配器板的 ZCU102

带有 AB18-PCIeX16/AB16-PCIeXOVR 适配器板的 KCU105

带有 AB18-PCIeX16 适配器板的 VCU118

Design Gateway 将 NVMeG3-IP 开发成可以作为 NVMe 主机控制器运行,以访问 NVMe SSD。用户接口和标准特性旨在实现易用性,无需了解 NVMe 协议的相关知识。NVMeG3-IP 的附加特性是内置的 PCIe IP 软核,它能通过纯逻辑实现 PCIe 协议的数据链路层和物理层的某些部分。因此,借助内置的 PCIe IP 软核和 Xilinx PCIe PHY IP 内核,NVMeG3-IP 即可在不带 PCIe 集成块的 FPGA 上运行。Xilinx 的 PCIe PHY IP 是一款可用的免费 IP 内核,包含收发器和逻辑均衡器。

NVMeG3-IP 支持六个 NVMe 命令,即识别、关闭、写入、读取、SMART 和刷新。NVMeG3-IP 中集成了 256 KB 的 BlockRAM,可用作数据缓冲区。该系统无需 CPU 和外部存储器。如需更多详细信息,请查阅 NVMeG3-IP 规格书,可从我们的网站下载此规格书。

XCZU9EG-2FFVB1156E FPGA 器件的 FPGA 资源使用情况,如下表 1 所示。

表 1:Ultrascale/Ultrascale+ 器件的示例实现统计数据

ZCU102 的实现和性能结果

图 4 展示了基于 ZCU102 的参考设计概览,以演示 NVMeG3-IP 的操作。该演示系统中的 NVMeG3IPTest 模块包括以下模块:TestGen、LAxi2Reg、CtmRAM、IdenRAM 和 FIFO。

有关 NVMeG3-IP 参考设计的更多详细信息,请参考 Design Gateway 网站上提供的 NVMeG3-IP 参考设计文档。

图 4:NVMeG3-IP 参考设计概览。(图片来源:Design Gateway)

该演示系统旨在对 ZCU102 上的 NVMe SSD 进行数据写入/验证。用户可通过串行控制台控制测试操作。要连接 NVMe SSD 与 ZCU102,就需要使用 AB17-M2FMC 适配器板,如图 5 所示。

图 5:安装在 ZCU102 上的 NVMeG3-IP 演示环境。(图片来源:Design Gateway)

使用 512 GB 的 Samsung 970 Pro 时,在 ZCU102 上运行演示系统的示例测试结果如图 6 所示。

图 6:使用 Samsung 970 PRO S 时,ZCU102 上 NVMe SSD 的读/写性能。(图片来源:Design Gateway)

总结

NVMeG3-IP 内核提供了一个在 ZCU102 评估套件上实现 NVMe SSD 接口的解决方案;同时也为不含 PCIe 集成块的 Xilinx Zynq UltraScale+ MPSoC 器件系列提供了解决方案。NVMeG3-IP 的设计目标是在不使用 CPU 的情况下,以最低的 FPGA 资源使用量实现 NVMe SSD 访问的最高性能。它非常适合不使用 CPU 的高性能 NVMe 存储,能够利用 GTH 收发器实现多个 NVMe SSD 接口,而不受 FPGA 器件上包含的 PCIe 集成模块数量限制。

-

FPGA

+关注

关注

1629文章

21736浏览量

603335 -

存储器

+关注

关注

38文章

7492浏览量

163830 -

SSD

+关注

关注

21文章

2862浏览量

117420

原文标题:在 Xilinx ZCU102 评估套件上实现 NVMe SSD 接口

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

存储技术未来演进:NVMe over Fabrics (NVMeoF)

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍

高性能NVMe主机控制器,Xilinx FPGA PCIe 3

高性能NVMe主机控制器,Xilinx FPGA NVMe Host Accelerator IP

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

Xilinx FPGA NVMe Host Controller IP,NVMe主机控制器

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

在Xilinx ZCU102评估套件上实现NVMe SSD接口

在Xilinx ZCU102评估套件上实现NVMe SSD接口

评论