介 绍

对实时视频流的需求已发展成为一项至关重要的业务需求。视频服务提供商面临着艰难的权衡取舍,因为他们必须在管理基础设施和运营成本的同时,还要为客户提供高质量体验。鉴于视频转换的计算强度,转码不断推升对灵活应变硬件加速的需求。

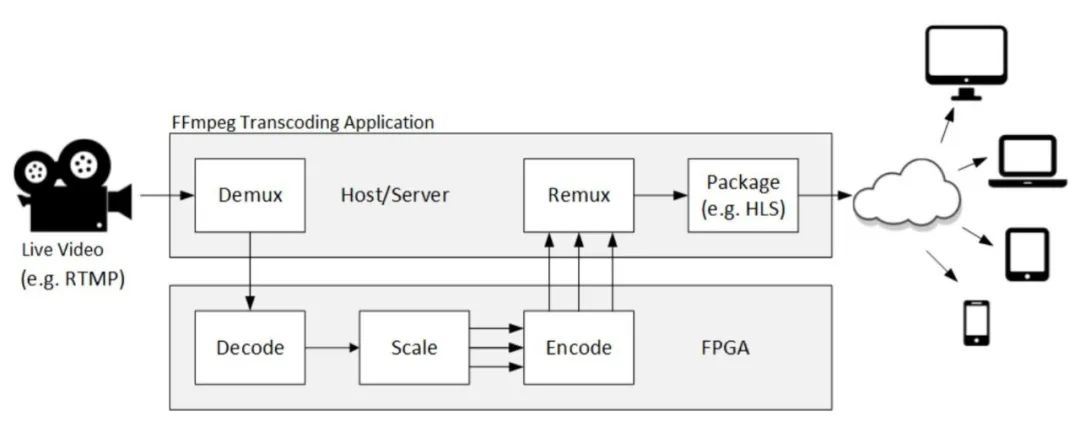

赛灵思已开发出一款高性能视频转码包,无需改变现有基础设施即可为服务提供商提供所需低功耗与优异性能。 此外,该解决方案采用业经验证的非常强大的 FFmpeg 命令行处理模式,方便任何人开发转码应用并将其与现有应用或自有基础设施轻松集成。

产品简介

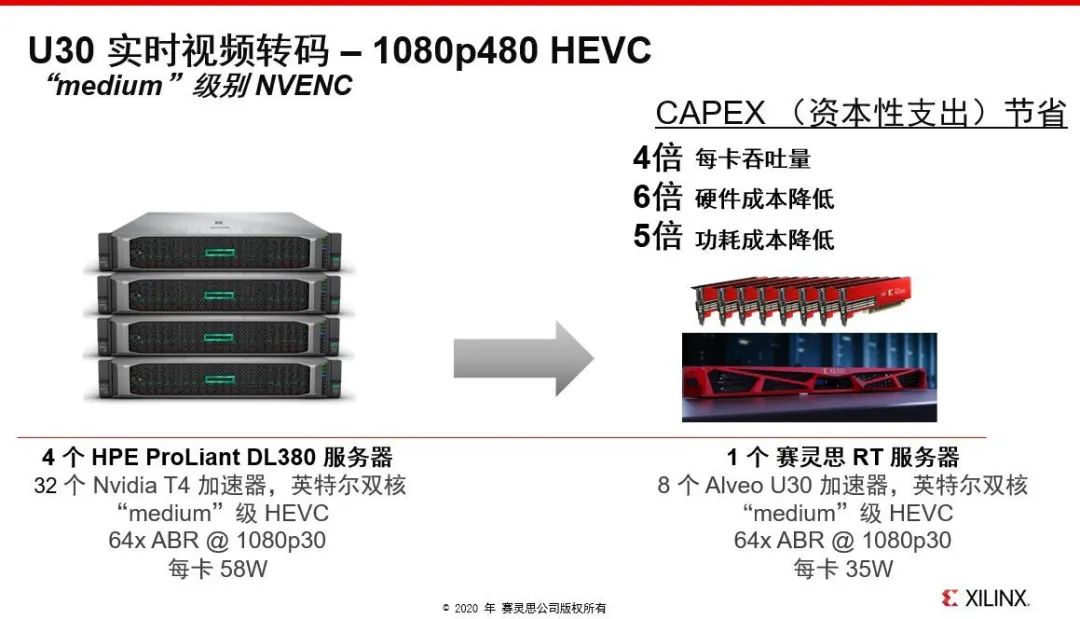

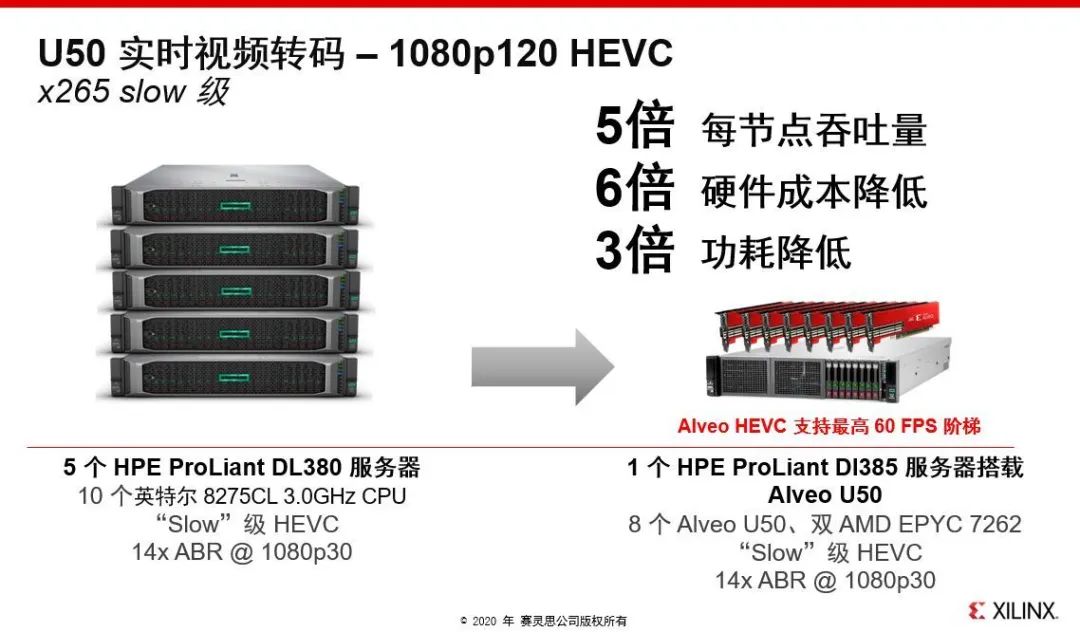

赛灵思面向低比特率(Alveo U50)或高密度应用(Alveo U30)实现最高质量的实时编码,并且以最低的主机 CPU 需求加速编码。另外,在 Alveo U50 和 U30 加速器卡上使用 ABR 阶梯提供 HEVC 和 H.264 编码流以及基于行业标准 FFmpeg 的简单 API。

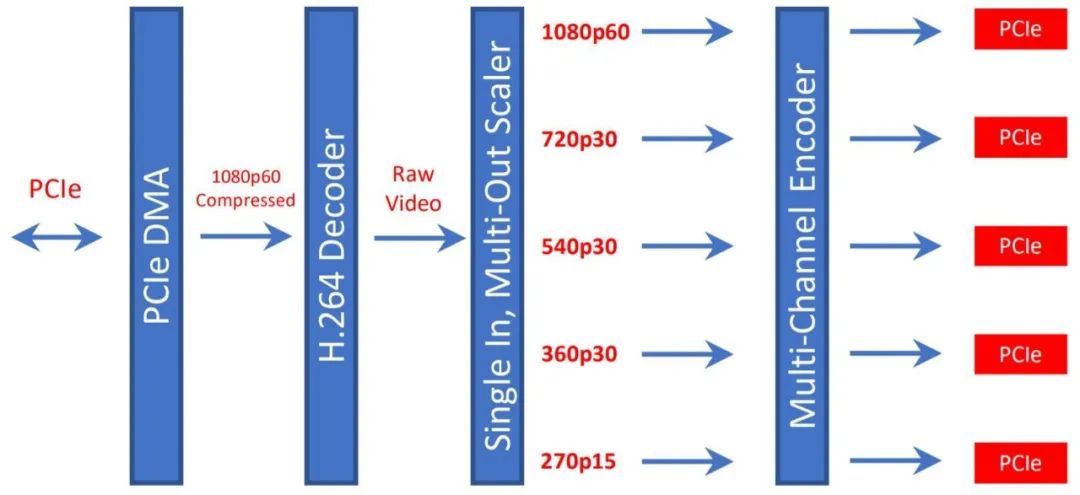

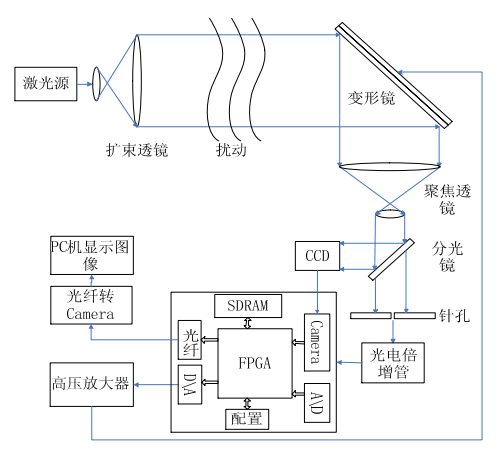

图 1:转码 ABR 阶梯示例

智能分区

赛灵思可以提供系统级最高性能。通过从 CPU 卸载编码任务,确保 CPU 能够为音频和广告插入等其他关键功能提供支持。

通过提供对 FFmpeg API 的支持,客户能够轻松地将多达 8 个 Alveo HHHL U50 或 U30 加速器卡和软件集成到其 1 RU 服务器中。

图 2:从内容生成器将数据流转码到消费端

优势与特性

实时编码可实现媲美 x265“慢速”预置编码的画质

U50 支持面向海量观众广播的最低水平比特率编码

低比特率 = 最低互联网带宽成本

在需要大量编码器时实现高密度编码,如用户生成内容 (UGC)

与 CPU 相比功耗下降 10 倍

与 GPU 相比功耗下降 2 倍

采用高级定标器,提供完整的 ABR 阶梯支持

灵活的多 ABR 阶梯输出,单个实例最多 32 个流

输出质量保持一致,与编码通道数量无关

用于解码器、定标器和编码器的 FFmpeg 插件

HEVC:主 10 配置文件,级别可达 5.1 HD/SD,U50:40 8 位,U30:42 10 位

H.264:主 10 配置文件,级别可达 5.1 HD/SD,U50:40 8 位,U30:40 10 位

恒定比特率 (CBR)、受限 VBR 和 ABR 模式

比特率:100Kb/s 到 40Mb/s 可配置

时延:30ms 到 20s 可配置

片类型:I、P 和 B,提供灵活的开放/闭合 GOP 模式和 GOP 长度

-

视频

+关注

关注

6文章

2012浏览量

75178 -

赛灵思

+关注

关注

33文章

1798浏览量

133638

原文标题:Xilinx 视频实时转码一体机解密系列三:Alveo 加速器卡上的自适应比特率转码

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

选择AMD Alveo V80加速卡的五大理由

如何使用 powerquad 加速器中的一些功能以及 CMSIS 原始实现中的一些功能?

AMD Alveo MA35D媒体加速卡的AMA SDK 1.4.0版本发布

AMD Alveo MA35D加速器:开启大规模交互式流媒体新时代

工业级-专业液晶图形显示加速器RA8889ML3N简介+显示方案选型参考表

边缘计算中的AI加速器类型与应用

航裕电源以大电流技术为国内外超导加速器项目提供优质方案

高压放大器驱动:基于FPGA的SPGD自适应光学控制平台的探索

Arm神经技术是业界首创在 Arm GPU 上增添专用神经加速器的技术,移动设备上实现PC级别的AI图形性能

配电房自适应滤波声纹传感器

基于FPGA LMS算法的自适应滤波器设计

无刷直流电机自适应模糊直接转矩控制研究

CYW43907使用AP功能时是否具有自适应功能?

粒子加速器 —— 科技前沿的核心装置

Alveo加速器卡上的自适应比特率转码

Alveo加速器卡上的自适应比特率转码

评论