实现思路

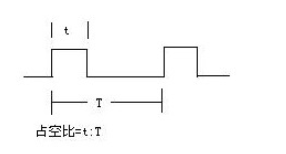

实现方法很简单,使用一个计数器一直计数,然后和两个值进行比较,一个值是高电平时间htime,一个值是周期period,在小于htime期间,输出高电平;大于h_time期间,输出低电平,到达周期period时,计数器清零。

端口说明

◆ nreset:复位信号,低电平复位,输出为0

◆ en:使能信号,高电平使能输出,低电平输出为0,

◆ period:PWM的周期,如主时钟96M,产生4MHz的波形,则period = 96/4 = 24

◆ htime:高电平的时间,如主时钟96M,产生4MHz,占空比25%的波形,则htime = 24 * 0.25 = 6

◆ pwm:PWM波输出

源程序

pwm_gen.v

实际应用

可产生任意占空的PWM波,若主时钟为96MHz。

◆ 产生4MHz,50%占空比:period = 24,h_time = 12;

◆ 产生3KHz,50%占空比:period = 32000,h_time = 16000;

◆ 产生宽度10us,间隔100us的脉冲信号:period = 10560,h_time = 960;

-

PWM

+关注

关注

114文章

5193浏览量

214212 -

Verilog

+关注

关注

28文章

1351浏览量

110154 -

计数器

+关注

关注

32文章

2256浏览量

94702

发布评论请先 登录

相关推荐

使用Verilog实现产生任意占空比PWM波的方法说明

使用Verilog实现产生任意占空比PWM波的方法说明

评论