据报道,台积电在推出3D SoIC后端服务后,还开发了主要用于超级计算AI芯片的InFO_SoW(晶圆上系统)技术,并有望在两年内以InFO(集成式扇出封装技术)衍生的工艺开始量产。此前,台积电已与Cerebras达成合作,InFO衍生的工艺开始量产意味着台积电可能在两年内开始商业化生产专用于超级计算机的AI芯片。

这款从去年推出就备受瞩目的超级AI芯片若进入商业化,机器学习或将迈入新台阶。

制造“超级”AI芯片,面临互连难题

此次台积电计划生产的AI芯片,其实是由一家初创人工智能公司Cerebras Systems在去年推出的世界上最大的半导体芯片,该芯片拥有1.2万亿个晶体管,40万个核心,面积为46225平方毫米,片上内存18G,是目前面积最大芯片英伟达GPU的56.7倍,并多78个计算内核。

根据Cerebras的说法,该芯片是目前唯一的万亿级晶体管晶圆级处理器,基于该芯片推出的CS-1系统可以提供比其他系统更少的空间和功耗的计算性能,相当于标准数据中心机架的三分之一,同时取代对数十万个GPU的需求。

Cerebras之所以推出这款AI芯片,主要是针对深度学习的工作负载。当今人工智能的发展受训练模型所需花费时间的限制,如何缩短训练时间是整个行业共同面临的问题。目前大多数芯片都是在12英寸的硅晶圆上制成的芯片的集合,并在芯片工厂批量加工,但Cerebras芯片却是采用互连的方法将所有内核放在同一块硅晶圆上,使得数据移动快速且低功耗。

另一方面,Cerebras将所需的数据存储在处理器芯片上而非单独的存储芯片上,这也就意味着,该款芯片能将原本需要几个月的训练缩短到几分钟,推理能力也更强。

所有这些改进,都指向制造出尽可能大的芯片。但芯片越大,可能出现的缺陷也就越多。这就要求在制造该款芯片的过程中,尽可能解决一些难题。例如,光刻工具是旨在将其特定的图案一遍又一遍地投射到较小的矩形框内,由于在晶圆的不同位置刻蚀不同图案的成本和难度,限制了在同一个晶圆上构建不同的系统。

对于这款超级计算芯片而言,最大的挑战在于芯片互连。这要求芯片制造商能够在每个芯片周围留下空白硅的窄边,这一窄边称为划线。基于这一难题,Cerebras与台积电展开了合作。

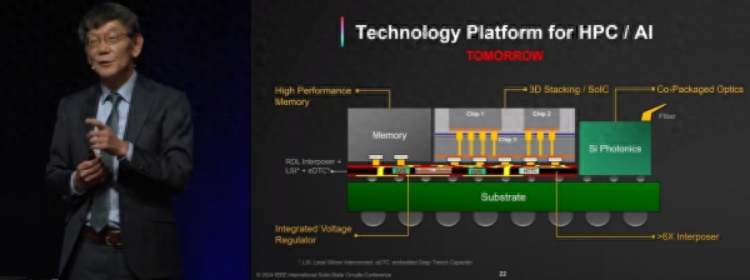

台积电先进封装技术有望实现“超级”AI芯片量产

在台积电与Cerebras的合作中,其集成式扇出封装技术(InFO)发挥着重要作用。

集成式扇出封装技术到底是什么呢?

从技术特点来看,先进的晶圆封装技术分为扇入型(Fat-in)和扇出型(Fan-out)两种,传统的晶圆级封装多采用扇入型结构,完成再布线并形成与外部互连的焊球,主要应用于I/O引脚数量较少的集成电路芯片。但随着终端用户对产品性能的要求日趋增多,摩尔定律下工艺节点不断推进,满足要求的芯片需要更多的I/O引脚,传统扇入型封装已不符合要求,扇出型晶圆级封装方式应运而生。

扇出型封装突破I/O引出端数目的限制,通过晶圆重构增加单个封装体面积,之后应用晶圆级封装的先进制造工艺完成多层再布线和凸点制备,切割分离后得到能够与外部带性能互连的封装体。

不同厂商的技术各有差异,就台积电而言,在扇出型晶圆封装领域开发出了集成式扇出封装技术(InFO),并于2014年宣布量产。台积电采用的扇出型封装技术,舍弃了原本扇入型封装所使用的印刷电路版,直接将NAND、逻辑IC、RF射频等器件嵌入晶圆,这就意味着,依靠扇出型封装技术所得到的芯片厚度和成本都减少。

根据台积电的说法,其扇出型封装技术使芯片厚度减少20%,成本降低30%,同时互连功耗降低15%。以较小的功耗实现巨大的连接性,这正是超级计算AI芯片所需解决的问题。

尽管扇出型封装技术比扇入型封装先进,但考虑到安全性等因素,目前市场上只有手机应用处理器使用扇出型封装,CPU和逻辑IC等依然使用扇入型封装。基于其成本与厚度优势,未来,可能会有越来越多的芯片采用扇出型封装技术。此次台积电与Cerebras的合作,也为扇出型封装技术开拓了新市场。

小结

预计Cerebras晶圆的成本为200万美元,价格昂贵,这一AI芯片就算实现量产也无法在短时间内大量普及,但其学习能力和推理能力确实值得我们期待,这似乎是赛博时代机器走向人类的一大步,如同我们对5G世界的想象一样,当机器学习变得更加容易,我们的世界将会是什么样子?

责任编辑:tzh

-

台积电

+关注

关注

44文章

5651浏览量

166654 -

人工智能

+关注

关注

1792文章

47387浏览量

238893 -

AI芯片

+关注

关注

17文章

1889浏览量

35093

发布评论请先 登录

相关推荐

台积电推出的超级计算AI芯片进入商业化,机器学习将迈入新台阶

台积电推出的超级计算AI芯片进入商业化,机器学习将迈入新台阶

评论