后摩尔时代 Chiplet 技术的演进与挑战

0 引言

自戈登•摩尔(Gordon Moore)提出,半导体芯片上集成的晶体管数量每 18~24 个月增加一倍。在过去五十多年里,集成电路制造工艺技术、封装与测试技术、设计方法学和 EDA 工具等微电子相关技术跟随摩尔定律的步伐始终保持着快速的发展。2019 年进入 7 nm 工艺制程。芯片经历了从小规模集成电路(SSI)、中规模集成电路(MSI)、大规模集成电路(LSI)、超大规模集成电路(VLSI)到甚大规模集成电路(ULSI)、最大规模集成电路(ELSI)阶段。近十年来,随着信息通信业,以及以机器学习、大数据为代表的新兴信息技术的飞速发展,片上系统 SoC(System on Chip)在提高产品性能、增加可靠性的同时,大幅降低了开发成本,缩短了开发周期,是半导体技术发展历程中的一个重大里程碑。半导体工艺进入 28 nm 节点后,新制程的研发成本呈指数级增长,芯片工艺提升越来越困难,片上系统 SoC 设计面临诸多挑战。异构/异质集成激发了多芯片封装(MCP)/多芯片模组(MCM)的发展,有望在当前芯片产业基础上催生新的产业生态系统和新的商业模式[1]。半导体业进入后摩尔时代。

最近,Chiplet(小芯片、芯片粒)技术热了起来,从美国国防高级研究计划局 DARPA(Defense Advanced Research Projects Agency)的 CHIPS(Common Heterogeneous Integration and IP Reuse Strategies,通用异构集成及知识产权复用策略)项目到 Intel的 Foveros 技术、ODSA(Open Domain-Specific Architecture)开放架构等,都把 Chiplet 看成是未来芯片的重要基础技术。本文试着从半导体工艺制程提升的难度、SoC 研发所面临的问题出发,探讨 Chiplet 的优势、关键技术及发展趋势,以期对行业人员了解 Chiplet 技术提供一定帮助。

1 片上系统 SoC 面临的挑战

SoC 起源于 1990 年代中期,随着半导体技术的高速发展,异构多核的 SoC 成为集成电路 IC 设计的主流趋势,是数字集成电路的主要实现形式。文献[2-8]对片上多核系统从同构到异构的演进过程进行了详细的阐述。

1.1 SoC 设计难度加大

SoC 是以超深亚微米工艺技术和知识产权核 IP 复用技术为支撑,将系统所需的处理器、存储器、模拟电路模块、数模混合信号模块以及片上可编程逻辑等高度集成到一颗芯片中,以此缩小体积,增加功能,提高性能和可靠性,且还大幅缩短产品上市时间、降低开发成本。

基于 IP 核的 SoC 设计,首先要面对的是 IP 核的互联问题。IP 的集成度越来越高,种类和复杂度急剧加大,IP 核间的互联缺乏通用接口,内部互联方式复杂化、多样化,不同厂商 IP 核之间的互联几乎不可能。片上网络成为片上系统内部互联的主流方式,即 IP 核之间通过网络结构来实现数据的传输。这种结构虽然可解决通用总线的问题,但还需建立高效的路由算法[4]。

基于 IP 核的 SoC 设计,要保证 IP 核的可重用性。首先要提高 IP 核代码的通用性,使设计能够方便地配置、裁剪和扩充。其次,IP 核应该能被方便地集成,这需要考虑 IP 核测试和低功耗技术的可重用性。对于处理器 IP 核,应考虑调试和接口的可重用性[6]。

总的说来,SoC 设计的关键技术主要包括 IP 可复用技术、总线架构技术、软硬件协同设计、SoC 验证、可靠性可测性设计、低功耗设计、超深亚微米电路实现技术等。SoC 所需要的仿真验证时间越来越长。高性能 SoC 采用更先进的工艺技术,使得功率收敛和时序收敛的问题变得更加突出;越来越高的集成度需要庞大的 SoC 团队软硬件协同开发,有可能进一步拉低芯片良率,盈利风险明显升高。

随着 SoC 应用的不断普及,市场需要更加广泛的 SoC 设计。SoC 芯片提供商不仅要拓展系统内部设计能力,还要直接交付开发 SoC 的设计条件和方法,为客户提供完整的解决方案。

1.2 新工艺制程的研发困难

SoC 芯片性能的提升与芯片的制造工艺息息相关。随着半导体工艺的进步,在同等面积大小的区域里,挤进越来越多的硅电路,漏电流增加、散热问题大、时钟频率增长减慢等问题难以解决,芯片设计的难度和复杂度也在进一步增加。图 1 显示了随着设计迁移到高级工艺节点,开发成本的快速增长。例如 28 nm 节点上开发芯片需要 5 130 万美元投入;16 nm 节点需要 1 亿美元;在 7 nm 工艺节点上的成本超过 2.5 亿美元。目前,市场上对 SoC 的需求是高性能、多品种,采用单片 IC 模式开发和实现 SoC,新工艺制程开发的 NRE(Non-Recurring Engineering)成本呈指数级增长且开发周期很长,增加的成本不能被摊薄,大多数企业不能接受。

芯片制造的过程极其复杂,影响良率的因素也非常多,其中影响最大的是晶圆尺寸、环境因素和技术成熟度三种因素。晶圆是圆形的,同时制造数量很多的芯片,一般中心区域的良率较高,而边缘区良率较低。而且,不同的芯片有不同的大小。大的 Soc 芯片,有可能一片晶圆上只有几百个甚至几十个芯片;小的芯片,一个晶圆可以有成千上万颗。环境因素,如尘埃、湿度、温度和光照亮度,对晶圆良率、Die 良率和封测良率都会产生一定影响,因此芯片制造和封测都需要在超净的工作环境中进行。新工艺刚出来的时候良率会很低,随着生产的进行和导致低良率的因素被发现和改进,技术不断成熟,则良率就会不断地被提升。提升良率是半导体公司孜孜以求的目标。

图 2 所示的芯片良率数学模型的曲线可以看出,芯片的良率与芯片的面积有关。随着芯片面积增大,芯片良率会下降。一方面先进半导体工艺很昂贵,另一方面良率又随着面积下降,两相结合进一步推高芯片的成本。

2 Chiplet 的起源

Chiplet(小芯片、芯片粒、裸芯片)由于面积较小,因此其良率较好。基于裸芯片的 Chiplet 模式,也许可作为一种解方,带给从上游 IC 设计、EDA 工具、制造工艺、先进封测等各个产业链环节颠覆式的改变,是 IC 业继续发展最有效的手段,后摩尔定律时代确已降临。

异构集成 Chiplet 系统中,产品的不同组件在独立的裸片上设计和实现;不同的裸片可以使用不同的工艺节点制造,甚至可以由不同的供应商提供。第三方 Chiplet 可以减少设计时间和成本。异构集成 Chiplet 系统提供了一种新的设计方案。

2.1 Chiplet 发展的推动力

由于 Chiplet 面积较小,使用 Chiplet 在封装内集成系统的办法相比直接设计一块大 SoC 的良率和成本有较大的改善。因此,良率和成本成为发展 Chiplet 的第一推动力。

发展 Chiplet 的另一个推动力就是异构计算和集成,是指器件封装内部的异构集成。使用小芯片不需要为后续每个半导体制程节点重新设计每个小芯片,芯片厂商可以针对特定应用设计专用的高性能芯片粒,并且和其他通用芯片粒(例如内存,高速串行接口等)集成在封装里,从而实现异构计算和集成以提升系统性能。

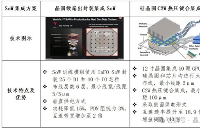

2.2 Chiplet 芯片与单片 SoC 等的比较

Chiplet 其实就是一颗商品化的、具有一定功能特征(如 USB、存储器)的裸芯片(Die)。Chiplet 模式下,首先将需要实现的复杂功能进行分解,然后开发出多种具有单一特定功能,可相互进行模块化组装的裸芯片,如实现高性能计算、信号处理、数据存储、数据传输等功能,并以此为基础,建立一个 Chiplet 的芯片网络,最后通过 SiP(System in Package)封装技术形成一个完整的芯片。所以 Chiplet 也是一种 IP,但它是以芯片裸片的形式提供,而不是像SoC以软件形式提供[5]。

Chiplet 解决了当前芯片技术发展的难题,大型最先进工艺的芯片,或者对性能、功耗和尺寸有超高要求,而价值比较高的芯片,适合做 Chiplet 的设计。另外,如果产品线复杂,每一个产品的量不够大,Chiplet 的重用性可以满足市场对高性能、多样化芯片的巨大需求。Chiplet 芯片与单片 SoC 的比较(表 1)。

3 Chiplet 需要解决的关键技术

Chiplet 面临着诸多挑战,例如接口标准化、接口间巨大的数据量造成裸芯片和裸芯片间互联所产生的大功耗,以及高成本所带来的未来大规模化应用等课题。如何去划分、定义这些小芯片的功能、接口、互联协议等,Chiplet 的接口技术或封装尚缺乏统一的标准。

3.1 die-to-die 通信技术

异构集成 Chiplet 方案需要在单个 MCM (Multichip Module)中实现从 die-to-die 的通信。目前 die-to-die 的通信有如下几种技术:(1)传统中长距离 SerDes 协议,如 PCI-Express、以太网等。(2)XSR or SiP SerDes[5]。基于传统的SerDes体系结构,专门为die-to-die通信而构建,可在SiP内实现极高带宽的链接。(3)USR Femto SerDes 协议。USR Femto SerDes协议专门为 die-to-die 通信而优化,在能效方面都有较大的提高,可使用现有的封装技术,带宽和成本比较均衡。(4)并行接口:高带宽内存(HBM),高级接口总线(AIB),电线束(BoW)接口。BoW 是类似于 DDR 的内存接口。AIB/HBM 都实现了相对较高的带宽密度,但也需要相对复杂的硅基互联技术。

几种协议的比较:上述 die-to-die 通信技术各有优缺点,需要根据应用进行选择。并行接口如 BoW、AIB、HBM 提供低功耗、低延迟和高带宽,但是裸片之间需要连接许多线路,只有使用昂贵的插接器或桥接技术才能满足布线要求,成本较高。相对于并行接口,SerDes 可提供同样的带宽,但能效不高,比片上网络延迟更大。系统设计人员在选择 die-to-die 的互联之前,应考虑与应用相关的所有要求。图 3 总结了每个接口技术在各种相关参数上的相对优势和劣势。

3.2 多裸片封装技术

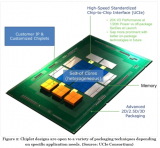

在产品和市场需求的驱动下,实现了更高密度的集成,封装技术在过去几年经历了革命性的转变。对封装的要求已经从单纯地实现与外部世界的电气和机械连接,发展到现在支持多芯片封装中不同芯片之间的多种接口技术。

(1)多 Chiplet 封装技术。将多个芯片和/或封装集成到一个 MCM 中导致了更大的封装尺寸,也导致信号线和空间有限。芯片之间的接口影响封装技术的选择,特别是需要集成多个芯片的基板。多芯片设计的封装技术需要考虑以下因素:chip-to-chip 接口、成本限制和性能要求、多 Chiplet 封装的总尺寸。

(2)并行接口集成封装。并行接口,如 AIB、HBM,或者 BoW 接口,对封装技术有严格的需求。BoW 的信号速度通常比串行解决方案慢一些,但芯片之间的互联更多,根据芯片之间需要支持的带宽大小,可以选择不同的封装技术。

(3)SerDes 集成封装。USR SerDes 互联技术的发展大大减少了半导体芯片之间通信所需的 I/O 总数,允许有机基质提供裸片之间的互联。

4 结语

Chiplet 技术的发展需要生态系统的支持。Chiplet 生态系统不仅需要建立起标准化的开放接口,同时也要求在晶圆测试、发热管理以及新型商业模式等领域实现技术共同进步,需要 EDA 工具提供商、芯片提供商、封测提供商都要提供全面支持。Chiplet、OSDA 将会大大降低芯片设计门槛,为芯片行业带来新的变革,这也是中国半导体业发展的大好机遇。

-

集成电路

+关注

关注

5388文章

11547浏览量

361837 -

半导体

+关注

关注

334文章

27367浏览量

218774 -

chiplet

+关注

关注

6文章

432浏览量

12595

原文标题:后摩尔时代 Chiplet 技术的演进与挑战

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

对话郝沁汾:牵头制定中国与IEEE Chiplet技术标准,终极目标“让天下没有难设计的芯片”

高带宽Chiplet互连的技术、挑战与解决方案

UCIe规范引领Chiplet技术革新,新思科技发布40G UCIe IP解决方案

国产半导体新希望:Chiplet技术助力“弯道超车”!

剖析 Chiplet 时代的布局规划演进

奇异摩尔携手SEMiBAY Talk 邀您畅谈互联与计算

什么是Chiplet技术?

Chiplet技术对英特尔和台积电有哪些影响呢?

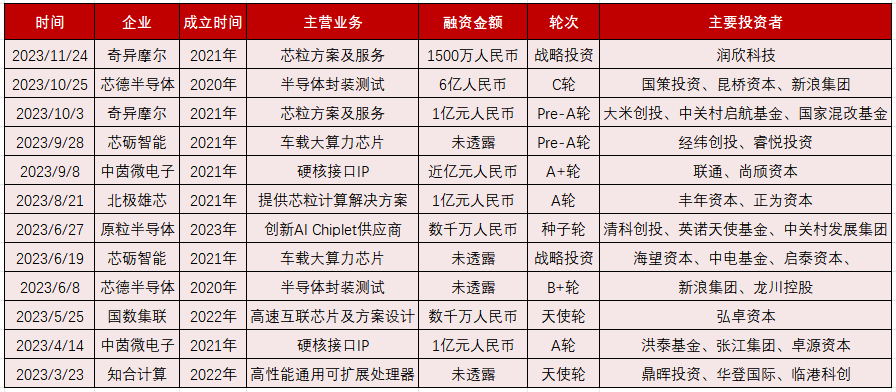

2023年Chiplet发展进入新阶段,半导体封测、IP企业多次融资

后摩尔时代Chiplet技术的演进与挑战

后摩尔时代Chiplet技术的演进与挑战

评论