DDR5 JEDEC最近已定稿,从各类介绍文章看基本集中在一些新特性描述方面,极少涉及到技术细节,与海报效果差不多。为了深入了解DDR5的各方面信息,“翻墙”、“找网友”、“找前同事”各种方法都用了,最后发现还是找不到最完美的JEDEC文件,很多参数在【TBD】的状态,经过对这些零碎材料的分析并结合自身的经验,给出在仿真DDR5新特性时采取何种策略或提出相应建议。 会发现,前面掌握的DDRx基础知识及方法大部分可以承传到DDR5仿真设计中,当然要把包含DDR5信号的产品设计好,还需要花更多的时间深入学习并根据实际的情况处理。

如下从几方面对DDR5进行阐述:

1 DDR5颗粒容量

DDR5单Die可以做到最大容量为64Gbit,单DIMM条容量达到2T。这个数据对于平时需要使用大内存仿真或平面设计的同学绝对是个好消息。

图 1. Dimm与Die的容量

2 DDR5封装

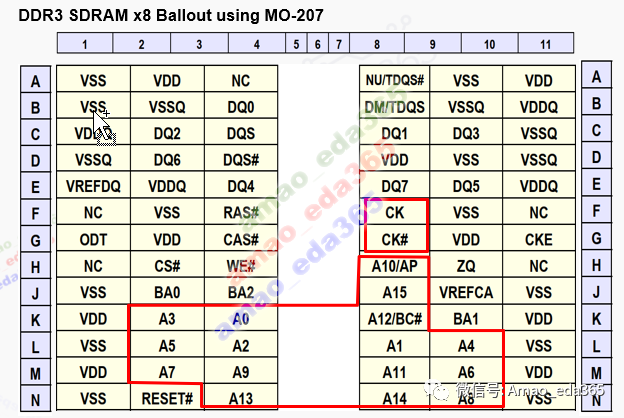

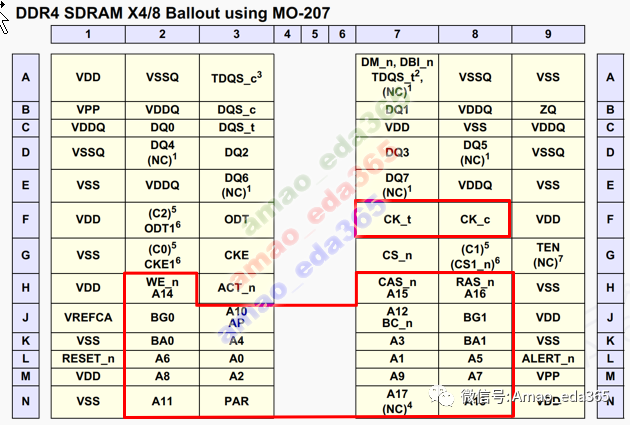

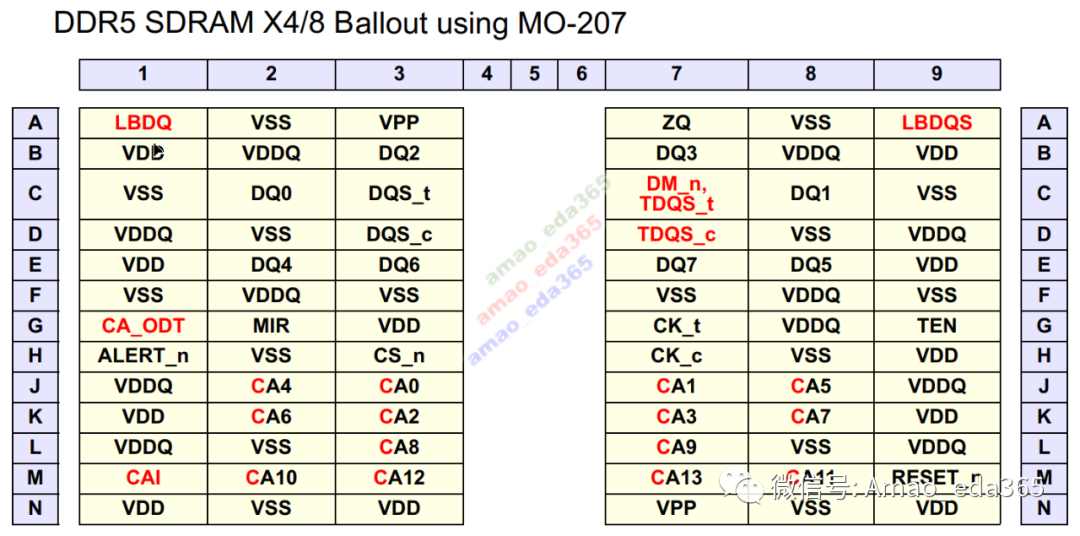

DDR3-5的封装比较

图 2. DDR3 PINMAP

图 3. DDR4 PINMAP

图 4. DDR5 PINMAP

从DDR3-DDR5 地址、控制、命令数据、时钟、电源的管脚总体摆放位置只作了小调整,而这个小调整按流程需要在DIE-PKG-PCB间进行Co-Design,以保证信号SI与电源的噪声,这是协同设计的过程。

一般工程师是在PINMAP固定的条件下进行板级的布线设计及仿真,较少有机会深入到芯片Padorder层面进行整体考虑,这与国内芯片生态及平台目前的状态有极大的关系。

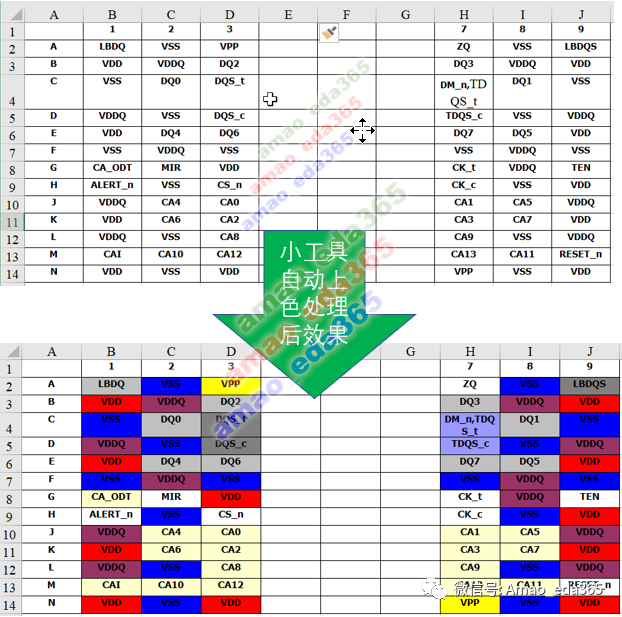

Pinmap设计时一般会给不同种类的信号总线赋上不同的颜色以提高工作效率及便于Reviewed。作者开发了相应自动上色小工具处理,高效快速,这里不作深入,有需要的读者可以到作者的公众号上自行下载。

如:小工具对DDDR5 PINMAP自动分类上色的效果图

经过上色后,DQ/ADDRESS/VDD等不同信号的分布状况一目了然,非常方便信号的检查。

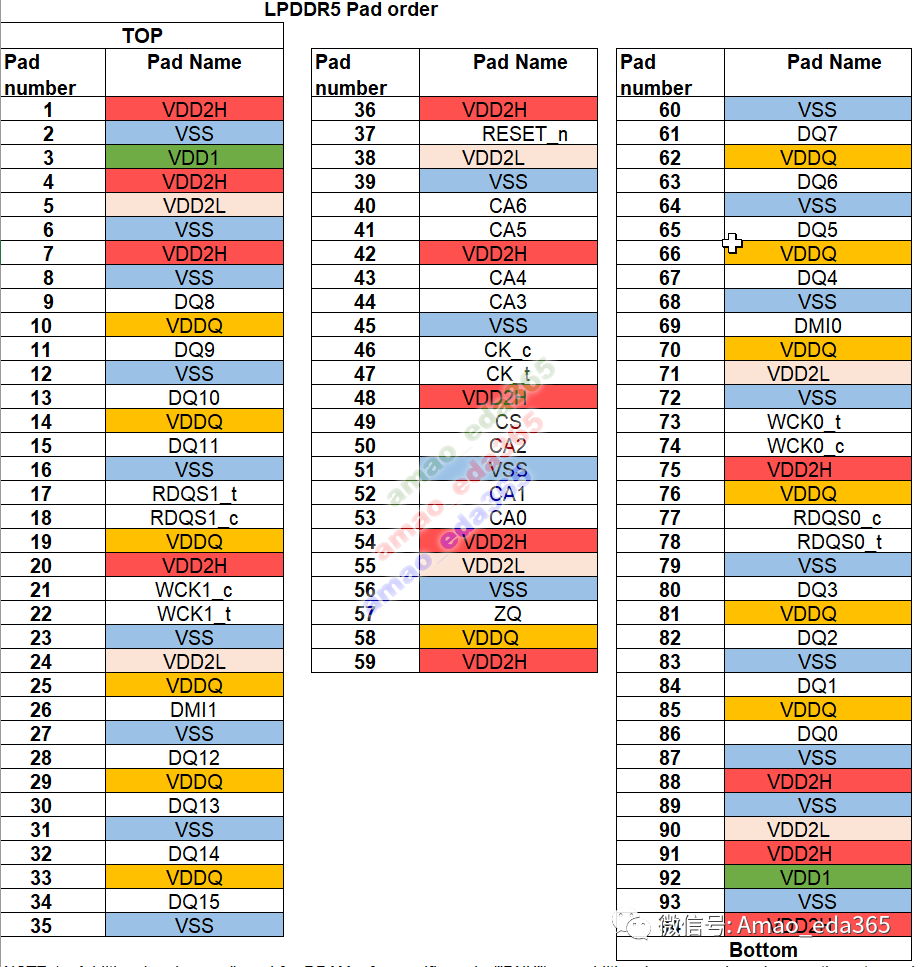

3 LPDDR5芯片管脚的摆放设计

芯片Padorder一般需如何摆放?可以参考下面LPDDR5颗粒的样例,从下图中的芯片管脚摆放可以看到,对于数据信号及时钟等速率较高的情况,要求每个pad必须要与电源/地相邻,在设计时怎样使整个芯片的PAD使用数量最少,则与设计者的水平有很大的关系。

图 5. LPDDR5芯片PADORDER

4 Dimm条分析

Dimm结构的改变应是本次从外观外看改动最大的地方,每个DIMM提供两个独立的32位数据通道(考虑ECC时为40位),两个7位CA总线,而不是DDR4单个24位CA总线,每个通道的变化及与DDR4的对比如下:

具体管脚的调整及摆放需要对DIMM条建模仿真以确定(下月我公开课中会对具体的建模过程及仿真的效果比较有详细的讲解)

图 6. DDR5 DMIMM

图 7. DDR4 DIMM

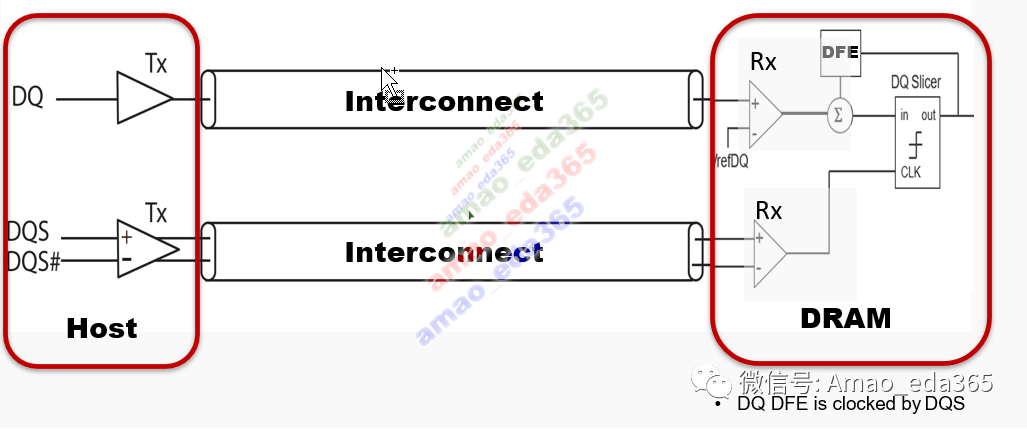

5 DEF

DFE(Decision Feedback Equalization:决策反馈均衡)的引入是DDR5的另一个亮点,DFE是一种通过使用来自内存总线接收器的反馈来提供更好的均衡效果及排除 inter-symbol 干扰的方法。均衡可以使DDR 5内存总线传输速率更高。还添加了新的改良训练模式,以帮助DIMM和控制器补偿内存总线上的微小时序差异 。

DFE的引入使仿真变得更简单,优化通过软件工具自动完成,很多复杂的设置体现在底层软件上,而应用层面则是越来越简单了。如下图的数据接收端引入的均衡示图。

图 8. DDR5 DQ DFE均衡

6 电压调节器上Dimm

由于工作电压降低,对纹波影响要求更严格,电压调节原来在主板上,这样的路径较长,中间还会经Dimm插座,对电源的影响较大,而现的Dimm条设计则是把电压调节器移到DIMM条上,如下图。

图9. DDR5电压调节器移到Dimm条上

DIMM上的电源PDN设计与仿真方法可以参考《信号、电源完整性仿真设计与高速产品应用实例》中PowerAC与PowerDC仿真等章节内容,这些方法对于DDR5的应用环境完全可以胜任。Dimm条仿真PowerDC/AC的效果如下图。

图 10. DIMM上IR DROP仿真效果

结论

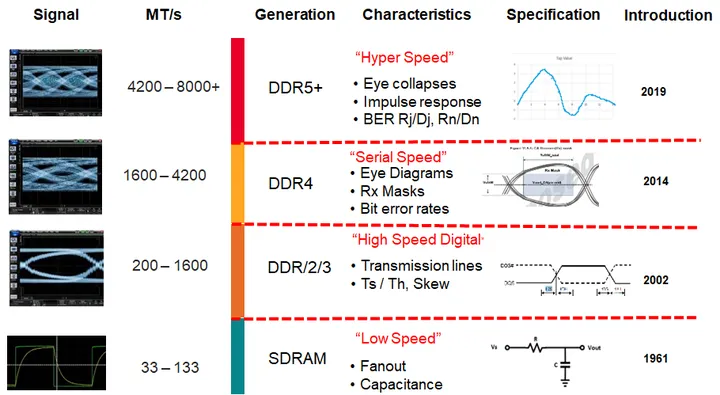

DDR5的出现,没有太多的惊喜,也没有太多的失望,从仿真的角度看,DDR4/3的仿真技能及思路大部分都可以继承,在实际DDR5仿真过程中需要具体问题具体分析了。

-

pcb

+关注

关注

4316文章

22993浏览量

396162 -

封装

+关注

关注

126文章

7771浏览量

142705 -

DDR5

+关注

关注

1文章

419浏览量

24092

原文标题:DDR5分析与仿真应对策略

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DDR5内存的工作原理详解 DDR5和DDR4的主要区别

揭秘DDR5的读写分离技术奥秘

Introspect DDR5/LPDDR5总线协议分析仪

DDR5内存条上的时钟走线

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

谈谈DDR5技术规格的那些事

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?

DDR6和DDR5内存的区别有多大?怎么选择更好?

lpddr5时序比ddr5慢多少

澜起科技宣布推出DDR5第四子代寄存时钟驱动器芯片(DDR5 RCD04)

DDR5接收机一致性表征和测试

ddr5为什么能跑得那么稳呢

从几方面对DDR5进行阐述

从几方面对DDR5进行阐述

评论