引言

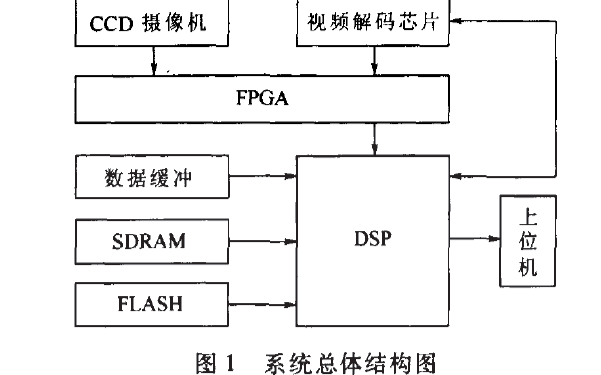

随着科学技术的发展和社会发展应用需求,人们对视频图像采集处理高清化,传输实时化和控制智能化的要求越来越高。高清视频图像在军事、科研、安防、工业生产、医疗卫生等领域得到了更为广泛的应用。 特别在安防行业,现有系统由于技术、成本和传输距离的原因,传输带宽都不高,直接实时传输高清视频图像难以实现,但是某些关键时刻或者特殊场景却需要高清晰度、高分辨率的图像进行细节的分析处理,便于智能化的应用。本文为了解决这一个矛盾的需求,提出了在视频监控系统的前端——图像采集和处理将采集到的原始高清图像数据分成两路同时进行处理的思想:一路按照传统的处理方法压缩处理转为标清视频流传输,实现监控的实时化;另一路数据由外部扩展SDRAM缓存,DSP实时读取缓存数据进行智能分析处理,根据分析处理结果决定是否传输高清图像或者结果。基于不同处理芯片在图像处理各层次应用有不同的针对性,合理分配硬件资源及算法,能够显著提高系统整体性能。本文采用FPGA+DSP技术实现高清图像采集和处理,并在硬件层面将数据分路处理。

1 系统结构及原理

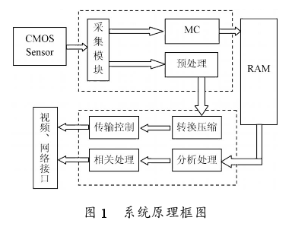

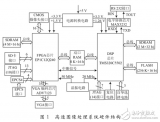

本文设计的硬件系统,就是利用FPGA和DSP对高分辨率CMOS数字图像传感器OV5642进行图像采集和处理。系统完成对 FPGA,DSP和OV5642芯片进行初始化。FPGA对OV5642进行全分辨率的数据采集。FPGA将采集到的图像数据成两路处理,一路直接原始高清数据传输外部SDRAM缓存,由DSP读取缓存数据进行智能分析处理;另一路由FPGA进行硬件预处理,将原始高清图像转换为合适的分辨率,送到DSP 片内进行格式转换、压缩等处理后传输到外部接口。DSP根据分析处理结果和设置阈值条件,决定是否对高清图像数据进行传输。需要传输的图像帧融入数据流中传输。外部扩展的输出接口可以将经过系统处理的数据流传输到本地监控或者远程监控。系统原理框图如图1所示。

在高清实时图像采集处理中,图像采集的速度高,低层的预处理中要处理的数据量大,对处理速度要求高,但运算结构相对比较简单,适合用兼顾速度及灵活性的 FPGA进行硬件实现。高层的处理算法的特点是处理的数据量较低层算法少,但算法的结构复杂,适合用运算速度高、寻址方式灵活、通信机制强的DSP芯片来实现。DSP+FPGA架构的最大特点是结构灵活,有较强的通用性,适合于模块化设计,从而能够提高算法效率,同时其开发周期短,系统易于维护和升级,适合于实时视频图像处理。 在本设计中充分考虑到FPGA和DSP在图像采集处理各层次应用有着不同的优势,采用FPGA+DSP结构,通过合理的硬件资源分配及算法处理,实现了高清图像采集和实时处理。在FPGA内设计采集模块和预处理模块,充分利用FPGA时钟频率高,内部延时小,运行速度快,全部控制逻辑由硬件完成的特点,主要完成图像数据采集、数据分路和图像缩放预处理。通过FPGA内模块间协调,在硬件层面完成数据的分路。在

DSP内则是利用DSP运算速度快、寻址方式灵活、通信机制强大等特点,主要完成系统配置、图像格式转化、压缩处理以及图像的智能分析处理、传输接口配置等。

2 系统硬件设计

2.1 图像采集模块设计

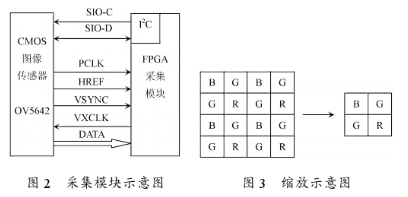

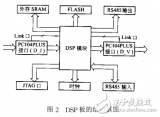

图像采集模块主要包括传感器工作模式配置、图像采集控制和数据传输。整个模块的功能示意图如图2所示。FPGA片内模拟I2C控制器,将COMS图像传感器OV5642初始化。OV5642在外部时钟VXCLK作用下,输出Bayer RGB格式图像数据和同步时钟。FPGA内部设计的采集控制器在PCLK,HREF,VSYNC同步时钟作用下,产生相应控制读写信号,进行数据传输采集。[page]

通过SCCB总线设置OV5642相关的内部控制寄存器,实现对OV5642初始化,从而确定输出分辨率、开窗位置、曝光时间等。SCCB总线是Omni Vision公司特有的一种三线串行摄像控制总线。三线中的SCCB_E为片选信号线,本文中只有OV5642一个从设备,所以SCCB_E直接置低,始终选中OV5642。在模拟I2C控制器控制下,第一步,SIO_D线传输OV5642的器件地址加上写操作标识,确定操作的器件和注明是写操作;第二步,传输内部的目标寄存器的地址;第三步,传输要设置的数据并写入到对应的寄存器中,完成寄存器配置。

采集控制器是在FPGA设置的一个时序逻辑控制器,主要产生OV5642需要的外部时钟XVCLK和根据OV5642输出的像素时钟PCLK,行参考时钟 HREF,帧同步时钟VSYNC产生读写控制存储信号。通过对PCLK,HREF,VSYNC时钟的计数,可以得到写满一行或者一帧信号,为后继处理提供同步时钟和使能信号。

2.2 预处理模块设计

预处理模块主要是利用FPGA可编程性和内部丰富的硬件资源,在硬件层面选择性的传输数据,将高清图像的分辨率降低。FPGA采集到的原始图像数据格式为Bayer RGB格式,每个像素点只有一种颜色分量,其余颜色分量可以通过插值算法恢复。如图3左边所示就是4×4的Bayer RGB格式。为了保持数据格式一致性,需要每隔2行或者每隔2列选择一个像素传输。本设计采用在行方向上每隔2列选择传输一个像素点,在列方向上每隔2行选择传输一个像素点。这样能将图像分辨率降低,达到缩放目的,如图3所示。

图像数据是逐个像素逐行串行传输的,在缩放处理上,利用PCLK,HREF和VSYNC信号时序关系产生计数脉冲和使能信号。在行方向上,选择传输一个像素点数据后,利用PCLK作为列计数脉冲,每过两个脉冲(隔两个像素点)再选择传输一个像素点数据,一直循环选择,直到处理完一行图像数据。这时根据 HREF信号产生列计数器清零信号,将列计数器清零,暂停数据选通。在列方向上,由行计数器利用HREF信号进行计数,每过两个计数脉冲(隔两行图像数据),重复行方向上的处理方式对当前行进行选择数据传输。如此循环处理,直到一帧图像数据处理完毕。每帧图像处理完毕信号是由VSYNC信号产生的。同时,VSYNC信号对行计数和列计数器清零,直到新一帧图像到达,计数器重新计数,开始新的一帧图像缩放处理。通过这样的缩放处理,可以将2 592×1 944的图像降为648×486的图像,数据量得到减少。预处理模块将缩放后图像传输到DSP中处理。

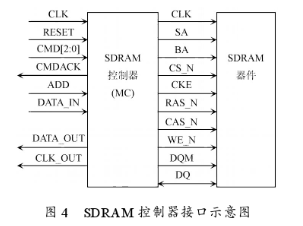

2.3 SDRAM控制器(MC)的设计

SDRAM控制器模块是FPGA内部设计的模块,用于将图像数据传输到外部存储器暂存。图4为FPGA设计的顶层模块示意图。在MC控制器的内部,采用状态机来实现数据读写、设置模式寄存器和刷新等操作的命令译码,产生输出给SDRlAM芯片的RAS/CAS/WE/CS/DQM等信号。已经初始化的SDRAM在得到了RAS,CAS,WE的值后开始执行相应的命令。在对SDRAM进行读、写操作过程中,要先进行页激活操作,保证存储单元是打开的,再通过预充电命令实现来关闭存储单元。在进行写操作时,内部的列地址和数据都会被寄存,而进行读操作时,内部地址被寄存,数据的读取则发生在CAS延迟时间(通常为1~3个时钟周期)后。SDRAM顺次的进行读、写操作后,当达到突发长度或者突发终止指令出现时,SDRAM控制器将终止其操作。

通过SDRAM控制器模块的控制传输,可以将采集到图像数据实时的传输到存储器件暂存。采用控制器模式具有一定的通用性,DSP可以通过控制器模块直接读取存储图像数据进行分析处理。

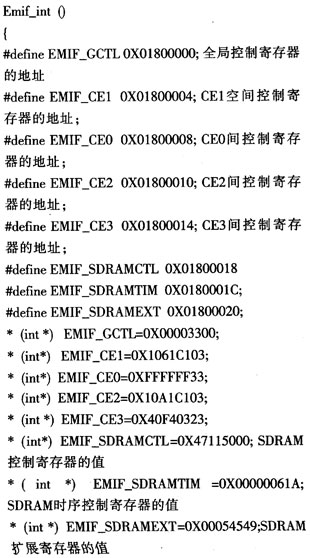

2.4 DSP子系统

DSP接收预处理模块输出的降了分辨率的Bayer RGB格式数据到数据缓存器,再将缓存数据传到片内preview engine模块进行格式转换,将Bayer RGB格式图像数据转换为YUV422格式数据。DSP对YUV422格式数据进行压缩处理后送到输出端口输出。 DSP通过SDRAM控制器读取SDRAM中的高清原始数据,进行一些智能化分析处理,如识别、验证等。根据处理结果和系统设定的阈值如光强变化、动静变化等,决定是否对当前或者前几帧图像进行传输。高清图像数据传输由DSP通过一定的相关处理结合到输出数据流中传输到后端,由后端提取出高清原始数据,进行各种应用。

3 结语

采用了FPGA和DSP技术,设计了对CMOS图像传感器进行图像采集和处理系统。该系统直接对CMOS传感器进行原始数据的采集,为后继处理的灵活性和应用的多样性做好数据基础。在FPGA中将数据分成两路,一路作为原始数据暂存到SDRAM,一路按照传统的处理、输出。这样既能实现了传统图像采集处理系统的功能,又能保存原始的数据为进一步的应用开发提供了硬件基础,能较好地解决网络传输带宽不足与关键时刻或者关键场景需要高分辨率图像进行分析处理的矛盾要求。采用FPGA+DSP的硬件组合具有相当大的灵活性,后期功能开发潜力大,可以根据不同的软件配置,实现多种功能,具有良好的应用前景。

责任编辑:gt

-

dsp

+关注

关注

554文章

8060浏览量

350865 -

FPGA

+关注

关注

1631文章

21806浏览量

606710 -

芯片

+关注

关注

457文章

51345浏览量

428270

发布评论请先 登录

相关推荐

分析一款不错的基于多DSP与FPGA的实时图像处理系统设计

基于FPGA+DSP的图像处理系统设计分析

基于FPGA+DSP的图像处理系统解析

基于多DSP与FPGA的实时图像处理系统设计

一种基于DSP+FPGA视频图像采集处理系统的设计与实现

如何使用DSP和FPGA技术实现细胞图像采集系统的设计

采用FPGA和DSP技术相结合实现图像采集和处理系统的设计

采用FPGA和DSP技术相结合实现图像采集和处理系统的设计

评论