能源与环境是当今全球性热点问题之一。天然气作为城市清洁能源,对我国的能源节约、环境保护、人民生活水平的提高和社会经济的发展有着重要的促进作用。天然气在我国的应用越来越广泛,城市燃气不会局限于以居民生活用气为主,而是在居民用气普及率提高的同时,拓展在车辆、采暖、制冷、商业和工业领域的应用。未来几年内,我国天然气需求将快于煤炭和石油需求,天然气市场在全国范围内将得到较大发展。目前,我国天然气输送管道所到之处,可以说是发展天然气终端市场的大好之地。高速增长的市场必然带来无限的商机。

天然气在输送、分配和使用过程中,需要对天然气的输送量、分配量和用户用量进行计量。在天然气流量的实用计量中,通常用某一段时间间隔内通过天然气管道输送的天然气总量来表示,即天然气的体积总量。天然气总量的计量对象类型很多,气源售出计量、城市购入计量、区域供气计量和用户用气计量等。目前国内天然气大都使用体积计量的方法,但由于天然气在不同的温度和压力下,气体体积有较为明显的变化,采用简单的体积计量,明显不符合公平交易的原则。如何将工况下的天然气体积通过温度、压力和压缩系数进行修正,从而得到标准状况下的体积,是保证天然气贸易结算公平的关键所在。信息技术的不断发展、计算机技术在计量系统中的广泛应用将会提高天然气的计量精度,加快测量数据的传递速度。

1 仪表总体设计

天然气体积修正仪主要完成天然气流量的自动修正,适于安装在工厂、住宅等环境,实时反映天然气的流量计量情况,并可与上位机进行通信,为上位机管理软件提供数据支持。

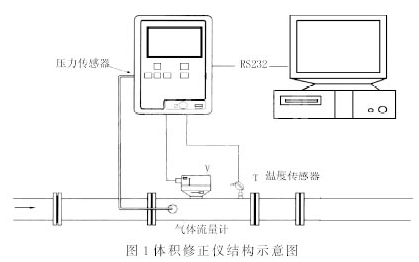

体积修正仪通过压力传感器和温度传感器采集压力和温度信息,结合气体流量计采集的流量脉冲信号进行天然气流量的自动修正,并通过RS232标准进行串口数据传送。图1是体积修正仪的结构示意图。

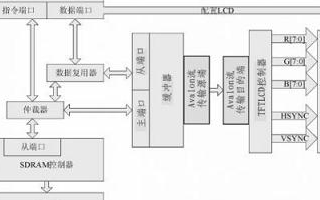

天然气体积修正仪根据功能设计如下5个模块:数据采集模块、体积修正模块、液晶显示模块、按键模块以及与上位机通信模块。几个功能模块采用低功耗FPGA器件,以Nios Ⅱ嵌入式处理器为核心,利用SoPC技术完成嵌入式开发。

2 数据采集模块设计

在天然气体积修正仪设计中,数据采集模块是保证测量和计算精度的首要模块。分为输入检测和数据处理两部分。

2.1 输入检测

天然气体积修正仪前端测量中涉及2个模拟量:温度和压力信号。根据温度和压力值可计算出天然气的压缩因子,从而校正天然气的体积。

2.1.1 温度检测

照顾到民用和商用的范围,设计采用Pt100陶瓷高性能铂热电阻温度计作为测温元件,铂在氧化性介质中,甚至在高温下的物理、化学性质都很稳定。另外,Pt100温度传感器还具有抗振动、稳定性好、准确度高、耐高压等优点。

本设计气体温度范围为:-30 ℃~70 ℃。经放大电路放大后电压变化范围在0V~4.5 V之间。

2.1.2 压力检测

由于工作压力范围为0~10 MPa,经过选型,采用CGYL-202压力变送器,其三线制输出电压范围为0 V~5 V,配合温度信号,方便后续模数转换。压力变送器采用硅杯压阻传感器为敏感元件,具有体积小、质量轻、结构简单和稳定性好的优点,精度也较高。且具有本安防爆认证,防震性能好。

2.2 A/D转换及数据处理

经采集的温度压力信号在参与压缩因子计算前必须经过模数转换。

本设计采用12位4通道、高速低功耗A/D转换芯片AD7864。AD7864是美国ADI公司生产的逐次逼近式并行输出的A/D转换器,片内由12位ADC、时钟电路、5 V高精度参考电压源和比较器组成,无需任何外部电路即可完成整个A/D转换的过程。该转换器自身带有4路采样/保持电路,可同时进行采样转换,这样就节省了系统的硬件电路空间。该器件最快转换时间可达1.65μs,信号输入范围可为0 V~5 V、±5 V或±10 V。

AD7864的控制状态引脚主要有:

(1)转换启动信号CONVST,下降沿触发一次四通道转换;

(2)工作状态忙信号输出BUSY,高为忙;

(3)读转换结果控制信号RD,低电平有效;

(4)片选信号CS,低电平有效;

(5)转换结束状态输出信号EOC,低电平有效;

(6)通道选择信号线SL1~SL4;

(7)硬件/软件通道选择方式H/S SEL;

(8)第1个数据输出状态信号FRSTDATA,第1通道转换结束数据可读触发为高,第2通道转换结束变为低。

本系统采用EP1C12Q240型FPGA,其足够的引脚资源完全能够满足需求。

2.2.1 数据采集模块总体设计

为了让CPU专注于处理其他任务,专门在FPGA内部设计一个A/D硬件控制器,负责对A/D的采样控制,并将采样数据进行滤波处理。该控制器还可以根据CPU的输出控制字改变采样的频率。

频谱分析的误差很大程度来自采样窗口和实际波形的同步不严格,造成频谱泄漏。为消除频谱泄漏引起的误差,常用的方法有硬件同步和加窗处理。硬件同步的方法比较多,常用的主要有使用PLL电路进行同步。因此,按照GB/T14549-1993要求,用FPGA内部高精度的PLL产生采样时钟来实现严格的同步采样,以保证窗口间无重叠和间隔,并能严格与被测信号频率同步。

在本模块中,所有时序控制均由FPGA完成,采用VHDL语言对FPGA进行配置,配置后的硬件功能包括对A/D转换器的控制、12位并行数据的处理和数据的滤波。

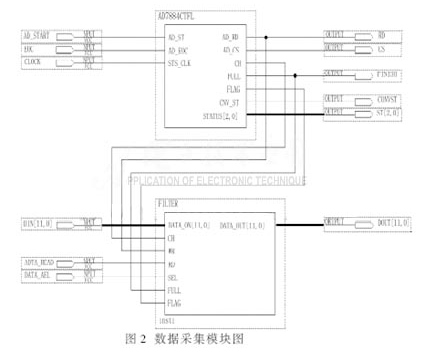

设计2个控制器完成上述功能:A/D控制器和滤波器。A/D控制器用来控制A/D时序,完成A/D转换功能。滤波模块完成数据的后续处理。设计模块图如图2所示。

2.2.2 A/D控制器设计

AD7864的工作时序图如图3所示。当CONVST信号为下降沿时启动一次四通道的A/D转换,因此采样频率决定于CONVST信号的频率,在第一通道开始转换之后BUSY信号为高,四通道转换全部结束后变为低,EOC为高表明正在转换,为低表示一次转换结束,可读取结果,此时将片选置为低,同时将读信号RD置低即可从数据线上将数据读出。为了便于控制采样频率,设置AD_START和CLOCK信号分别作为外部控制A/D开始转换信号和时钟信号。

本文采用硬件选择通道方式,SL1、SL2置高,两通道依次按顺序转换。由于两通道采样数据使用同一路数据总线依次读出,采用有限状态机(FSM)实现各通道数据的采集。状态机是逻辑设计中最重要的设计内容之一,通过状态转移图设计手段可以将复杂的控制时序图形化表示,分解为状态之间的转换关系,将问题简化。VHDL流水线设计方法可以提高系统的工作频率,采用VHDL语言编写控制程序。

状态机的状态转移图如图4所示,共分为6个工作状态:零状态(idle)、等待状态(STAND_BY)、转换第一通道数据(CH0_CONVST)、读第一通道数据(CH0_RD)、转换第二通道数据(CH1_CONVST)以及读第二通道数据(CH1_RD)。

FSM结构体定义信号类型ST和count。ST为状态,且初始状态为零状态;count用于读数据的计数,用于滤波。

为了实现快速状态转换同时增强稳定性,避免出现毛刺现象,A/D转换器的时序控制采用多进程有限状态机来实现。

(1) 时序逻辑

时序逻辑进程STATE_TRANS负责状态转换,当时钟信号SYS_CLK上升沿到来时,判断转换条件使状态机转入相应状态。

(2) 组合逻辑

组合逻辑进程STATE_BEHV负责状态输出,当状态变量ST发生变化时,产生对应此状态的CNV_ST,AD_RD AD_CS,CH(0为第一通道,1为第二通道)及STATUS相应输出。

(3) 计数逻辑

定义P0进程,敏感参数为CNV_ST,当一组数据采样结束(CNV_ST信号由0变为1),如果已经采集10组数据,则置位FULL信号,表示采样过程已经结束。

2.2.3 滤波器设计

A/D转换后的数据还不能立即送入处理器中处理,为了提高数据的准确性,设计滤波单元对数据进行处理。滤波滤波器设计实现经A/D转换后的数据滤波处理及数据的输出。

数字滤波模块的滤波算法采用中位值平均滤波法,相当于“中位值滤波法”+“算术平无度滤波法”,该方法计算简单、速度快,还可消除由于脉冲干扰所引起的采样值偏差,使得经滤波后的输出信号为“干净”信号,可直接用于工业控制。中位值平均滤波法的时域差分方程是:

本系统设计10组数据进行滤波处理,取N=8。为了节约FPGA内部资源,滤波器的设计中采用移位寄存器代替除法器来实现平均滤波部分的算法。滤波模块的设计从采样数据的输入、数值累加、去极值、求平均值到数字量的输出共5个处理步骤,并且整个数据处理是“单流向”的,前一步骤的输出是下一步骤的输入,符合流水线设计要求。采用流水线设计方法可以提高系统的工作频率,从宏观上看数字滤波模块不占用额外的处理时间,对于超高速A/D转换控制中显得格外重要。从VHDL语言的角度看,流水线操作是用面积换速度思想的具体体现[3]。

定义滤波器端口类型见表2所示。

从仿真图中可以看出,当时钟处于上升沿,AD_START变为高电平时,启动A/D转换,依次读2个通道的数据。当读满10组时,进行滤波处理。当CPU发出读信号时,数据读出。可见,设计的A/D控制器和滤波器完全符合设计要求。

对设计程序进行编译,可以看出,EP1C12Q240C8总的逻辑元数目为12 060,本控制模块只占用了227个,完全达到数据采集及滤波处理功能,极大地减轻了CPU的负担,可以让CPU专注于其他的任务。是一种可行且值得推广的方法。

3 总体功能仿真及编译结果

设计完成,生成顶层模块。该模块可直接加入到体积修正仪的SOPC设计中。其总体功能仿真如图5所示。

从仿真图中可以看出,当时钟处于上升沿,AD_START变为高电平时,启动A/D转换,依次读2个通道的数据。当读满10组时,进行滤波处理。当CPU发出读信号时,数据读出。可见,设计的A/D控制器和滤波器完全符合设计要求。

对设计程序进行编译,可以看出,EP1C12Q240C8总的逻辑元数目为12 060,本控制模块只占用了227个,完全达到数据采集及滤波处理功能,极大地减轻了CPU的负担,可以让CPU专注于其他的任务。是一种可行且值得推广的方法。

责任编辑:gt

-

传感器

+关注

关注

2550文章

51046浏览量

753126 -

处理器

+关注

关注

68文章

19265浏览量

229672 -

嵌入式

+关注

关注

5082文章

19111浏览量

304847

发布评论请先 登录

相关推荐

采用nios和μClinux实现嵌入式系统设计

如何实现天然气体积修正仪的系统设计?

Nios II入门起步-创建一个嵌入式处理器系统

基于Chirp函数的Nios Ⅱ嵌入式实现

介绍如何用Nios II 软核处理器来开发FPGA嵌入式系统软件

基于NiosⅡ处理器的嵌入式平台上实现μC/GUI的移植设计

FPGA Nios嵌入式处理器的软件开发

FPGA Nios嵌入式处理器的软件开发

基于Nios Ⅱ嵌入式处理器实现天然气体积修正仪的系统设计

基于Nios Ⅱ嵌入式处理器实现天然气体积修正仪的系统设计

评论