引 言

雷达作为一种特殊的无线电装备,也必然遵循从模拟到数字再到软件化这样的发展道路。数字波束形成技术被视为新一代雷达所必须采用的技术,它保留了天线阵列单元信号的全部信息,并可采用先进的数字信号处理技术对阵列信号进行处理,可以获得优良的波束性能,方便地得到超分辨和低副瓣的性能,实现波束扫描、自校准和自适应波束形成等。正是由于以上特点,DBF技术的成功应用必将对现代雷达技术的发展产生重大的影响。

在数字波束形成技术的工程化过程中,也遇到了一些问题。主要包括:数据传输量太大,尤其当阵元数较多时,这样就限制了通道的增加;来波方向估计和权值更新计算量太大,使得权值更新速度比较慢,无法在一些高速运动的载体上使用;当阵列数较多时,高速实时波束形成器的复乘运算耗费较多的资源,尤其是需要形成多个波束的情况下。原来的DBF系统就遇到数据传输瓶颈问题,采样数据只能通过PCI总线进行传输,无法保证所有通道的数据都实时传输,因而只能做需求数据较少的测向工作,并不能做实时波束形成。为了克服这些困难,这里将测向数据和波束形成数据分开进行传输,采用LVDS技术解决多通道高速数据传输,选择内置高性能DSP内核的高密度FPGA并行实现波束形成中的大量复乘运算。

1 DBF系统组成

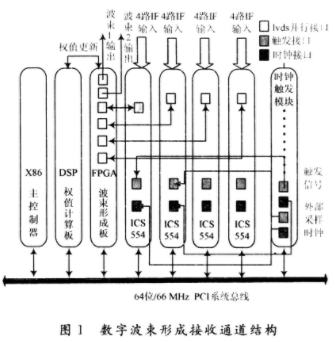

DBF系统包括阵列接收天线、多通道接收机、多通道数据采集板、FPGA波束形成板、DSP权值计算板、外部时钟触发模块、工控机等单元,如图1所示。接收机一般采用超外差方式,实现阵列接收信号的下变频、滤波,并将信号放大至A/D变换所需的水平。DBF系统最主要的功能就是实现来波方向估计(测向)和波束形成,DSP权值计算板承担来波方向估计和权值计算任务,权值计算要根据测向结果和波束扫描,以及对抗干扰的要求综合考虑得到,FPGA波束形成板承担全阵波束形成任务。波束形成器根据权值计算结果,通过对数字化的阵列单元接收信号进行复加权运算,形成所需的接收数字波束。

该系统中,由4块四通道采集板ICS554实现16阵元中频信号的模/数转换和数字下变频。为了实现所有通道的同步,采集板均工作在外部信号触发模式,外部采样时钟完全同步;来波方向估计和权值更新计算由DSP权值计算板完成,运算需要的每个通道数据量通常并不大,ICS554将测向所需数据通过PCI总线传送给DSP权值计算板;FPGA波束形成板要实现全阵的波束形成,就要对每个通道的数据复加权求和,得到最终所需的波束,因而需要传输数据量很大,4块ICS554通过LVDS将高速数据传输到FPGA波束形成板;权值由DSP权值计算板计算完成后,通过自定义的串口通信发送到FPGA波束形成板。

2 实时数字波束形成器设计

2.1 高速数据采集与传输

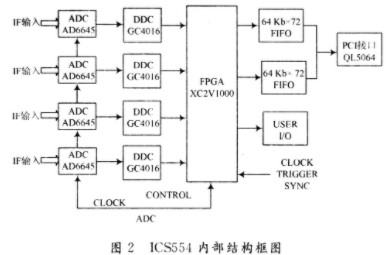

该系统中,由于信号带宽比较宽,选择ICS公司四通道的采集板ICS554实现数据采集任务,ICS554是ADC和数字下变频(DDC)集成化的产品。ADC决定了系统的动态范围,依据ADC的位数K,以每位6 dB增加,并随着以dB表示的并行接收通道数目N增加。ICS554的组成如图2所示,它主要包括4个独立的14 b/105 MHz模/数变换器AD6645,4个正交下变频器(QDDC)GC4016,1个100万门的用户可编程FPGA(Xilinx XC2V1000),2个512 KB的FIFO和1个PCI接口芯片QC5064。其中,AD6645的输入信号带宽可达50kHz~200 MHz,最大无虚假动态范围(SFDR)为92 dB(10 MHz±50 kHz),每个GC4016内部包括4个独立的DDC通道,每个通道都可独立控制其本振频率和初始相位,频率分辨优于24 MHz,全频段的覆盖使得每个GC4016共享共同的射频前端与A/D转换器,大容量的FIFO用于缓冲输出数据,FPGA则可用于对输出信号进行初步处理。ICS554具有较高的稳定性,优异的非线性以及正交等系统特性,灵活性比较强。ICS554的可编程控制参数通过配置不同的寄存器来完成。

该系统共16个天线单元,A/D采样频率105 MHz,经过数字下变频后形成30 MHz的I,Q两路24 b数据流,如果将所有数据传输到后端FPGA波束形成板进行处理,那么每块ICS554采集板每秒需要传输的数据量为:

4×2×24×30 Mb/s=5.625 Gb/s

考虑到采集板ICS554并未提供更高性能的数据传输总线,要实现5.625 Gb/s流量的数据传输很困难,因此利用板上预留给用户的FPGA资源,先在采集板中做一次子阵的波束合成,将同一采集板4通道的I,Q两路数据进行加权求和,得到合成的I,Q数据,数据流量降低为1 440 Mb/s。

采集板ICS554与FPGA波束形成板之间的连接采用LVDS技术,低电压差分信号(Low Voltage Dif-ferential Signaling,LVDS)是一种用低摆幅的差分电压串行传输信号的技术。这种信号能在差分PCB导线对或平衡电缆上以几百Mb/s,甚至上Gh/s的速率传输,具有低电压、低辐射、低功耗、低成本、强抗干扰能力和可内含时钟等优点,尤其适用于对传输距离有要求设备间的高速数据传输。但是,LVDS只定义了信号电气规范,作为一个完整的数据通信规范还需要相应的数据传输控制。为了提高效率,使用不含帧结构的数据直接传输,同时为了尽量增加数据传输的通道,取消发送端和接收端之间的控制信号,使用不连续的发送端时钟.仅在发送端数据有效时,给出发送时钟。这种情况下,接收端可以使用一个高于发送时钟的连续时钟对发送时钟进行采样来确定数据是否有效。

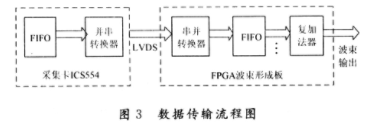

采集板ICS554本身给用户预留有64个通用I/O口,可以将其配置为LVDS的I/O口,这样可以提高数据传输能力和抗干扰性能。数据传输流程如图3所示,ICS554内部FPGA先将24 b的I,Q数据流并/串转换。VHDL语言的状态机实现并/串转换很容易,然后由LVDS发送模块将LVTTL信号转换成LVDS信号进行发送,接收端FPGA波束形成板首先将接收到的LVDS信号转换成LVTTL信号,然后进行数据同步,再经过串/并转换,将串码恢复成24 b的I,Q数据。由于利用ICS554提供给用户的通用I/O口配置为LVDS差分对,差分对的相位、互耦等都没有很好的考虑,而且不能采用专用的平衡电缆连接,因而必须降低传输速率,以减小传输误码率,增强可靠性,同时考虑配置9位的LVDS口,8位并行传输数据,1位发送时钟信号,LVDS传输速率为:

30×2×24/8=180 Mb/s

实际测试也表明,180 Mb/s的传输速度LVDS差分对能够可靠的工作,FPGA波束形成板正确地接收到采集板ICS554的数据。

2.2 实时波束形成计算

如前所述,整个实时波束形成分为两次,首先在采集板ICS554中完成子阵波束形成,然后再到FPGA波束形成板中实现全阵的波束形成,如何保证整个计算的实时性是关键。

波束的形成,其实就是对A/D变换后数字信号进行幅度和相位加权,波束的特性如波束指向、副瓣电平、主瓣宽度等完全由权值决定。权值计算主要考虑两方面的因素,首先要对各通道进行幅相校准,克服各通道不一致和互耦的影响,然后实现空域滤波,完成希望的波束指向。首先幅相校准,对于第i单元:

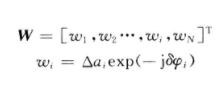

式中:δφi,△ai分别为第i通道与标准通道的相位差和幅度比值。若要实现空域滤波则需要在此基础上增加阵因子对幅度和相位加权。

![]()

式中:φi为第i通道相位加权值;αi为幅度加权值,可以根据不同的波束性能要求(主瓣宽度、旁瓣电平、零陷位置)灵活选择不同的幅度加权形式,得到不同的αi,权值矩阵W也会有所不同。权值更新计算由DSP处理板完成。

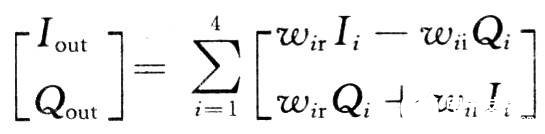

最初的子阵波束形成需实现四通道单元的波束形成,即对4路中频数字I,Q两路信号复加权求和:

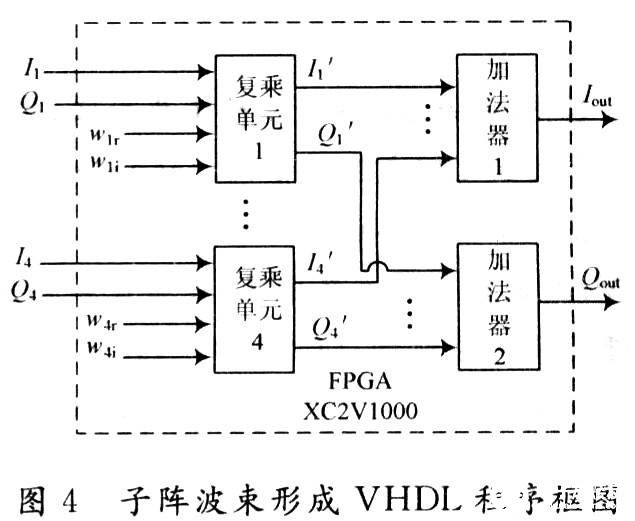

式中:Iout,Qout为4通道波束形成后I,Q两路输出结果;ωir,ωii分别为第i单元权值的实部、虚部。由于ICS554采样频率比较高,而FPGA片内剩余可利用的资源比较多,在这里采用并行复乘运算,运用ISE软件IP核设计映射出4个独立的复乘运算单元,片内VHDL程序设计如图4所示。

用4块采集板ICS554独立进行子阵波束形成,然后将结果Iout,Qout输出给FPGA波束形成板进行复求和,最终得到16个天线单元的全阵合成波束。考虑FPGA运算的复杂性,选用内含DSP内核的Xilinx公司的XC3SD3400A芯片,该芯片性价比非常高,内含的DSP内核XtremeDSP DSP48A运算速度可以达到250 MHz,差分I/O传输速率可达到622 Mb/s。要保证整个波束形成运算的实时性,主要从采集板子阵波束形成运算、数据传输、FPGA板全阵波束形成运算三个方面测试分析。全阵波束形成运算主要是在XC3SD3400A内做复数加法运算,加法运算最高可以到250 MHz,远远高于数字下变频后数据流速度。子阵波束形成运算则是在XC2V1000内做四通道并行复乘运算和复加运算,片内复乘流水线、复加运算时钟频率可达420 MHz。实际上,子阵和全阵波束形成的运算能力都是足够的,整个系统的主要瓶颈还是数据传输,数据传输流量大,数据传输I/O口位宽达8位,在数据传输环节,将低速多位并行数据用倍频时钟转换成250 MHz高速串行数据;在接收端,使用移位寄存器实现串/并转换就可以得到低速并行数据。仿真和实际测试也表明,能够保证整个系统波束形成运算的实时性。

3 结 语

这里设计的高速实时波束形成器,改善了原DBF系统,不仅可完成测向工作,同时实现了高速数据传输和全阵的实时数字波束形成。系统是基于采集板ICS554搭建的,ICS554虽然是一款高性能的4通道采集板,但是它成本高,而且只提供PCI接口,没有提供其他高性能的数据传输接口,当阵元数更多时其可扩展性并不强。为了达到数据传输能力的要求,采用了多组LVDS差分对数据进行传输,虽然实现了要求的速度,但是连接电缆太多,互耦影响大、传输距离短。因而,后续的系统设计中,利用FPGA集成速度更快的高速串行差分RocketIO通道、光纤传输等技术来改善性能,提高系统可扩展性。

责任编辑:gt

-

dsp

+关注

关注

555文章

8073浏览量

352084 -

FPGA

+关注

关注

1635文章

21837浏览量

608336 -

接收机

+关注

关注

8文章

1189浏览量

53810

发布评论请先 登录

相关推荐

数字波束形成相控阵中射频电子的物理尺寸分配

怎么设计基于FPGA多波束成像的声纳系统?

基于FPGA器件和LVDS技术设计的高速实时波束形成器

一种高速实时数字波束形成器的设计

成像声纳中多波束形成的FPGA工程实现

专用集成电路实现宽带射频相控阵波束形成

基于FPGA的B超全数字波束形成技术

采用FPGA器件和LVDS技术实现高速实时波束形成器的设计

采用FPGA器件和LVDS技术实现高速实时波束形成器的设计

评论