在三个关键系统模块(处理器,内存和互连(I/O))之间需要互相协调,每个要都在更好的提升性能。随着按各种指标衡量的处理器和内存速度已得到了大幅提高,所以互连也需要跟上发展,以免整体性能被卡了脖子!但是铜缆链路正面临着一些明显的障碍。电光互连似乎是解决方案,但要使其发挥潜能并与硅一起工作一直是一个重大挑战。

不过,最近有一次演示展示了英特尔与AyarLabs(加利福尼亚州埃默里维尔)之间的合作所取得的巨大进步,该项目是由美国国防高级研究计划局(DARPA)在其“光子学”中赞助的。该计划希望使用先进的封装内硅光子接口来实现每秒1T位(Tb/s)以上的数据速率,同时所需的能耗不到1皮焦耳/bit。并能实现千米级的传输距离(图1)。

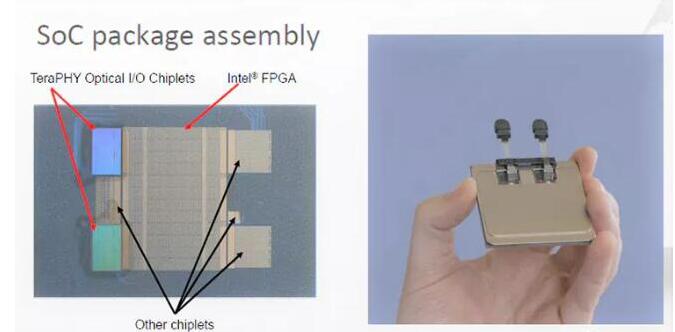

SoC器件显示(左)各个小芯片的位置以及完整的封装(右)。

英特尔/Ayar项目尚未实现这些目标,但确实朝着这些目标迈出了重要一步。在2020年光纤会议(OFC)上的线上演示中,Ayar展示了其TeraPHY光学芯片技术,该技术已集成到通常使用铜互连的改进型商用IC(英特尔Stratix10FPGA)中(图2)。

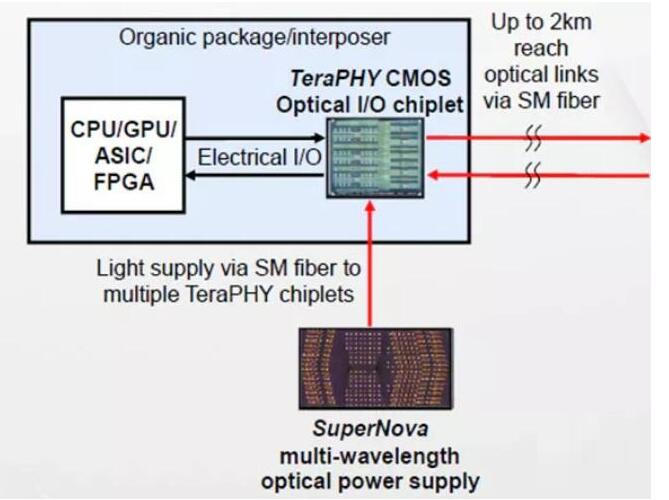

这是一种非常高级的光学I/O系统架构,图片显示了主要组件的互连

从硅电子中产生光数据流并不仅仅是先进的LED、激光二极管、增强掺杂或独特的制造结构的问题,尽管这些结构都具有更高的性能和扭曲度。。相反,它需要一种新的思维方式,需要先进的深层电光物理学见解,其中涉及合适结构中电子、电场和光子之间的关系。

利用硅光子技术

基本设计是基于使用硅光子学作为构件,包括波导、定向耦合器和微环谐振器。与广泛使用的马赫-曾德尔干涉仪(MZI)相比,后者是耦合和能量传输的首选,因为它提供了大约缩小100倍的小尺寸,25-50倍的高带宽密度和50倍的高能量效率。然而,它也需要更复杂的设计和精密制造。

Ayar公司的TeraPHY芯片片采用GlobalFoundries公司的45-nmSOICMOS制造工艺制造,该芯片集成了微米级的光波导。TeraPHY芯片上的光波导被蚀刻在硅片中,提供的功能是基于铜的能量和信号路径的光学模拟。将两个波导靠近,就能将光子和功率从一个波导转移到另一个波导,从而形成一个能量耦合器。在耦合器内,一个直径为10微米的微环谐振器可以对相位进行电调制,并控制光的方向,要么通过芯片,要么直至芯片顶部,从而创建I/O端口。

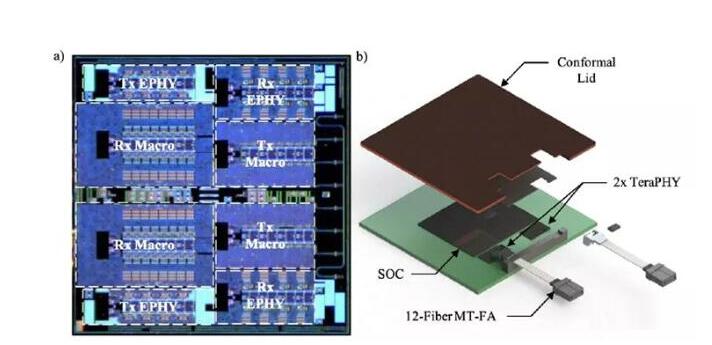

TeraPHY平台由单片集成的硅光子和CMOS组成(图3),采用倒装片系统封装(SiP),可将一个SoC的综合功能拆分在一个封装的多个小芯片上。这些小芯片采用密集、节能、短距离的封装内电气互连方式互连在一起。

图片展示了一个TeraPHY芯片的例子,显示了16通道25G光子发射(Tx)和接收(Rx)宏以及相应的串行器/解串器(SerDes)(a)。多芯片模块(b)的分解图包括一个系统级芯片裸片和两个TeraPHY芯片。(来源:AyarLabs)

SiP技术的主要优势在于能够使每个小芯片提供不同的专门功能,并使用最适合实现该功能的工艺技术进行制造,只要该小芯片仍可以符合标准的SiP集成和封装约束。这类似于在SiP中使用高密度CMOS来制作处理器或FPGA,再加上专业的模拟处理来实现精密数据采集和调理。

尽管目标为1pJ/bit,但在这种类型的设计中,散热方面的考虑与电子和光学方面的考虑一样重要,因为SoC耗散了300W,TeraPHY耗散4.7W。分析表明,解决TeraPHY耗散问题的实用解决方案将其分为TxRx,电气I/O和GPIO区域。

当然,封装也是分析的一部分,所得到的温度曲线说明了高性能系统中预期的热环境(图4)。尽管CMOS器件可以承受这些工作温度,但任何共封装的激光器都将降低效率并降低可靠性,因此TeraPHY被设计为使用外部激光源。

图4是多芯片模块(MCM)的等距剖视图

-

处理器

+关注

关注

68文章

19250浏览量

229623 -

芯片

+关注

关注

455文章

50697浏览量

423052

发布评论请先 登录

相关推荐

研究透视:芯片-互连材料

探索倒装芯片互连:从原理到未来的全面剖析

基于国产芯片的IPMI解决方案

解决方案 | 基于TSMaster的平板电脑解决方案

无人驾驶矿卡整体解决方案(5g物联网通信方案)

中国星坤满足各行业个性化需求的互连解决方案

Ansys和英特尔代工合作开发多物理场签核解决方案

恶劣环境对互连解决方案的影响及应对思路

芯片互连卡脖的解决方案

芯片互连卡脖的解决方案

评论