面壁十年图破壁,我以我血荐轩辕。

近日,华为消费者领域总裁余承东在中国信息化百人会2020年峰会上表示,受到美国第二轮制裁的影响,华为的芯片没办法生产,最近都在缺货阶段,今年发货量可能低于去年。由于9月15日后台积电也将断供,无法再承接华为高端芯片代工订单,华为麒麟高端芯片很快将成“绝版”。

不过令人振奋的是,余承东还表示,后悔当初没有进入芯片制造领域,但是在半导体方面,华为将全方位扎根,突破物理学、材料学的基础研究和精密制造,突破制约创新的瓶颈,包括EDA的设计,材料、生产制造、工艺、设计能力、制造、封装封测等关键流程,全部被华为设定到今后的目标领域之中。

虽然与各种限制,但是华为在2020年上半年的业绩还是依旧亮眼的,销售收入4540亿元,同比增长13.1%,净利润率9.2%。而且,从目前一系列布局来看,华为即将走向IDM即全流程芯片商,也就是一条再也不受外界卡脖子的道路。 那么,我们来盘点一下,华为在芯片产业内需要攻克的难关,同时也反思一下为什么我们的芯片产业会如此之脆弱,被人一卡就死? 小“芯片”的大能量 上世纪40年代由美国发起,众多知名科学家参与的曼哈顿计划不但为人类带来的原子弹,也为我们带来了计算机,而计算机中的集成电路也就是我们芯片的前身,渐渐发展成了一个市场规模近万亿的庞大产业,单是中国对外的芯片净进口额去年就达到了4000亿人民币,甚至我国进口的芯片价值还超过了能源进口1000亿。 而芯片行业的上游是以EDA为代表的工业软件,下游则辐射物联网、云计算等规模数十万亿人民币的巨大市场 ,而4000亿的芯片规模与40万亿产业链规模之间的差额,就是芯片杠杆。可以说,运用芯片卡住我国的脖子,效果远比什么金融核武Swift要好得多。

EDA软件突破难度 ※※※※突破希望 ※※※※EDA是计算机辅助设计CAD的细分领域,属于工业软件的一种,利用EDA工具,芯片设计人员可以从概念、算法、协议等开始设计电子系统,完成电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程。数据显示,2018年全球EDA市场规模还没突破100亿美元,EDA相对于几千亿美元的芯片产业来说从产值上看根本不值一提,但如果缺少了EDA,整个芯片产业都得停摆。 EDA市场前三位的Synopsys、Cadence和西门子约占全球市场份额的60%,产业集中度并不是太高,不过在中国市场,却完全是另一番景象,我国EDA的市场份额95%由上述三家瓜分,而且这三家EDA巨头公司已经完全和华为中断了合作。 其实我国在EDA方面起步不算晚,早在上世纪90年代我国自主研发的熊猫EDA软件就问世了,这也是我国最大的EDA厂商华大九天的前身。不过在熊猫刚刚面世不久,Synopsys、Cadence就纷纷入华,以低价占领市场,直接把我们的熊猫EDA扼杀在了摇篮里。 前不久爆款文《我国工业软件消失的30年》中曾经将我国工业软件衰落的原因归结为国家补贴的不足,笔者虽然不太认同这样的观点,但是过早的让我们不成熟的产品直接面对市场的竞争,也使我们在EDA方面不被卡脖子的希望随之消失。 芯片设计领域EDA软件,就类似于美工设计师的Photoshop,机械设计师的Autocad,如果没有这些工具辅助设计成本就直接突破天际,而且EDA软件中丰富的IP库,还可以为芯片仿真,降低流片率起到关键性作用,而一旦被EDA厂商断供就意味着没有了IP库的更新,也就是无法再用最新的元器件库进行设计或者访真了,所以EDA软件也成了我们首要解决的问题之一。 IP授权突破难度 ※※※※突破希望 ※※※既使有了EDA软件可以进行芯片设计,但芯片设计师们在动手之前,也必须先决定芯片的架构,也就是指令集。 目前我国还没有拥有完整知识产权的芯片指令集。目前应用较为广泛的X86以及ARM架构芯片,其实都是需要单独授权乃至完全封闭的IP。一旦产权方停止授权而开成断供那么后果不堪设想。而在这方面阿里达摩院的RISC-V以及龙芯所使用的MIPS架构相对比较安全。 其中RISC-V 是 2010 年新出现的开源精简指令集架构,架构设计上没有历史包袱,采用的理念和方法较为先进。和主流架构 x86/ARM 相比,RISC-V 架构篇幅更少,基本指令集更少, 支持模块化和拓展性,而且为贯彻开源精神。目前RISC-V基金会已经有搬迁至瑞士的计划了,不过RISC-V架构出现时间晚, 适配软件和工具方面沉淀不足,目前虽然由阿里达摩院推出了号称最强RISC-V的玄铁910芯片,不过总体上讲其生态环境构建尚需时间。 而MIPS在给予龙芯永久授权后,也由龙芯继承了MIPS所有的生态,因此MIPS在国内发展及工具积累的情况相较于RISC-V要好一些。目前龙芯已经发布了基于 MIPS自主版权的指令集 LoongISA。其最新产品 3A4000/3B4000 的性能与 AMD 28nm 工艺的产品相当,而且目前龙芯已经全面进入云计算领域,并与浪潮云、阿里云、腾讯云等巨头合作。 但是,无论是MIPS还是RISC-V都还无法在高端领域与ARM及X86进行全面对抗。好在华为已经拿下了ARMV8的完整授权,而ARMV9最迟也会在2022年问世。因此芯片指令集,也是一个我们急需要解决的问题。 晶圆制造突破难度 ※※※※※突破希望 ※※提起晶圆制造也就说到了芯片生产过程中最难的环节了,而且值得注意的是在晶圆制造这个环节中也会决定制程,这个芯片最为重要的指标。 这里也再为大家科普一下制程的相关概念。上世纪60年代,仙童半导体的Gordon Moore在《电子学》杂志上,发表论文提出了如雷贯耳的摩尔定律,即当价格不变时,集成电路上可以容纳的元器件数目,将每隔一年增加一倍,这其实就是指元件的密度会不断增大,也就是原件之间的间隔距离不断减少,而在芯片中不同原件的距离就是制程,所以摩尔定律也可以被称为是制程定律。 我们知道CPU是以0和1为基础的逻辑运算,其关键就是要判断晶体管中的电位情况。当在Gate端做电压供给,电流就会从Drain端到Source端,如果没有供给电压,电流就不会流动,通过这样表示1和0。 缩减元器件之间的距离之后,晶体管之间的电容也会更低,从而提升它们的开关频率。那么,由于晶体管在切换电子信号时的动态功率消耗与电容成正比,因此,它们才可以在速度更快的同时,做到更加省电。另外,这些更小的晶体管只需要更低的导通电压,而动态功耗又与电压的平方成反比,这时能效也会随之提升。以10nm制程的骁龙 835为例, 在集成了超过 30 亿个晶体管的情况下,体积比14nm骁龙 820 还要小了 35%,整体功耗降低了 40%,性能却大涨 27%。因此,我们可以看到一款芯片最大的宣传点就是它的制程。 而想造出先进制程的芯片,还需要先进工艺与光刻机的共同配合才行。半导体的制造工艺,主要经历了如下几个阶段:MOS时代:在上世纪50年代末贝尔实验室研制出MOS管,也就是金属-氧化物半导体场效应晶体管,在MOS管推出不久能够量产晶体管的平面工艺诞生,通过氧化、光刻等一系列的流程,可以制作出晶体管集成电路,也就是我们目前所说的芯片,不过当时还只能称为集成电路时代,原件密度比现在要低的多,不过这也成为了制造各种半导体器件与集成电路的基本工艺技术,也是光刻技术的原型。

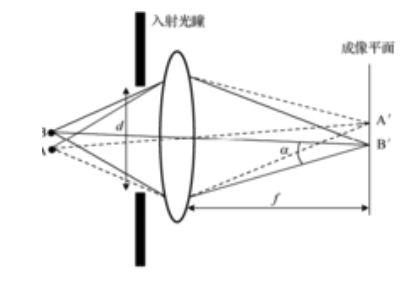

FinFET:但是MOS管也并不尽善尽美,其制程存在着20nm的极限,不过在2000年加州大学伯克利分校的胡正明教授发表了一篇文章《FinFET-a self-aligned double-gate MOSFET scalable to 20 nm》,在该论文中提出了一种名为FinFET晶体管结构,中文译名为“鳍式场效应晶体管”,顾名思义,这种晶体管结构形状也就类似于鱼鳍, FinFET使得芯片制程突破了20nm的工艺关键节点,是推动当代工艺进一步缩小的关键技术。GAAFET:(Gate-All-Around)由Imec(Interuniversity Microelectronics Centre)提出。GAA也就是横向晶体管技术,也可以被称为GAAFET。这项技术的特点是实现了栅极对沟道的四面包裹,源极和漏极不再和基底接触,而是利用线状(可以理解为棍状)或者平板状、片状等多个源极和漏极横向垂直于栅极分布后,实现MOSFET的基本结构和功能。这样的设计在很大程度上解决了栅极间距尺寸减小后带来的各种问题,包括电容效应等,也可以突破目前7nm的制程极限,不过这项技术目前还没有正式的商用,只是台积电和三星等头部厂商取得了一定进展。 可是我国以中芯国际为代表的芯片制造厂商的制造工艺水平还停留在14nm,比国际最高水平的5nm整整落后了一代。不过即使有了14nm的制造工艺,中芯国际也还没明确表示,可以继续向华为供应芯片,这是因为我国在光刻技术方面的水平只达到28nm,而且造不出最先进的EUV光刻机。EUV:Extreme Ultra-violet极紫外光刻,是目前最为先进的光刻技术,由于光源对制程工艺的影响是决定性的,目前非EUV的光源还无法突破7nm的极限。因此没有EUV的加持,我们就像被三体的智子锁定基础科技发展水平一样,最高也只能达到14nm的制程水平上。 令人遗憾的是,我国光刻技术的起步并不晚,早在上个世纪60年代中科院就开始研究光刻机了,并且在1965年就研制出65型接触式光刻机,1972年武汉无线电元件三厂编写的《光刻掩模的制造》的书中,具体讲述了当时那个时代,我们光刻技术的发展历程,后来1980年中国清华大学第四代分布式投影光刻机获得成功,将光刻精度缩小至3微米,这个制程与当时国际先进水平非常接近。 不过与熊猫EDA的情况类似,同样由于我们过早的让自主的光刻产品直接面对西方企业的价格竞争,这使得我国光刻先驱武汉无线电元件三厂在1994年破产,改制成为副食品商铺,这使得我们20年光刻技术的积累全部付之东流,而且陷入停滞。 总有有说光刻有那么难吗?笔者这里可以给出一个非常肯定的答案,光刻技术之复杂精密,尤其对于基础光学水平要求很高,想取得突破谈何容易。 下面向大家简要介绍一下光刻技术。在一台光刻机中激光器负责光源产生,首先是激光器发光,经过矫正、能量控制器、光束成型装置等之后进入光掩膜台。

而光刻机的分辩率原理图如下,下图中AB两点的距离就是不同元件间的距离, 光刻机分辨率=k1*λ/NA:

随着半导体工业节点的不断提升,为提高分辩率指标,光刻激光波长也在不断缩小,从436nm、365nm的近紫外(NUV)激光进入到246nm、193nm的深紫外(DUV)激光,现在DUV光刻机是应用最多的,光源是ArF(氟化氩),从45nm到7nm工艺都可以使用这种光刻机,但是到了7nm这个节点就是DUV的极限,所以英特尔、三星和台积电都会在7nm这个节点引入极紫外光(EUV)光刻技术。 不过正如笔者前文所述,光刻涉及的基础科学领域繁多,即使是国际光刻巨头ASML也不能掌握光刻技术的全产业链,其镜头和激光器也是从德国、比利时等国家进口的。所以华为想以一人之力打通整个芯片的产业链条,其勇气与决心也可见一斑。 封装 、测试突破难度 ※※※突破希望 ※※※※目前芯片的封装测试分为晶圆测试与成品测试两个步骤。晶圆检测:指通过探针台和测试机配合使用,对晶圆上的裸芯片进行功能检测和电参数测试,其检测过程为:探针台将晶圆逐片自动传送至测试位置,将芯片的pad点通过探针/专用连接线与测试机的功能模块进行连接,测试机对芯片世家输入信号并采集输出信号,判断芯片功能和性能是否达到设计规范要求。测试结果通过通信接口传送给探针台,探针台据此对芯片进行打点标记。成品测试:指通过分选机和测试机配合使用,对封装完成后的芯片进行功能和电参数测试,其测试过程为:分选机将被测芯片逐个传送至测试工位,被测芯片的引脚通过测试工位上的基座,专用连接线与测试机的功能模块进行连接,测试机对芯片施加输入信号并采集输出信号,判断芯片功能和性能是否达到设计规范要求。测试结果通过通信接口传送给分选机,分选机据此对被测芯片进行标记、分选、收料或编带。 其实如果我们能突破到这步,也就基本不会再被人卡脖子了,因为这方面不像光学、材料学等基础科学的突破,还是可以靠多掏学费弥补的。 穷且益坚不坠青云之志,老当益壮宁移白首之心。目前我们在通用计算的芯片领域虽然还有很多困难要克服,不过从最新年报披露的信息来看,华为应该已经为这场硬仗,提前准备了未来一到两年的芯片储备,用时间换空间,以期突破这些卡脖子的环节。 不过,我们也必须清醒的认识到,芯片虽然是IT领域的核心产业,但芯片制造却更偏向于基础科学的属性,只能结硬寨,打硬仗,没有捷径可言,也呼吁业界同仁给予华为以及我国整个芯片业以更多耐心,以期破壁图强,逆境重生。

-

集成电路

+关注

关注

5381文章

11391浏览量

360902 -

华为

+关注

关注

215文章

34322浏览量

251204 -

芯片制造

+关注

关注

9文章

610浏览量

28775

原文标题:华为麒麟将成“绝版”,造芯为什么这么难?

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ADS1256的输出会突然下降,然后锁死,为什么?

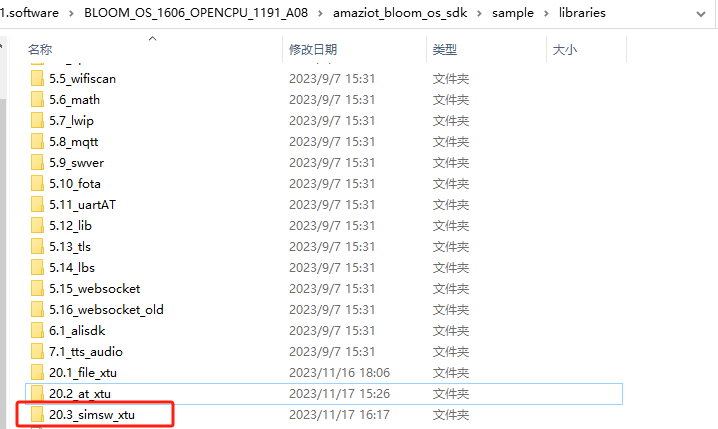

物联网行业中全网通卡切卡方案

PCB设计有必要去掉死铜吗?死铜能带来什么问题?

2024世界芯片产业链博览会暨峰会,一位难求?巨头纷纷借势!

ST3232接口芯片锁死怎么解决?

SPC58E芯片锁死的原因?

stm32c031 Nucleo开发板芯片锁死的原因?

NVIC_SystemReset()导致系统挂死怎么解决?

如何通过Jlink查看GD32芯片跑飞后程序死在哪里?

如何减少LED透明屏死灯的问题?

PCB设计有必要去除死铜吗?

为什么我们的芯片产业会如此之脆弱,被人一卡就死?

为什么我们的芯片产业会如此之脆弱,被人一卡就死?

评论