近期,英特尔举办了“架构日”活动,发布了一系列重磅技术。在这次“架构日”的活动中,英特尔六大技术支柱推出全面、实质性的新进展,为英特尔构造产业最具领导力的产品再添“利器”。

英特尔六大技术支柱指的是制程&封装、架构、内存&存储、互连、安全和软件,依靠这六大技术支柱,英特尔的技术更具灵活性,并且能够快速为客户提供具备领导力的产品。英特尔中国研究院院长宋继强在近期接受媒体的采访中表示:“在目前的环境下,产品种类众多,有云、边缘计算、各类智能设备,并且要求快速给出方案,因此英特尔要依靠多个领域的技术,即我们的六大技术支柱,组合起来形成产品的领导力,并能够快速达到客户需要的性能要求,增强客户对我们的信心。”

图注:英特尔六大技术支柱

对于英特尔来说,能够为客户快速提供具备领导力的产品是终极目标,而六大技术支柱是实现这样目标的重要“根基”。在六大技术支柱中,每一个支柱都很关键,所发挥的作用都无可取代。

制程是基础,封装在“异军突起”

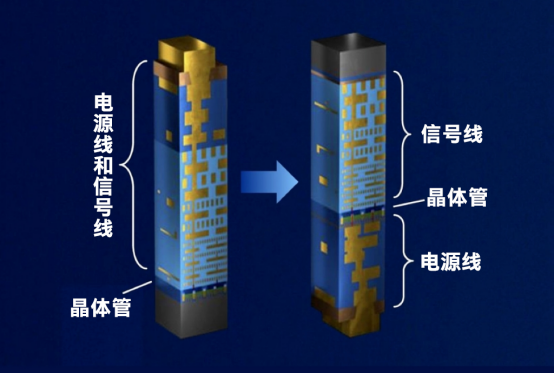

制程工艺是非常重要的基础。在今年“架构日”上,英特尔推出了创新的晶体管技术SuperFin。这项技术拥有行业颠覆意义,英特尔在底层晶体管设计上做了优化,降低了电阻,提高了电流,同时在电容层级采用了Super MIM的大幅优化技术,电容量提高了5倍,同时降低了压降。

与上一代10纳米相比,SuperFin所带来的性能提升超越了15%。 宋继强表示:“我们14纳米节点,每一次性能提升是5%左右,SuperFin所带来的性能提升在以前是可以作为一次跨越节点提升的。”

封装技术也在“异军突起”,英特尔在封装领域有多种维度的先进封装技术,并且处于业界领先地位。英特尔有标准封装、2.5D的EMIB、3D的Foveros以及在今年“架构日”上推出的Hybrid Bonding(混合结合)技术,可以把凸点间距降到10微米以下,带来更高的互连密度、带宽和更低的功率。这些封装技术还可以相互叠加,叠加后能够带来更大的扩展性和灵活性。例如,Co-EMIB技术就是把2.5D的EMIB技术和3D的Foveros封装技术进行整合。

“封装技术的发展就像我们盖房子,一开始盖的是茅庐单间,然后盖成四合院,最后到高楼大厦。以Foveros 3D来说,它所实现的就是在建高楼的时候能够让线路以低功率同时高速率地进行传输,” 宋继强表示。“英特尔在封装技术持续投资,因为它的优势在于我们可以更早地知道,未来这个房子会怎么搭,也就是说可以更好地对未来芯片进行设计。”

面向未来异构计算的大趋势,英特尔在今年的“架构日”上推出了“分解设计”策略,这是一种结合新的设计方法,如晶片分解,以及先进的封装技术,将关键的架构组件拆分为仍在统一封装中单独晶片的解决方案。宋继强表示,分解设计就是把原先的整个SoC芯片由大变小,“化整为零”,先把它做成几个大的部分,比如CPU、GPU、I/O,再将SoC的细粒度进一步提升,将以前按照功能性来组合的思路,转变为按照晶片IP来进行组合。这些分解开的小部件整合起来之后,速度快、带宽足,同时还能实现低功耗,有很大的灵活性,将成为英特尔的一大差异性优势。

相对于以前的芯片整体设计思路,分解设计的好处在于,不仅能够提升芯片设计的效率、降低产品化的时间,并且能够有效减少此前复杂设计所带来的Bug数量。“原来一定要放到一个晶片上做的方案,现在可以转换成多晶片来做。另外,不仅可以利用英特尔的多节点制程工艺,也可以利用合作伙伴的工艺,”宋继强解释。“这样可以给客户更多选项,在每个选项下面可以选择最好的不同部件的组合,不管是to C还是to B的需求,都可以快速开发多种不同产品方案给客户,而不是说芯片都必须要在单一节点内实现。”

XPU架构 & oneAPI软件,真正释放硬件潜能

在“万物智能化”的时代下,数据量呈指数级增长,我们有大量的数据和处理需求,有的要实时,有的要稀疏,有的要并行,有的需要矩阵,所以说一个架构“包打天下”的时代已经过去,应对不同的数据需要采用不同种类的芯片架构,因此英特尔提出了XPU架构,这个“X”指的是至少会包含CPU、GPU、专用加速器以及FPGA的混合架构,从而处理部署的标量、矢量、矩阵和空间架构数据。

英特尔的GPU架构也迎来重大更新,全新的Xe架构最大的特点是高度可扩展。它同时拥有性能向上增长(Scale Up)以及向外拓展(Scale Out)的能力。性能向上增长指的是单个GPU构造组件区块(Tile)性能能够提升,内部也有多个EU执行单元。向外拓展指的是可以构建多个区块(Tile),并根据不同的任务规模去组合,在架构上充分体现了灵活性,以及可以在未来增加一些新的加速部件。

宋继强认为,要真正获得硬件异构之后的超级性能提升,没有好的软件是不行的。如果软件能够根据不同领域的工作负载进行优化,性能提升可以高达十倍甚至是百倍,而英特尔oneAPI就担负了这样艰巨的重任。作为跨XPU架构统一编程模型,oneAPI是一个开放的产业联盟,它包含工具链、性能库、编译器、调试、编程、程序移植等,可以帮助开发人员有效减少跨架构程序开发时间和成本。

“架构和软件,这两个是要搭配的,架构要体现出不同的架构都能玩的转,同时做出来的硬件还要能让别人用软件快速使用。如果新的架构出来,没有一个很好的软件能够把它生态化,那就还是起不来,” 宋继强表示。“所以除了要有很好的架构掌控能力,还需要软件能够把这些好处暴露出来,XPU & oneAPI未来会成为英特尔突出的特点。”

再“乘以”内存和存储、互连和安全,英特尔综合实力爆棚

同时,作为计算不可或缺的部分,内存和存储,互连以及安全技术也是英特尔“六大技术支柱”的重要组成部分。

根据宋继强的介绍,在原来三级存储模式中,每一级之间的速度差是百倍,容量差别也是百倍到千倍,因此在高性能计算中,会造成很大的性能损失,因此要填补这个差距,通过内存和存储技术提升计算性能。英特尔最新发布的3D NAND已经可以达到144层,当内存使用的XPoint也从之前的2-Deck增长到了4-Deck,属于国际领先的技术。

“互连”技术也是重要的技术之一。因为要把不同的设备连在一起,把不同的芯片连在一起,连接距离小到微米级,大到公里级,甚至是数百公里级,在客户端产品以及数据中心产品都会涉及。英特尔最新的互连技术在提升带宽的同时,还能够减轻体积和降低功耗。在安全方面,英特尔的控制流强制技术(CET)为计算带了更好地安全保护,避免通过控制流返回跳转攻击软件漏洞。

“当我们把这些技术全部乘在一起的时候,英特尔就构建出一个以XPU为上层架构,中间以各种级别的内存作为支撑,底部是从云到端的完整产品布局,从而产生各种各样快速创新的能力,并且能够和产业界分享,” 宋继强表示。

总结来看,英特尔六大技术支柱包含的内容涉及到计算的各个方面,所带来的综合实力在业界内独树一帜,具有其他厂商不可比拟的优势。在制程工艺逼近极限之际,未来半导体行业的比拼一定是综合实力的比拼,制胜的关键点就在于能否为客户又快又好地提供产品,解决在数据大爆发的现状下,能否实现指数级增长的挑战。英特尔的六大技术支柱已经打下了非常坚实的基础,必将助力英特尔继续行稳致远。

责任编辑:pj

-

芯片

+关注

关注

455文章

50851浏览量

423987 -

英特尔

+关注

关注

61文章

9974浏览量

171824 -

晶体管

+关注

关注

77文章

9698浏览量

138259

发布评论请先 登录

相关推荐

英特尔IEDM 2024大晒封装、晶体管、互连等领域技术突破

英特尔展示互连微缩技术突破性进展

英特尔推出全新英特尔锐炫B系列显卡

技术前沿:“环抱”晶体管与“三明治”布线

英特尔采用Super MIM优化技术推出晶体管技术SuperFin

英特尔采用Super MIM优化技术推出晶体管技术SuperFin

评论