SDRAM是一种RAM类型的易失性存储器件,因其具有较大的容量和相对较低的价格在嵌入式系统中应用广泛。然而应用SDRAM需要实现刷新操作、行列管理、不同延迟和命令序列等逻辑,控制复杂,而Qsys提供的SDRAM控制器IP核接口极大的方便了SDRAM的使用,本文我们实现使用SDRAM控制器IP核对SDRAM进行读写操作。

理论部分简介

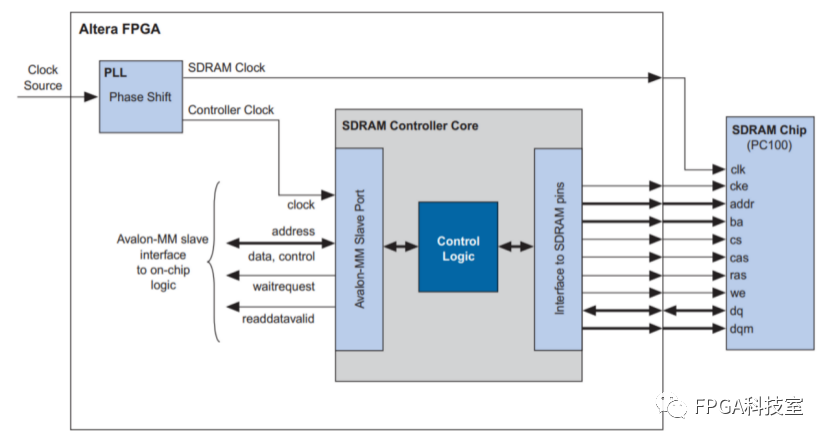

SDRAM控制器IP核能够处理所有的SDRAM协议要求,包括上电初始化、地址复用、刷新、读写时序等,极大的方便了SDRAM的使用。下面我们先来看看SDRAM控制器IP核和SDRAM芯片的连接框图,如下所示:

从上面的这个结构框图中,我们可以看到SDRAM控制器IP核产生于FPGA内部,它带有接口引脚、控制逻辑、以及Avalon从机接口。接口引脚用来连接外部SDRAM芯片管脚,这些接口引脚通过Altera FPGA上的I/O引脚连接到SDRAM芯片管脚上。控制逻辑用来实现SDRAM的操作,比如,SDRAM初始化,自刷新,突发读写等,这些全都是控制逻辑来完成的,控制逻辑不需要我们编写,当我们生成SDRAM控制器IP核之后,它会自动生成。

Avalon从机接口用来连接我们的CPU,Avalon从机接口是SDRAM控制器IP核中仅为用户可见的部分。从控制器端口提供一个如SDRAM芯片一样大的平滑、线性存储器空间。当访问从控制器端口时,SDRAM协议的细节完全透明。Avalon接口作为一个简单的存储器接口操作,没有存储器映射的配置寄存器。这里我们需要注意的是:SDRAM芯片必须和Avalone接口一样以相同的时钟来驱动。

我们可以看到图中的片内锁相环(PLL),它就是用来调整SDRAM控制器与SDRAM芯片之间的时钟相位差。在较低的时钟频率下,可能不需要PLL。在较高的时钟频率下,当信号在引脚上有效时,需要PLL来调整SDRAM时钟。PLL并没有包括在SDRAM控制器内。如果需要PLL,设计者必须在生成Qsys系统模块以外手动添加PLL。Altera FPGA和SDRAM芯片的不同组合将要求不同PLL的设置。

还有一点我们需要说明的是fmax性能取决于整个硬件设计。Qsys系统模块的主控制器时钟驱动SDRAM控制器和SDRAM芯片。因此,整个系统模块的性能决定SDRAM控制器的性能。例如,为了实现100MHz的fmax性能,系统模块必须设计为100MHz时钟率,且QuartusII软件的时序分析必须检验硬件设计是否能够进行100MHz的操作。说完了SDRAM的综述之后下面我们就总结给出SDRAM控制器IP核的功能特性:

(1)SDRAM控制器IP核具有不同数据宽度(8、16、32或64位)、不同内存容量和多片选择等设置。

(2)SDRAM控制器IP核可以全面支持符合PC100标准的SDRAM芯片。 (PC100,表明时钟信号为100,数据读写速率也为100)

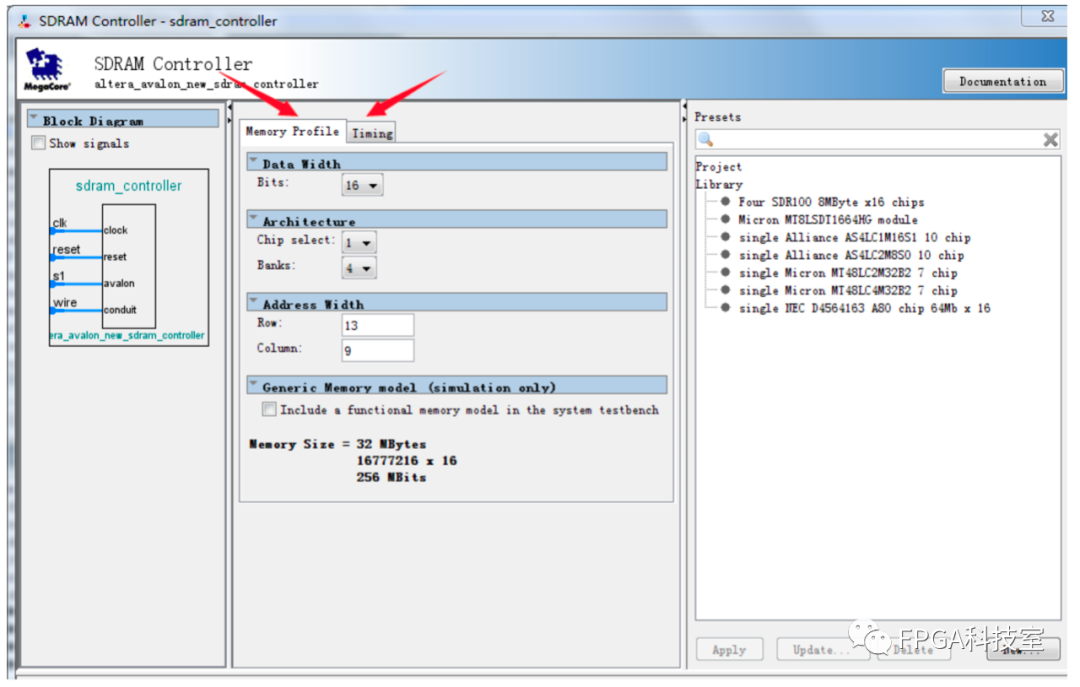

(3)SDRAM控制器IP核可选择与其他的片外Avalon三态器件共用地址和数据总线,该特性在I/O引脚资源紧张的系统中很有用。我们可以在Qsys中使用SDRAM IP核的配置向导来指定硬件特性和仿真特性。SDRAMIP核配置向导有两个选项卡:Memory Profile和Timing,如下图所示。

为了使用方便,Presets列表提供几个预定义的SDRAM配置。如果实际使用的SDRAM芯片型号与列表中的一致,可直接选用而不用设置其他选项。选择不同的预配置,SDRAM IP核将自动改变Memory Profile和Timing选项卡上的值来匹配指定的配置。如果实际使用的SDRAM芯片与列表中的不相同,则需要设计者根据SDRAM芯片数据手册的参数来设置Memory Profile和Timing标签上的值,改变任何选项卡上的配置设置转变Preset值为custom。

当然我们也可以将我们配置好的SDRAM参数添加到预定义的SDRAM配置,在今后的使用过程中我们就直接选择我们添加的预定义的SDRAM配置。接下来我们就来简单的介绍一下Memory Profile和Timing。

(1) Memory Profile选项卡

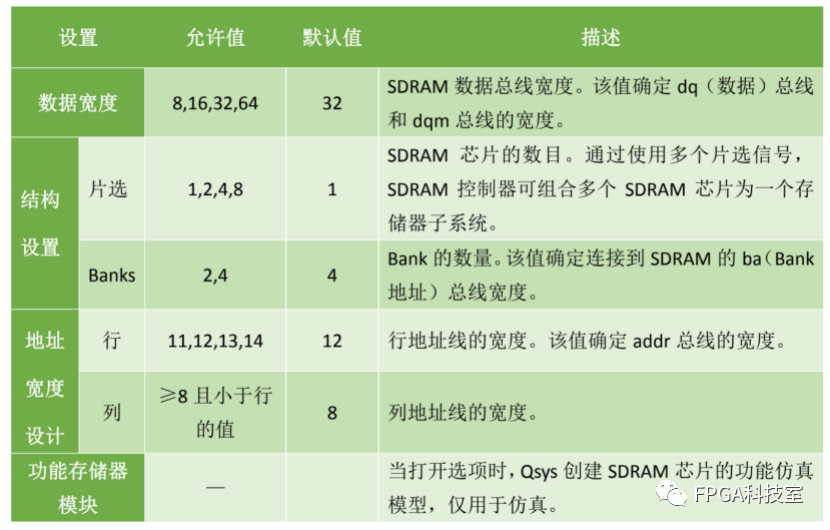

Memory Profile选项卡允许设计者指定SDRAM的结构,例如地址和数据总线宽度、片选信号的数目和区的数目等。Memory Profile选项卡设置项如下表所示。

这些参数值可参照使用的SDRAM手册来设置。通过Memory Profile选项卡上的设置后,消息框以兆字节、兆bit位以及可寻址的字长显示SDRAM预期的内存容量。将这些预期值与选择的SDRAM的实际大小相比较可以检验设置是否正确。说完了Memory Profile选项卡,接下来我们看看Timing选项卡。

(2) Timing选项卡

Timing选项卡允许设计者设置SDRAM芯片的时序规范。正确值在SDRAM芯片数据手册中提供。Timing选项卡上可用的设置如下表所示。

我们需要注意的是无论我们输入的精确时序值如何,每个参数实现的实际时序将为Avalon时钟的整数倍。对于每隔一段时间执行一个刷新命令的参数,实际时序将不超出目标值,而其他所有参数,实际时序将大于或等于目标值。

操作任务

利用官方SDRAM ControllerIP核实现对SDRAM的读写操作。

硬件设计

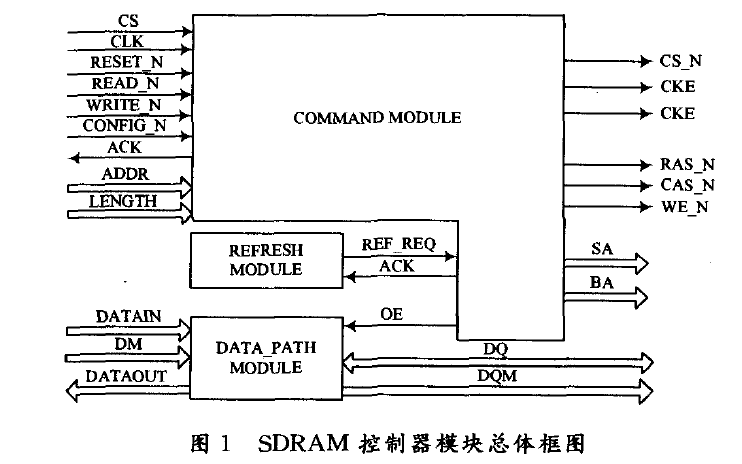

实验的硬件框架如下图所示:

图中,我们要把clk IP 核的时钟频率设置为 100MHz。

另外需要注意的是,Nios II IP 核需要将复位向量 Reset Vector 和异常向量 Exception Vector 都设置为 SDRAM,如下图所示:

现在我们主要来介绍一下新添加的SDRAM IP 核,按照使用的 SDRAM 型号为

W9825G6KH的datasheet,配置如下图所示。

为了方便大家以后的使用,下面我们就简单为大家讲解一下如何将自己的SDRAM配置添加至Library中。当我们配置好SDRAM以后,我们可以在窗口的右下方找到【New】按钮并点击,弹出如下图所示页面。

在该页面中,我们将Preset name和Preset description填写好以后,我们就可以点击【Save】按钮,弹出如下图所示提示窗口。

在该提示窗口中我们选择是,这时我们就可以在Library中看到我们添加的SDRAM配置了。然后我们重新打开Qsys软件,这时,我们就可以在SDRAM的Library中看到我们添加的W9825G6KH。最后我们再补充说明一点,SDRAM为动态存储器对时序要求比较高,由于FPGA内部有延迟,所以PLL输出100Mhz时钟频率给SDRAM_SCLK时,PLL时钟需要设置相位偏移,

相位偏移我们设置为-75deg。

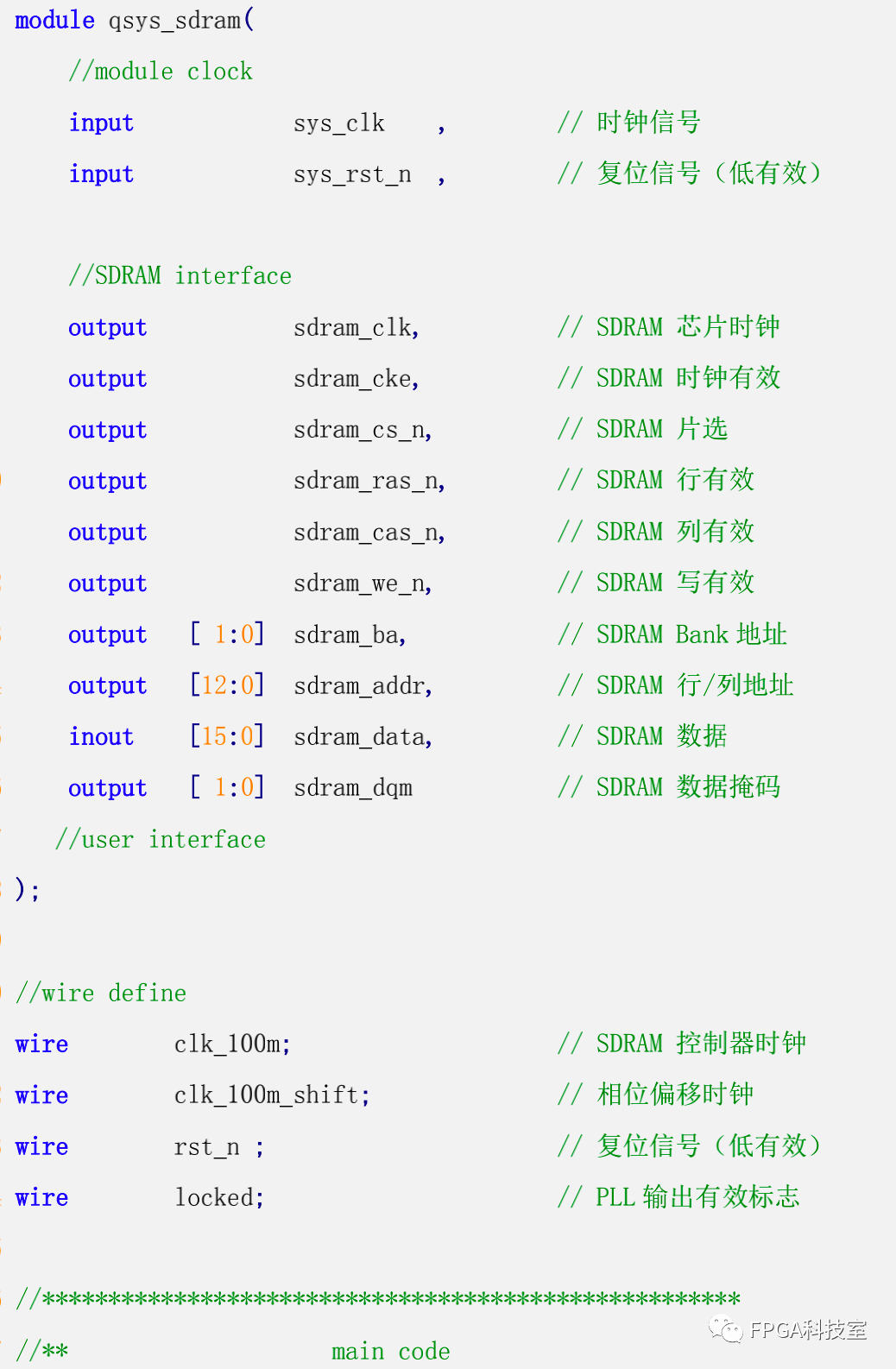

顶层代码如下:

从顶层代码可以看到,我们主要例化PLL和SDRAM控制器,PLL生成两个100MHz的时钟,其中一个偏移-75度用于驱动SDRAM芯片。

软件设计

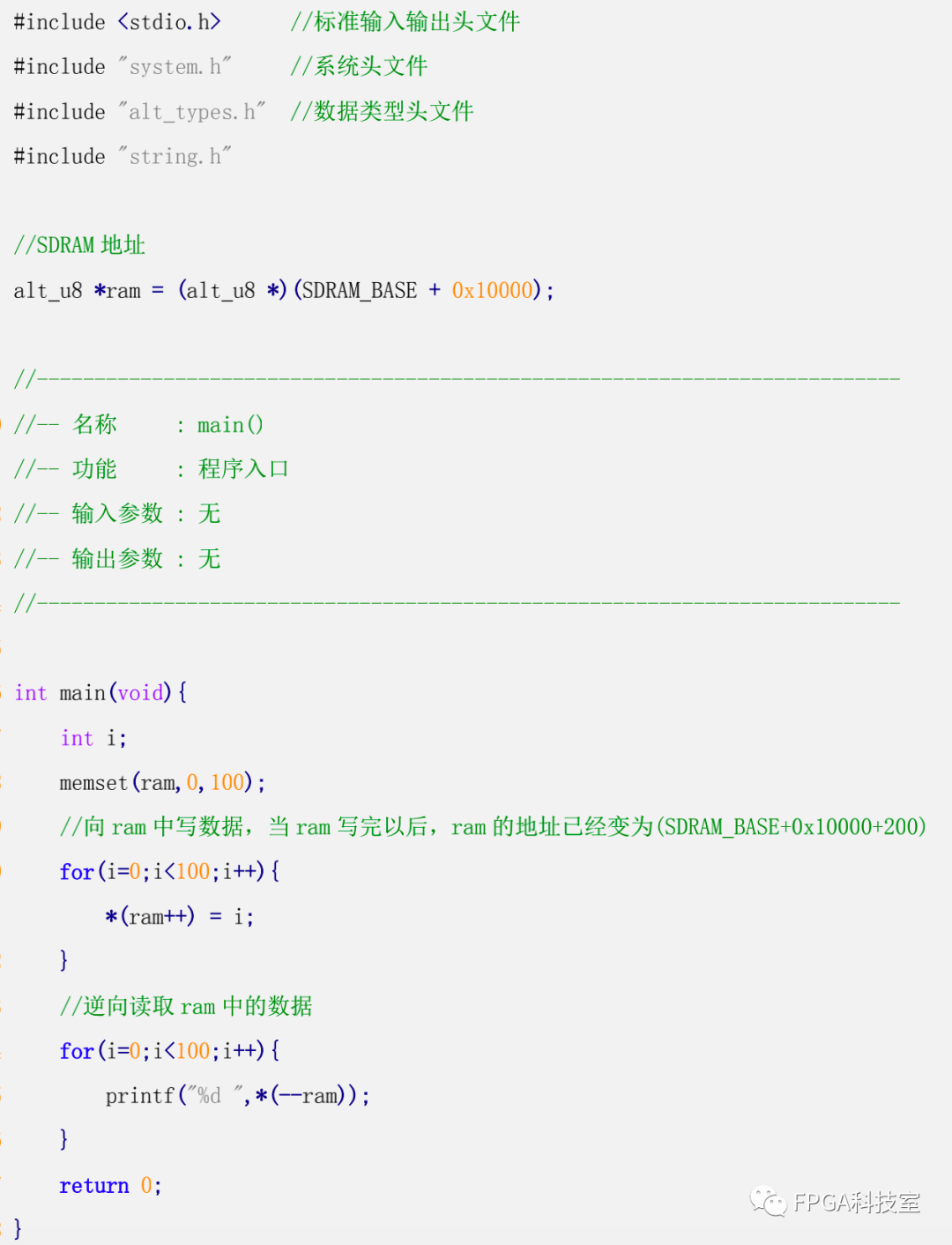

本实验的软件工程代码如下:

在代码中,首先定义了一个aut_u8型的指针ram指向SDRAM的基地址+0x10000,之后我们改变或读取指针指向的地址(SDRAM基地址+偏移地址)的值,就改变了SDRAM相应地址(偏移地址/2)的值。在主函数中,我们通过memset函数将从ram指向地址开始的100个地址的值全部清0,再通过一个for循环向从ram指向地址开始的100个地址的赋相应的值,最后再将这100个值逆向读取打印出来,这样就完成了SDRAM的读写操作。可以看出,通过SDRAM控制器的使用,对SDRAM的读写操作变得非常简单。

之所以对SDRAM的读写要偏移0x10000,是因为CPU程序的运行占用了从SDRAM基地址开始的部分内存,如果我们不做偏移直接从基地址开始读写,则很有可能破坏程序正常运行,0x10000这个值并不固定,只要别占用程序运行的内存就可以了。

下载验证

首先我们需要在Quartus II软件中将qsys_sdram.sof文件下载到开发板中;然后在Eclipse软件中将qsys_sdram_rw.elf文件下载进去。

qsys_sdram_rw.elf下载完成以后,我们的C程序会自动运行,同时在Nios II Console界面会显示程序的打印信息。图中可以看到从SDRAM中读出的数据为99到0,与我们写入的数据一致,说明本次实验下载验证成功。

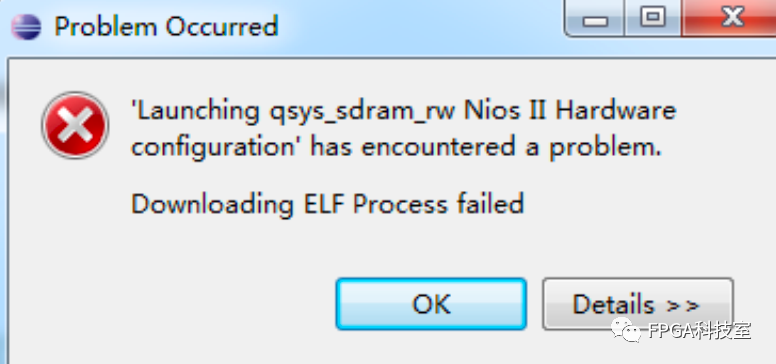

如果大家在下载elf文件的过程中工具提示错误,如下图所示:

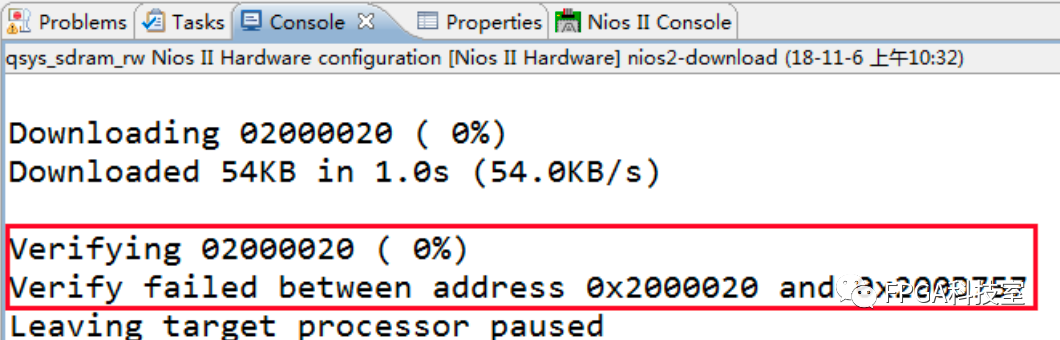

我们留意到在下载过程中,Console 会提示如下图所示的信息,说地址“0x2000020”到 “0x200D757”之间验证错误。

错误的这段地址并不固定,但它们在Qsys 系统中刚好处于 SDRAM 的地址范围内。此时,我们可以通过以下方式解决下载报错的问题。

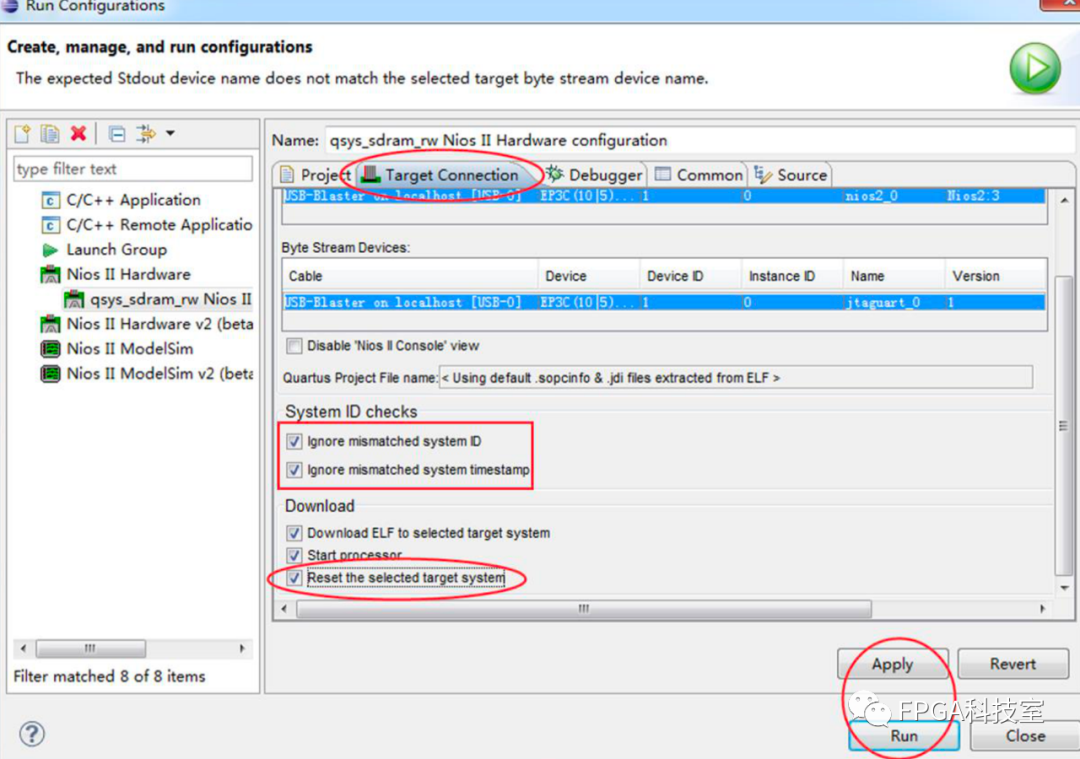

在Eclipse 中右击应用工程“qsys_sdram_rw”,在弹出的菜单中选择“Run As”

—>“Run Configurations”,会弹出“Run Configurations”配置页面,如下图所示:

在上图所示页面中的“Target Connection”标签页最下方,勾选“Reset the selected

target system”。在上图中,我们同时勾选了“Ignore mismatched system ID”以及“Ignore mismatched system timestamp”。设置完成后,点击“Apply”,最后点击“Run”来重新下载elf文件,这样在下载的过程中就不会报错了。

-

SDRAM

+关注

关注

7文章

422浏览量

55153 -

SDRAM控制器

+关注

关注

0文章

28浏览量

8131

原文标题:NIOS II处理器系统设计之SDRAM IP核应用

文章出处:【微信号:fpgaerZT,微信公众号:FPGA科技室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的SDRAM控制器的设计_SDRAM设计源码_明德扬资料

具有时间隐藏特性的数据块读写SDRAM控制器

图像处理系统中SDRAM控制器的FPGA实现

SDRAM控制器的设备与VHDL实现

使用Verilog实现基于FPGA的SDRAM控制器

基于FPGA的高速SDRAM控制器的视频应用

SDRAM控制器的设计

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

使用SDRAM控制器IP核对SDRAM进行读写操作

使用SDRAM控制器IP核对SDRAM进行读写操作

评论