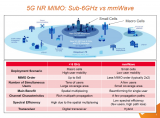

下一代5G网络的愿景是相比现有的4G网络,在容量、覆盖范围和连接性方面实现数量级提升,同时大大降低运营商和用户的每bit数据成本。

5G新无线电(NR)标准化第一阶段的重点是定义一种无线电接入技术(RAT),利用新的宽带频率分配(包括6GHz以下和24GHz以上的频段),以实现国际移动通信2020年及之后的愿景展望中提出的大峰值吞吐量和低延时。

图1:5G使用案例

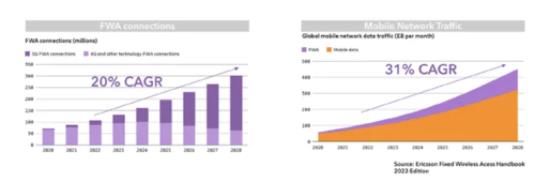

FWA部署

通过利用NR RAT,尤其是在毫米波频段方面实现的改进,移动网络运营商只需花费传统电缆和光纤到户设施的一小部分时间和成本即可向家庭、公寓和企业提供千兆固定无线接入(FWA)服务。FWA描述了一个集中的分扇区的BTS与多个固定或移动用户之间的无线连接,如图2所示。

图2:城市郊区环境中的FWA

以任意城市郊区为例,假设每平方公里有800个家庭,BTS站点间距离(ISD)为500m,运营商需要设置至少9个蜂窝站点,形成23个扇区。此时,每个扇区覆盖约35个家庭。如果提供1Gbps服务且网络超额利用率为目前的5倍,那么每个BTS的容量约为5Gbps,对应每个扇区平均BTS总容量为3Gbps,可以提供400MHz的带宽。再假设该郊区有35%的用户签约使用1Gbps服务,费用为100美元/月,则收入为14000美元/扇区/年,177000美元/平方公里/年。

由此可见,较大的覆盖范围对于成功实现FWA商业化至关重要,运营商也会要求设备供应商构建能够再最高规定限值下运行的BTS和CPE设备,以最大限度地提高覆盖率和盈利能力。这样一来,在运营商预期的成本、尺寸、重量和功率预算范围内构建符合这些目标要求的系统成为一大挑战。选择适当的前端架构和RF半导体技术是应对这一挑战的关键。

按列馈电阵列

新兴的毫米波有源天线均采用了两种主要平面架构,即「按列馈电阵列」和「全硅阵列」。

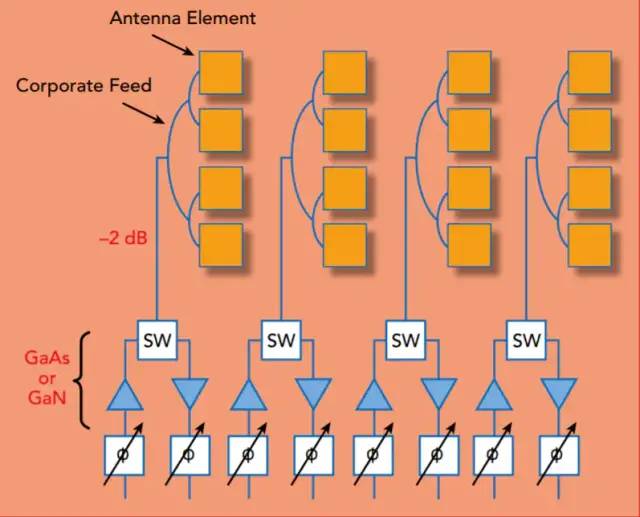

图3:射频前端位于阵外的按列馈电阵列

图3是按列馈电阵列的典型架构,在这种结构中,控制IC位于阵列外部、进行一对一驱动;列中所有单元增益/相位设置统一。控制IC与发射单元之间一般采取并联馈电结构。为简单起见,图3只展示了4*4的情况;实际生产中,行列可选取任意数字。

由于控制IC位于阵列外,因而可以采用高射频功率的GaAs或GaN来驱动阵列,使得每个单元都具备极高的射频功率,从而实现小阵列高发射EIRP。还可通过同时驱动天线柱的顶端和底端得到双极化阵列。

该架构的主要优点有:

每个单元都具备高射频功率;

每N列只需要N条控制IC射频电路;

由于IC位于阵列区域之外,不需要受到其尺寸限制。

最后一点对GaAs或GaN工艺来说非常重要,因为这两种半导体工艺的集成度有限,无法将控制元件整合到毫米波阵列的λ/2范围中。当然,这一点也随之为射频前端组件带来了插入损耗,因为控制IC需要通过馈线来传输发射单元的射频能量。

虽然发射端的插入损耗可以通过增加少量的有源单元即可弥补,但是接收端却要增加一倍的数量。造成这种情况的原因有两点:

接收端G/T值满足10log(N),其中N为阵列中单元个数,因此前端的损耗需要更多单元才能补偿。

根据馈电损耗和接收机噪声系数值的不同,馈电损耗对G/T的影响可能会超过1dB/dB。这意味着馈电损耗每产生1dB的变化,G/T便会降低1.5到2dB。纵然基于GaAs或GaN的按列馈电平面阵列具有较高的EIRP,但其接收性能很成问题。

按列馈电架构的另一个缺陷在于它只能支持一维波束导向缺少二维波束导向对于前期的5G固定无线接入应用来说还不算大事;但对中低轨卫星通信系统(LEO/MEO SATCOM)、移动卫星通信系统及城区密集的5G小基站而言,二维扫描能力是必需的,按列馈电架构便不合适了。

采用GaAs和GaN工艺实现控制IC还有一大问题便是无法对电路的振幅和相位变化进行自补偿。组件间|S21|和∠S21的变化分别可高达±2dB及±100°,不能自调便意味着要对阵列进行校准,对天线系统而言又是一笔巨大的成本开支。

此外值得注意的一点是,仅有少数全球性供应商能实现6寸GaAs和GaN工艺,在同样规模的生产力条件下,12寸的Si工艺显然成本要低很多,更何况6寸GaAs和GaN工艺还不够成熟。

阵列前端密度

早期的毫米波FWA BTS设计采用单独的单极化发射和接收天线阵列,随着相控阵单元之间的格栅间距越来越小,比如39GHz时已缩小到3.75mm。为了最大限度地减少馈电地插入损耗,需要将射频前端组件置于靠近辐射单元的位置,以便将多种功能整体集成在裸片上或多芯片模块封装内。为了实现所有功能的部署,我们要么成倍的提高阵列大小,以容纳更多的RFFE组件,要么使用GaN等具有高功率的半导体材料。

此外,在半导体材料的选择上,还要考虑耐温性。由于SiGe的可靠性在温度高于150°C时就会急剧下降,因此我们会选择额定温度为225°C的GaN-on-SiC,尤其是针对室外被动冷却式相控阵。

全硅阵列

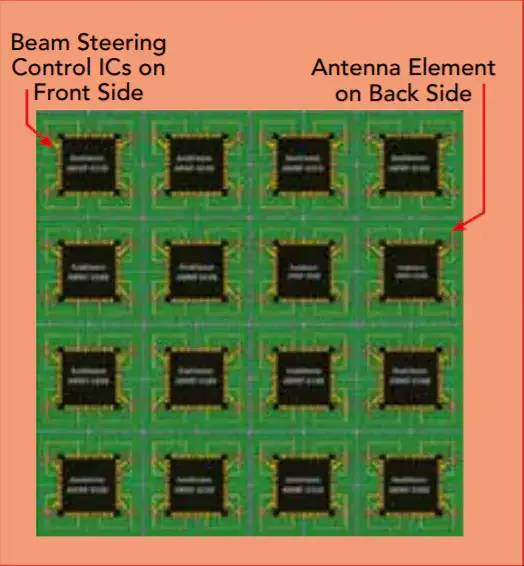

另一种有源天线架构是全硅阵列,其波束控制IC位于内部,如图4所示。

图4:全硅架构使得射频前端能够嵌入阵列内

波束导向控制IC包含了发射输出、接收输入、增益控制以及相位控制器件,全部集成在一块硅片上。芯片可以是单一发射器、单一接收器或是半双工发射/接收器。

该架构的优点在于可以将馈电损耗尽可能地降低,从而使发射EIRP和接收G/T的效率达到最大。同时,由于各个发射单元振幅和相位设置均不同,便可以实现LEO/MEO卫星通信、移动卫星通信和高密度城区所需的全幅二维扫描。同时,该架构只采用了硅工艺,产能高、成本最低、供应商充沛,无疑是另一大优势,而且硅材料集成度高,能够实现片上系统,因此可以植入一些功能来免去阵列校准的必要。这些对毫米波卫星通信和5G 有源天线等大规模市场而言非常重要,因为它们极需要压低成本。

波束成型技术

有源天线主要应用了三种通用的波束成型架构:模拟、数字及混合成型。

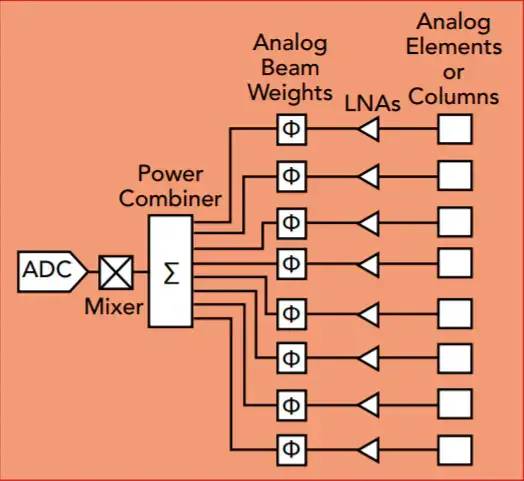

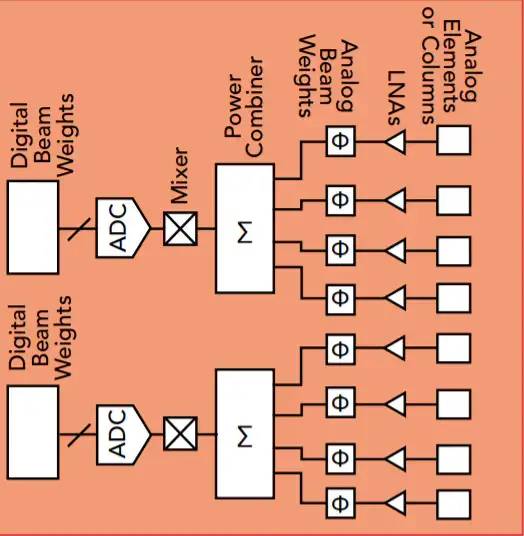

全硅架构下的模拟波束赋形通过对阵列中的每个单元加上模拟波束权重来实现(图5);按列馈电架构下则对每列加权。进行了模拟波束加权后,相干功率合成波束,后接一个频率合适的下变频器及ADC构成接收天线系统。

图5:模拟波束成型

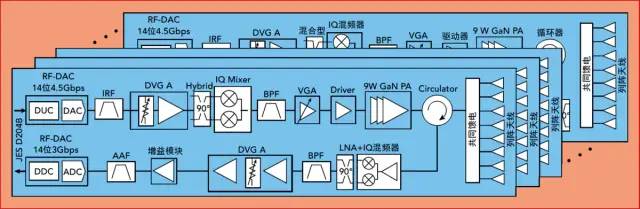

数字波束成型(图6)使用复杂的数字权重而非模拟权重,使用该技术在毫米波频率下的阵列过于密集,二维扫描就不适用了。因为按列馈电架构只能进行一维扫描,电子器件都位于阵列外部,所以可以应用数字波束赋形。同时,因为每个完整的接收器对应一列而非一个单元,所消耗的直流功率显著降低。

图6:数字波束成型

数字波束赋形还有几大难点,包括直流功耗高(尤其是在将大带宽数字化的情况下);信号通路复杂,其中大量I、Q数据点必须绕过阵列与数字处理器相连;本机振荡器(LO)信号通道需要控制在阵列内。不过,令人欣慰的是,如果这些困难都能迎刃而解,那这个架构便具有极大的发挥空间,因为无需更改硬件就可以形成多个波束及零点,同时全阵列的增益能影响到每个波束。

数字波束成型的热管理技术也颇具挑战,但是即将问世的新型GaN FEM(有限元建模)可帮助解决这个问题,再加上新一代RF采样DA/AD转换器实现的功耗节省、毫米波CMOS收发器的改进以及小信号集成度的提高,要不了多久,我们就能目睹更多全数字波束成型解决方案的部署。

图7:采用数字波束成型和现成商用组件的阵列设计

混合波束成型是模拟与数字波束赋形的结合(图8),其优势包括:

可以在毫米波频率下使用;

灵活度高,无需更改硬件即可动态形成许多波束和零点;

单个单元不需要完整的射频通路,每个子阵仅需一条。

图8:接收通路的混合波束成型

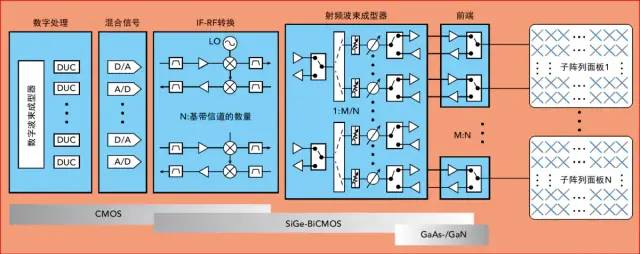

混合波束成型有源阵列的基本框图如图9所示。此处,N个基带信道用于驱动RF模拟波束成型器,进而将信号分为M条路径,并提供单独的相位和振幅。流行的设计比率是16或64个有源单元对应一个基带信道,不过也要视实际部署而定。

图9:采用混合波束成型的有源阵列

例如,如果采用热点小基站(或在CPE终端侧),那么一个1:16单面板就可以了;而一个宏BTS就需要1:64的面板,如果有24个子阵列,则对应256512个有源单元和4~8个基带信道。

RFFE半导体的选择

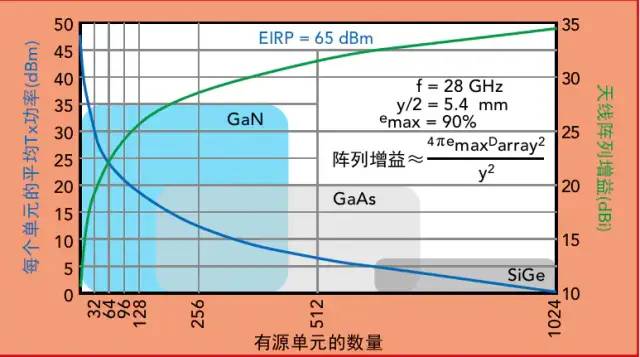

RFFE技术选项取决于系统的全向辐射功率(EIRP)和G/NF要求。这两者都由波束成型增益决定,而波束成型增益则由阵列大小确定,如图10所示。

图10:优化RFFE技术与阵列大小的关系

上图添加了最适合每种半导体技术的功率范围指示,功率限值根据每项技术的基准进行设置,从而避免采用会降低组件可靠性或效率的外来功率合成或方法。随着阵列大小越来越大(超过512个有源单元),每个单元的功率变得足够小,以便使用SiGe;相反,如果采用GaN技术,则实现相同的EIRP所需的信道数减少为1/8或1/16。

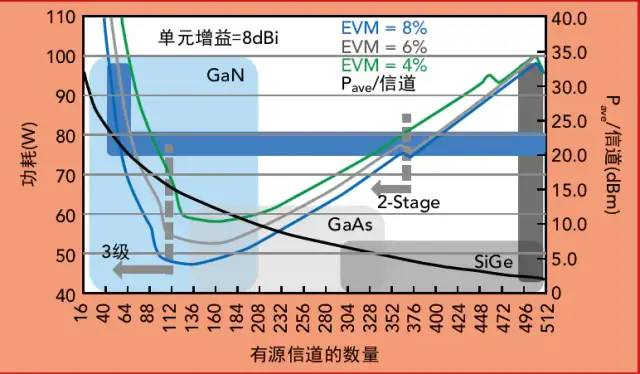

对于可实现64dBm EIRP的阵列,图11分析了波束成型器加前端的总PDISS与每个子阵列有源单元数量之间的关系。

图11:64dBm EIRP的系统功耗与阵列大小以及EVM的关系

从图中,我们可以看出,PA效率越低,随之波束成型器的效率则也越低。换句话说,选择将阵列大小增加8倍以实现完全采用SiGe的解决方案要付出一定的代价,因为输入信号被分为更多条路径,且需要使用线性偏置型耗电器件将信号放大。

相控阵的成本包括RF组件、印刷电路板材料和天线成本。采用化合物半导体前端可将阵列大小立即减少到1/8,同时PDISS不会增加。即使采用较低成本的印刷天线技术,也可以大大节省昂贵的天线基板材料成本。考虑到组件成本,目前采用4英寸晶圆制成的150nm GaN-on-SiC,每平方毫米成本仅为8英寸130nm SiGe的4.5倍。随着6英寸GaN生产线开始实现大批量生产,GaN的成本会降至SiGe的3倍。采用高功率密度型化合物半导体(如采用6英寸晶圆制成的GaN)时,可将完全采用SiGe的架构原始裸片成本降低35%。虽然每个组件的硅技术成本较低,但整个系统的成本明显更高。

基于Qorvo自行研发的FEM工具,在输出功率相当的情况下,GaN PA的裸片尺寸只有GaAs PA的1/4,同时不会降低增益,且效率稍有提高。考虑到采用LNA ,我们选择了90nm GaAsPHEMT工艺,因为它的NF略占优势。然而,在考虑使用额外的焊线和50Ω匹配网络后,其净改进只是几个十分之一dB。经过权衡分析我们得出,最好继续采用允许PA、LNA和T/R开关进行相互匹配的单片GaN设计。这样的设计风险更低,更易于装配和测试,且可采用尽可能紧凑的MMIC。系统热分析表明,GaN-on-SiC提供的更高结温对于被动冷却式阵列至关重要。

总结

FWA商业化很快就会实现,原因在于低成本频谱资源丰富、早期监管和标准制定工作得当,并且运营商有机会快速开拓一个新市场。剩下的挑战是要有可用的设备能够以合理成本闭合链路。

用于5G和卫星通信的有源毫米波天线在未来几年将实现空前的量产,两种主要的平面结构已经问世。一种基于GaAs或GaN工艺,IC位于阵列外;另一种基于硅工艺,IC位于阵内。

-

移动通信

+关注

关注

10文章

2614浏览量

69938 -

无线电

+关注

关注

60文章

2145浏览量

116601 -

毫米波

+关注

关注

21文章

1925浏览量

64887 -

5G网络

+关注

关注

8文章

1742浏览量

42450

原文标题:5G卫星通信与固定无线接入阵列

文章出处:【微信号:mwrfnet,微信公众号:微波射频网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

5G毫米波市场蓬勃发展的因素

苹果自研5G芯片获重要进展,毫米波技术暂缺席

5G毫米波测试助力突破高频段设备局限,实现高效外场测试

简述毫米波雷达的结构、原理和特点

爱立信与高通、Dronus共同完成使用5G毫米波无人机的制造与仓储用例测试

Qorvo收购Anokiwave,以硅晶创新推动毫米波5G商业化

用于5G和卫星通信的有源毫米波天线在未来几年将实现空前的量产

用于5G和卫星通信的有源毫米波天线在未来几年将实现空前的量产

评论