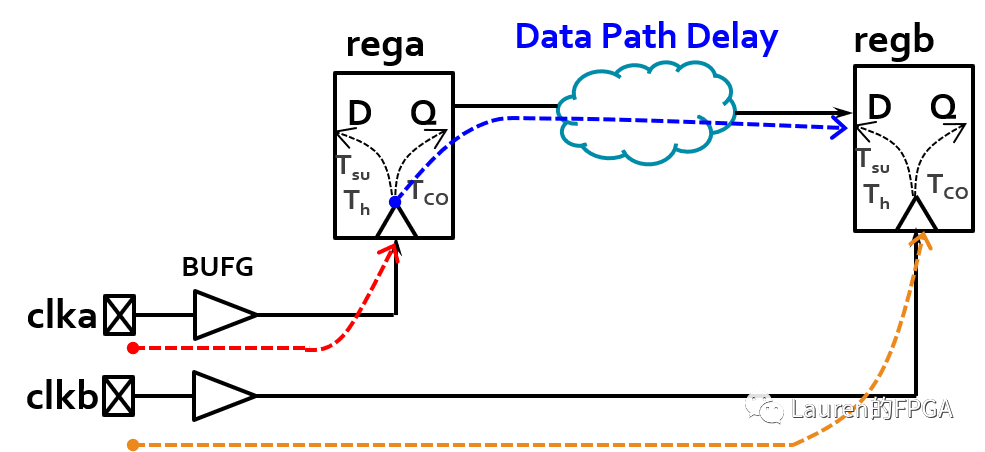

更为具体的时序报告信息如何从中获取,或者如何根据时序报告发现导致时序违例的潜在原因呢? 首先,我们要了解时序路径的构成,如下图所示。不难看出,对于一条典型的触发器+组合逻辑+触发器的时序路径,它由三部分组成:源时钟路径(发送时钟路径)、数据路径和目的时钟路径(接收时钟路径)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时序

+关注

关注

5文章

411浏览量

39019

原文标题:如何阅读时序报告

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

在FPGA开发中,时序收敛往往是项目后期最令人头疼的环节。许多工程师都有过这样的经历:RTL仿真通过,综合布线后却出现大量时序违例,为了满足时序不得不反复修改代码、调整约束,甚至重构设计。一

RGB时序灯条的工作原理讲解

图文配合讲解了RGB时序灯条的应用场景、什么是RGB时序灯条、信号格式与传输规则、灯珠芯片的工作流程、颜色与动态效果控制方式等

发表于 02-06 11:36

•0次下载

keil5使用中文路径安装.pack后缀报错的解决办法

安装完成

此时首先需要在keil5文件安装路径上改正文件名

此时再次安装.pack后缀文件时可能会发现两个问题:一个是默认打开方式改变了:

解决办法是在keil5安装路径下找

发表于 01-22 06:50

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

中,同一个系统时钟既传输数据也获取数据。考虑到板子路径延时和时钟抖动,接口的操作频率不能太高。

图1‑1 简化的系统同步输入SDR接口电路图

图1‑2SDR系统同步输入时序

上述时序

发表于 01-16 08:19

数字IC/FPGA设计中的时序优化方法

在数字IC/FPGA设计的过程中,对PPA的优化是无处不在的,也是芯片设计工程师的使命所在。此节主要将介绍performance性能的优化,如何对时序路径进行优化,提高工作时钟频率。

vivado时序分析相关经验

vivado综合后时序为例主要是有两种原因导致:

1,太多的逻辑级

2,太高的扇出

分析时序违例的具体位置以及原因可以使用一些tcl命令方便快速得到路径信息

发表于 10-30 06:58

使用Simcenter Micred Power Tester硬件对高功率多芯片模块散热路径中的裂缝面积进行定量说明

摘要热传导路径的退化是功率半导体封装最常见的失效机理之一。通常情况下,在界面接触区域,由于构成散热路径的不同材料之间的热膨胀系数不同,因而会产生热机械应力,从而引发焊接疲劳并导致裂缝

E203内核移植到FPGA开发板时出现时序违例的解决方式

在移植内核时,用VIVADO进行综合实现后会出现时序违例,如图:

虽然可以上板正常进行开发,但是还是想把这些违例解决下^_^

检查后,发现是 apb_adv_timer 这条路径报的违例,解决方式

发表于 10-27 07:32

时序约束问题的解决办法

slack 计算如下图所示:

所以 slakc 为负数时,说明路径的组合逻辑延时过长。解决办法有两个:第一个是降低时钟频率,第二个是将延时过长的组合逻辑拆成两个或者多个时钟周期执行。

无论 Setup

发表于 10-24 09:55

一文浅谈室内导航方案

一、方案背景 随着大型室内场所如商场、医院、机场、停车场等大型场馆日益增多,人们在复杂的室内环境中经常面临找路难,不知去向的问题,通过室内导航方案,能为用户提供精准、便捷的室内路径引导服务,轻松规划

一文知道时序路径的构成

一文知道时序路径的构成

评论