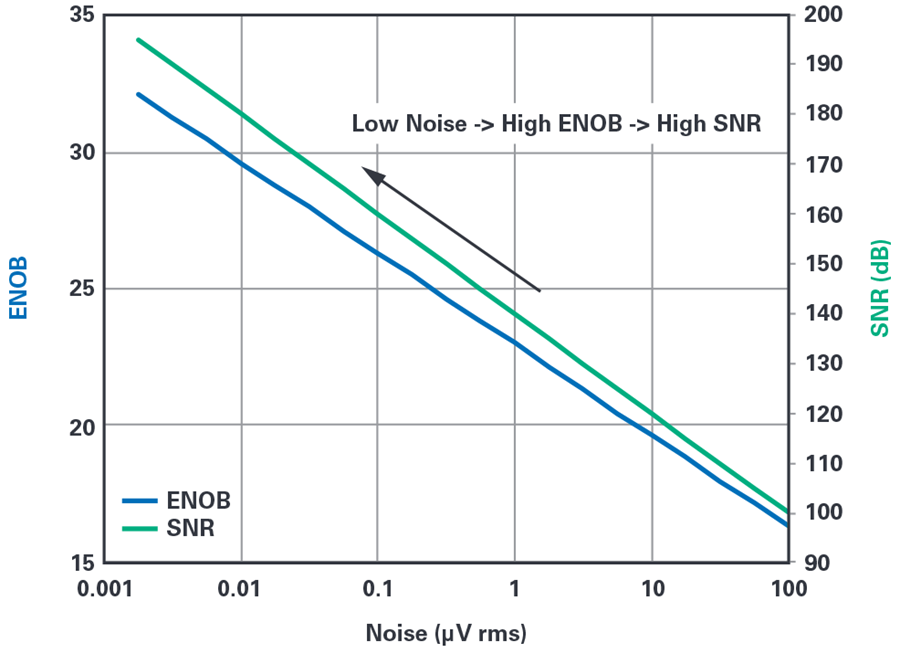

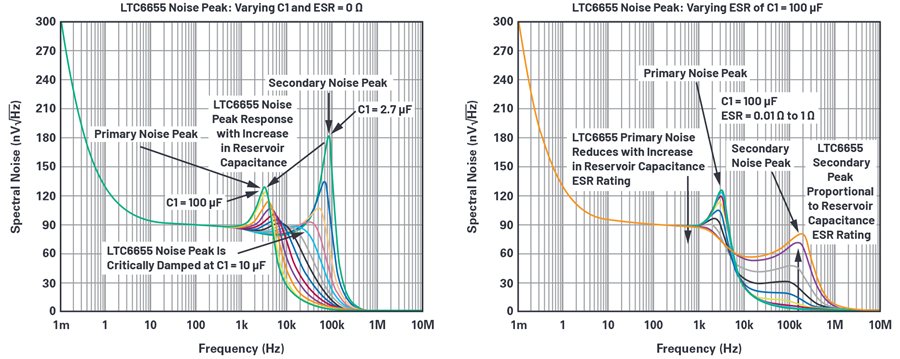

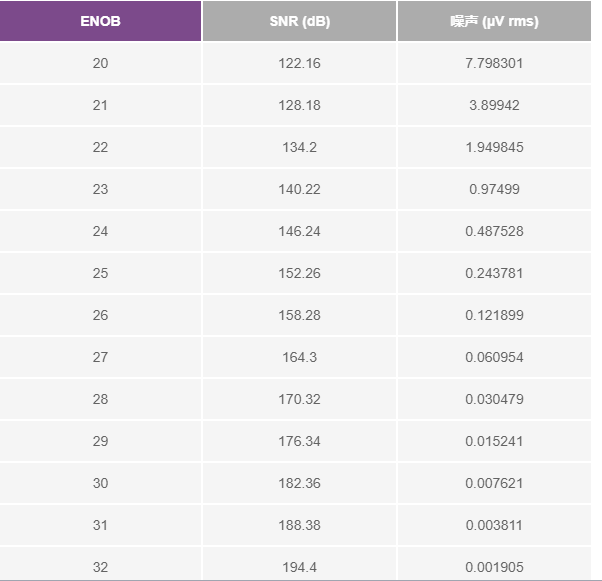

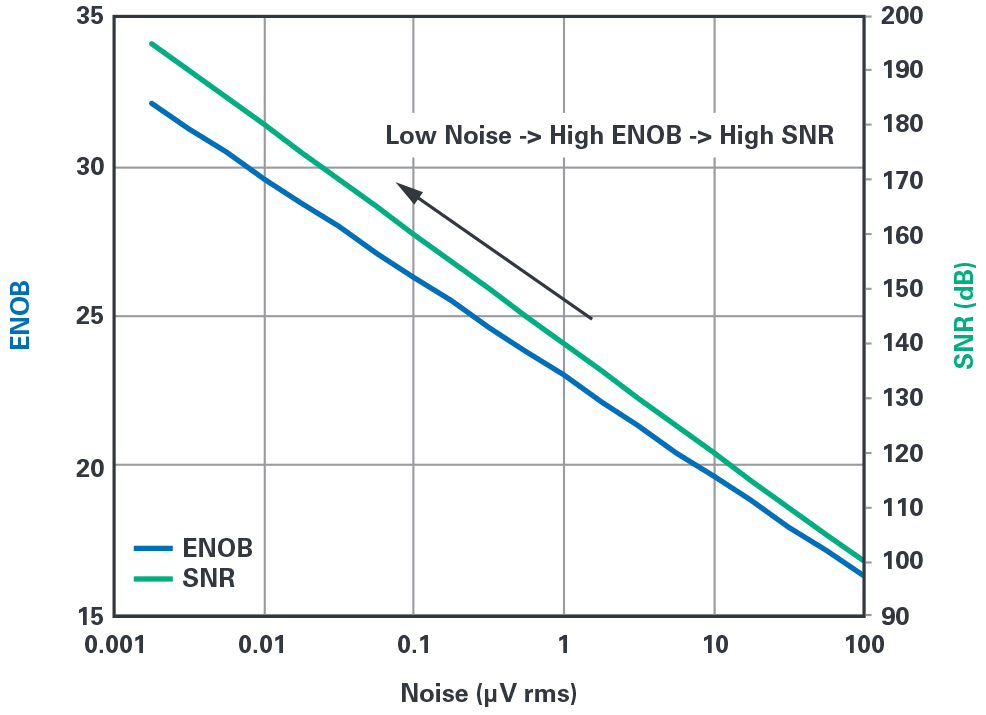

为了实现这种高分辨率,需要使用低噪声信号链。图1显示噪声与有效位数(ENOB)和信噪比(SNR)之间的关系。注意,噪声是基于基准电压(VREF) =5V,ADC输入设置为满量程范围来计算的。举例来讲,要实现25位分辨率,或者152dB动态范围,可允许的最大系统噪声为0.2437µVrms。

图1.噪声与ENOB和SNR。

基准电压设置输入模拟信号的限值,ADC可以解析该信号。公式1是ADC的理想转换函数,其中输出数字码(小数形式)通过模拟输入信号VIN、基准电压VREF和ADC位数N计算得出。

一般来说,ADC数据手册中的分辨率是基于输入短路技术得出,其中ADC输入连接至GND,或者ADC差分输入连接至共源极。ADC输入短路技术有助于确定ADC分辨率的绝对限值特性,方法是忽略ADC输入源噪声,消除VREF噪声的影响。结果确实如此,因为VIN设置为0V,使得VIN/VREF比也等于0V。

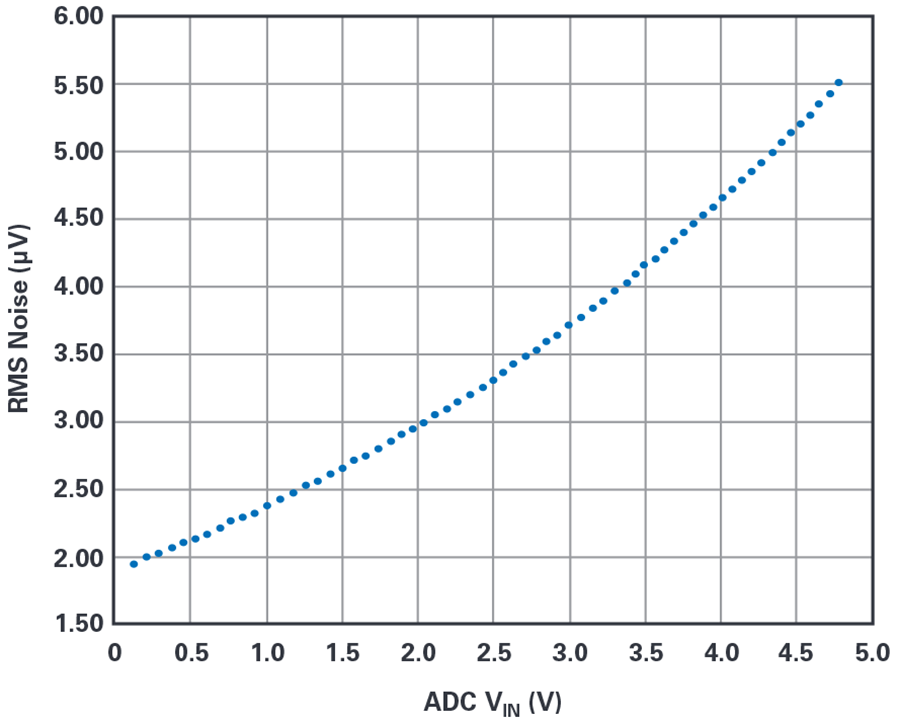

为了研究基准电压噪声对整体系统噪声的影响,图2显示了总系统噪声(rms)和ADC输入直流源电压之间的关系。实施本次测试期间,我们使用了AD7177-2 32位ADC,其VREF输入连接至LTC6655-5(5V),ADC输入则连接至低噪声直流源。ADC输出数据速率设置为10kSPS。注意,在整个ADC输入电压范围内,ADC噪声保持恒定(35nV/√Hz),但ADC直流输入源噪声增大(≤6nV/√Hz),与基准电压噪声(96nV/√Hz)相比,仍保持较低水平。如图2所示,总体噪声与ADC直流输入电压成正比。这是因为VIN(5V),ADC输入则连接至低噪声直流源。ADC输出数据速率设置为10kSPS。注意,在整个ADC输入电压范围内,ADC噪声保持恒定(35nV/√Hz),但ADC直流输入源噪声增大(≤6nV/√Hz),与基准电压噪声(96nV/√Hz)相比,仍保持较低水平。如图2所示,总体噪声与ADC直流输入电压成正比。这是因为VIN/VREF比随之增大,所以在ADC使用满量程输入时,VREF噪声主导整体系统噪声。信号链中各组件的噪声会以和方根(RSS)的方式叠加,导致曲线形状如图2所示。

图2.ADC VIN与rms系统噪声之间的关系。VREF设置为LTC6655-5。

为了实现25位或以上的高测量分辨率,即使是市面上最好的独立基准电压(具备低噪声规格)也需要获取一些帮助来衰减其噪声。添加外部电路(例如滤波器)可以帮助衰减噪声,以达到所需的ADC动态范围。

本文的其余部分介绍各种类型的低通滤波器,以及如何使用这些滤波器来衰减基准电压噪声。本文还会讨论滤波器设计技术和与滤波器有关的取舍。本文将以衰减基准电压噪声为基础,介绍两种类型的低通滤波器,分别是简单的无源RC低通滤波器(LPF)和基于有源信号流程图(SFG)的低通滤波器。电路性能部分会展示系统评估结果,用Σ-ΔADC表示测试。

使用无源低通滤波器来降低噪声

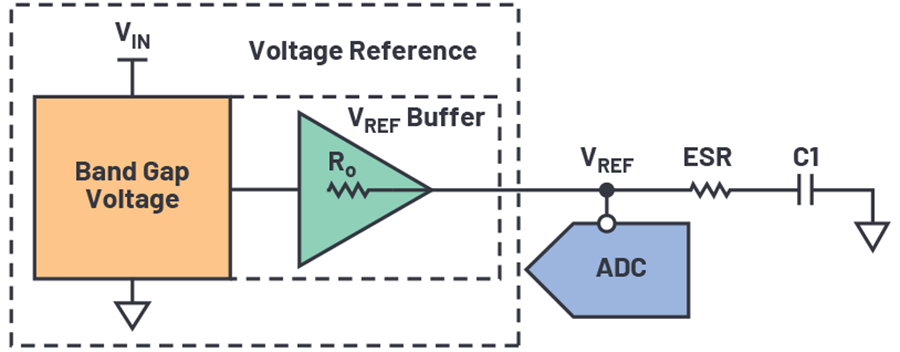

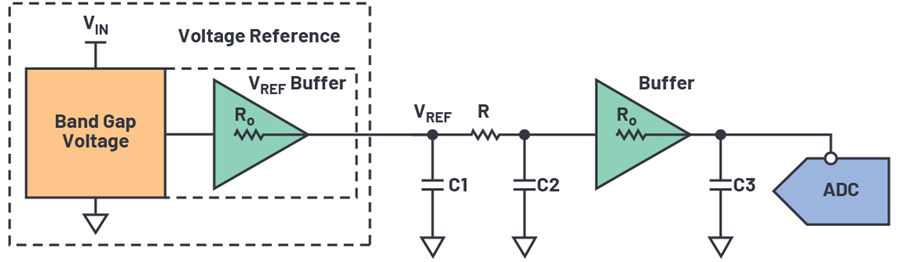

图3显示基准电压通过低通滤波器驱动ADC,该滤波器采用了外部储能电容C1、储能电容的等效串联电阻(ESR),以及基准电压运算放大器(运放)的输出阻抗。无源RC LPF截止频率由以下公式确定

从公式可以看出,带宽与电阻R和电容C成反比。

从公式可以看出,带宽与电阻R和电容C成反比。

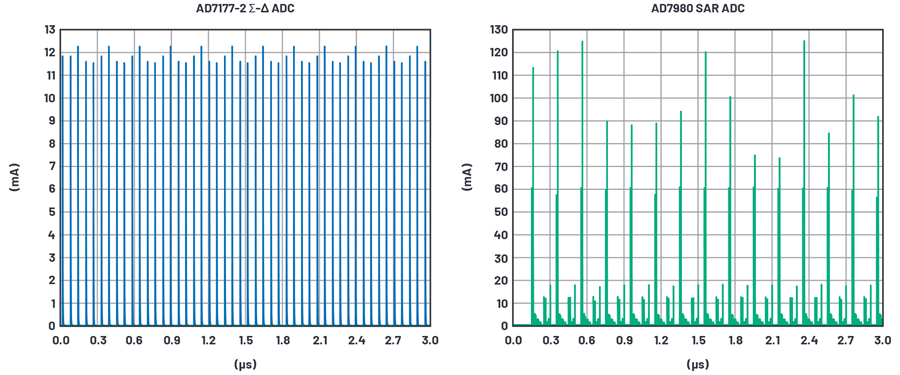

储能电容C1也可以用作本地电源存储器,用于补偿ADC基准电压电路突然要求负载电流发生变化时产生的电压尖峰。图4显示Σ-ΔADC AD7177-2和SAR AD7980ADC动态基准电流响应。

图4.AD7177-2和AD7980模拟动态基准电流响应。

用户可以选择C1电容的值来满足LPF截止频率要求,但是有些SAR ADC要求基准输入端采用至少10µF电容,以保证正常运行。最小的10µF C1电容可以降低基准电压源缓冲器的相位裕量。随着相位裕量降低,缓冲器反馈不再为负。在单位增益交叉频率附近的信号与输入信号同相反馈。1这导致闭环响应在交叉频率附近出现噪声峰值。由于源自截止频率(–3dB点)的带宽最高达到16MHz,总集成噪声(rms)由噪声峰值主导。即使基准电压储能电容C1作为噪声滤波器使用,并补偿电压尖峰,也需注意噪声峰值。图5显示LTC6655基准电压的噪声峰值,该峰值因储能电容C1引起。噪声峰值幅度由储能电容的值和其ESR额定值决定。

图5.LTC6655基准电压噪声峰值密度。

大多数基准电压都具备复杂的输出级,以驱动适用于ADC基准电压源电路的大型负载电容。例如,LTC6655输出级设计用于采用设置为10µF的储能电容来执行关键衰减。LTC6655的储能电容设置为最小2.7µF、最大100µF时,会产生噪声峰值。

VREF输出储能电容的等效串联电阻会消除主要的噪声峰值,但是会在100kHz和以上频率时产生二次噪声峰值。究其原因,可能是因为电容的ESR产生零噪声,可以改善相位裕量和降低主要噪声峰值。但是,这个零噪声与LTC6655固有的零噪声结合在一起,产生了二次噪声峰值。注意,图5所示的噪声响应只适用于LTC6655基准电压源。

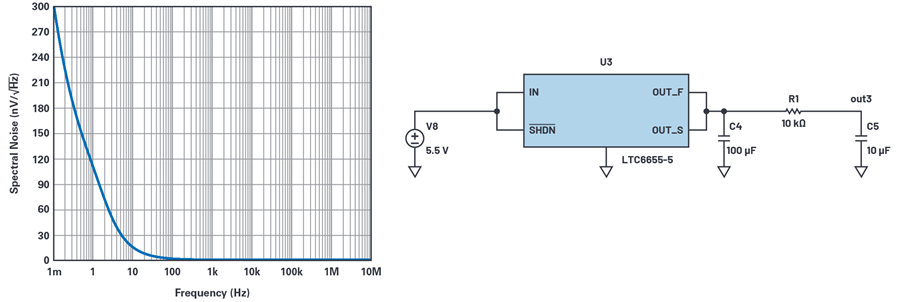

过滤基准电压噪声、消除噪声峰值,以及合理驱动ADC的另一种解决方案是添加无源RC LPF,然后添加缓冲器。通过添加缓冲器,我们可以隔离LPF和ADC基准电压源输入电容之间的设计限制。参见图6。

图6.无源RC LPF,后接缓冲器。

将无源RC LPF截止频率设置为远低于单位增益交越频率,不止可以降低宽带和低频率噪声,还可以避免出现噪声峰值。例如,图7显示LTC6655噪声响应,其中C1=100µF(ESR=0Ω),后接无源LPF,其中R=10kΩ、C2=10µF(ESR=0Ω),在1.59Hz时产生极点。

增大低通滤波器电阻R可以帮助实现低截止频率,但是也可能会降低精密基准电压的直流精度。添加无源RC LPF时,用户还必须考虑对负载调整和VREF缓冲器响应(τ=RC)的影响,在驱动ADC时,这会影响其瞬变性能。

要达到所需的瞬变性能,建议如图6所示使用缓冲器。选择缓冲器时,要考虑的关键规格包括超低噪声、支持高负载电容的能力、低失真、出色的压摆率,以及宽增益带宽。建议采用的缓冲器为ADA4805-1和ADA48071。

图7.LTC6655-5,后接无源RC LPF噪声响应。

使用有源LPF降低噪声

表1指明了所需的动态范围和必须满足的可允许最大系统噪声要求,以实现所需的ENOB ADC分辨率。根据ADC带宽,按20dB/10倍衰减的单极低通滤波器可能无法达到所需的宽带噪声消除。级联无源低通滤波器构建一个阶梯结构,可以生成更高阶的滤波器,但每个部分的输入阻抗将是前一部分的负载。这会降低精密基准电压的直流精度。但是,基于有源组件设计更高阶的LPF可以在输入和输出之间提供良好的隔离,最大限度避免基准电压直流精度下降,并提供低输出阻抗来驱动ADC的基准电压源电路。

表1.条件:VREF= 5 V,ADC输入设置为满量程范围

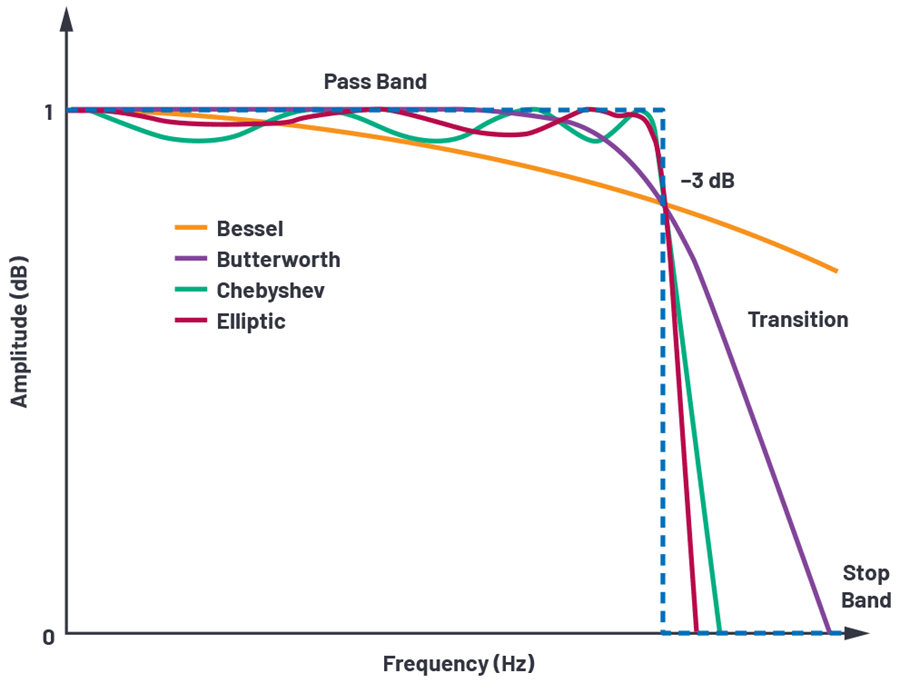

不同类型的有源低通滤波器,例如,Bessel、Butterworth、Chebyshev和elliptic,具体如图8所示。采用平坦带通或无纹波带通,可以最大限度地避免降低精密基准电压的直流精度。在所有滤波器类型中,基于Butterworth拓扑的LPF设计可以实现平坦的带通和陡峭的衰减。

图8.滤波器振幅响应示例。

有源低通滤波器设计技巧

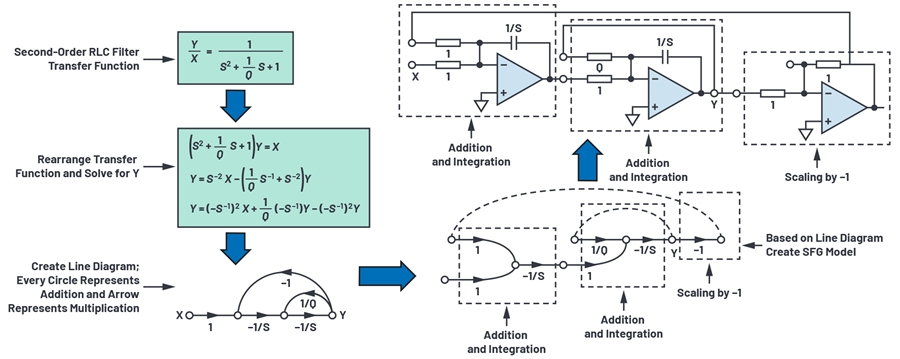

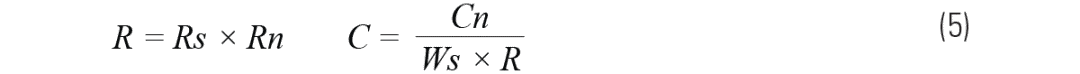

信号流程图是用图形表示源自一系列线性公式的系统。SFG用于连接转换函数和对应的系统电路拓扑。该理论可用于基于有源电路设计模拟滤波器。SFG滤波器设计方法的主要优点在于:衰减系数Q和截止频率都可以单独控制。SFG LPF可以帮助衰减噪声和提高信噪比,但会导致物料成本(BOM)、PCB区域和功率增加。此外,SFG LPF可以影响基准输出电压与温度,导致产生微小PPM误差,造成直流精度下降。图9所示为二阶低通滤波器示例,该滤波器采用SFG方法,从转换函数转换至电路块。扩展电阻(R)和电容(C)针对截止频率实施配置(请参见公式5)。

图9.基于SFG方法实施有源RC低通滤波器。

有关信号流程图理论的更多信息,请参考Addison-Wesley出版的Feedback Control of Dynamic Systems(《动态系统反馈控制》)。

其中

Rs表示比例因子

Cn表示比例因子

Ws表示截止频率(Rad/s)

以下是一个计算示例,用于说明如何设计二阶0.5Hz截止频率SFG低通Butterworth滤波器:

-

为了保持简明,选择Rs=1Ω,Cn=1F。

-

选择Fs=0.5Hz,以最大化宽带噪声抑制效果。Ws=2×π×0.5=3.141rad.

-

设置衰减因子Q=0.71。选择此值可实现平坦的带通和陡峭的衰减,以反映Butterworth拓扑。

-

R、C和Rq值基于迭代流程选择,以实现较低热噪声和可用于表面贴装的组件值。

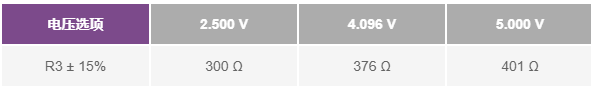

LTC6655LN简介

考虑到与RC LPF和SFG LPF有关的取舍,更好的解决方案是如图10所示,将低通滤波器安装在基准电压的集成式低噪声缓冲器之前。这种布局不但会减小PCB面积,还不影响基准电压缓冲器的响应。使用快速稳定,具有高输入阻抗,能够灌电流和拉电流的基准电压缓冲器,有助于解决负载调整不良的问题,保持直流精度,以及改善瞬变性能。LTC6655LN采用了这种架构。它配有降噪引脚,可以帮助降低宽带噪声,支持使用集成式输出级缓冲器。LTC6655LN内置R3电阻(参考图10),允许用户在降噪(NR)引脚位置连接外部电容,以创建低通滤波器。采用LTC6655LN架构时,用户可以根据系统要求配置低通截止频率。

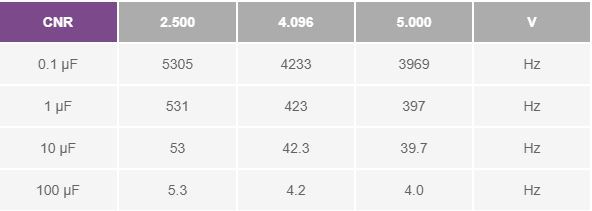

表2.3 dB截止频率,适合连接至NR引脚的电容实现不同值

LTC6655LN RC LPF连接至缓冲器的非反向节点,该节点是此器件最灵敏的引脚。必须做好预防措施,应选择极低漏电流类型的外部电容,以防泄漏电流从R3电阻漏出,导致直流精度下降。此外,R和C之间的变化相互无关,所以RC时间常数和LPF截止频率会因为流程、电压和温度(PVT)差异而产生变化。

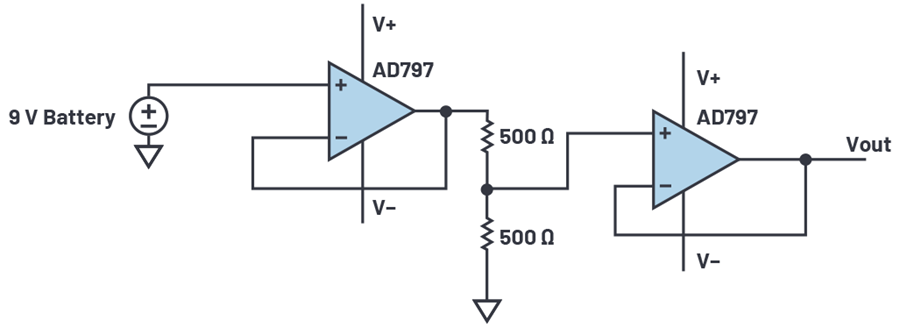

表3.3种电压选项的R3的电阻值

基准电压(例如内置LPF的LTC6655LN)提供最佳解决方案,用于简化噪声滤波器设计,消除对外部缓冲器的需求,以驱动ADC基准电压电路。

图10.LTC6655LN方框图。

测试电路描述

AD7177-2精密ADC被用于确定LTC6655/LTC6655LN加10uF NR电容以及LTC6655后接SFG滤波器的标准性能,。AD7177-2是高分辨率32位低噪声快速稳定2通道/4通道∑-∆模数转换器,用于实现低带宽输入。AD7177-2集成可编程数字带通滤波器,允许用户控制5SPS至10kSPS的输出数据速率(ODR)。

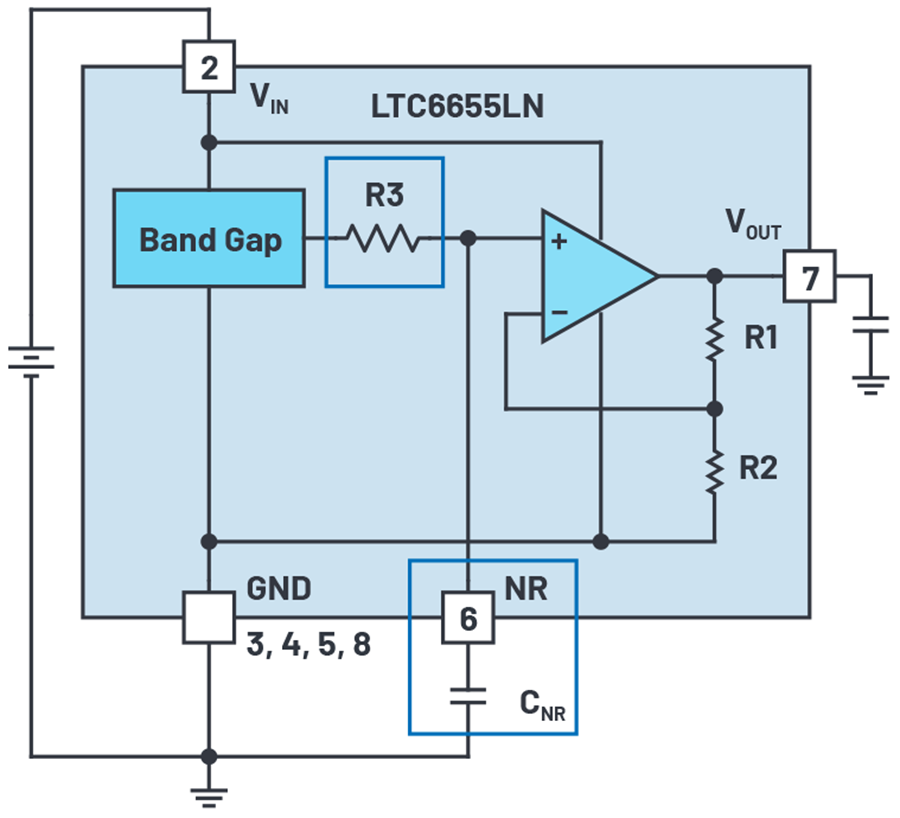

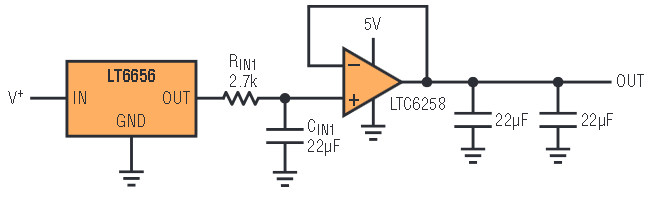

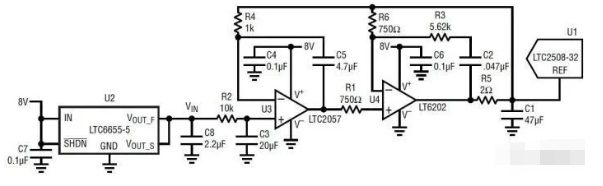

设计SFG LPF(图11)时用到的组件包括2个ADA4522-1运算放大器、1个AD797运算放大器、多个25ppm表贴式电阻、多层表贴式陶瓷电容,以及1个10µF WIMA薄膜电容。ADA4522是一款轨到轨输出运算放大器,宽带噪声密度为5.8nV/√Hz,闪烁噪声为177nVp-p。AD797是一款低噪声运算放大器,具备0.9nV/√Hz宽带噪声、50nVp-p闪烁噪声、20V/µs出色压摆率,以及100MHz增益带宽,因此适合驱动ADC。

图11.SFG LPF。

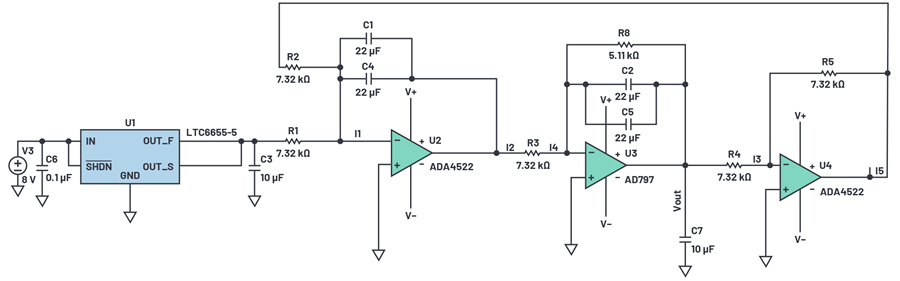

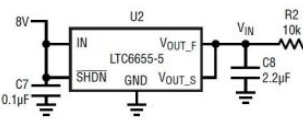

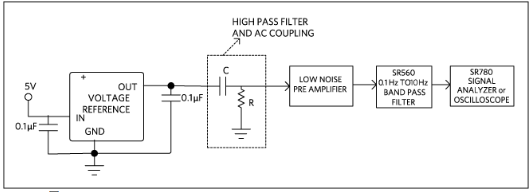

在使用LTC6655和带有AD7177-2的LTC6655LN时,为了正确评估性能,需要使用整体噪声低于ADC基准电压和ADC噪声的直流源。因此,会使用理想源,也就是9V电池电源,具体如图12所示。

图12.低噪声直流源。

电路性能

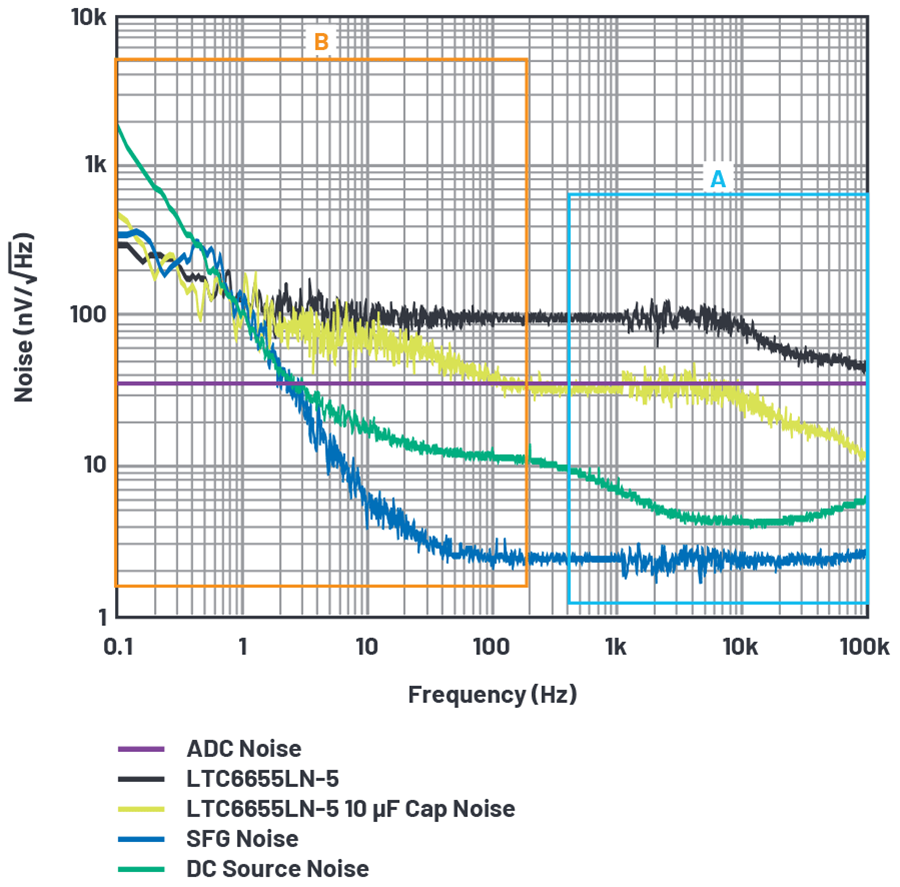

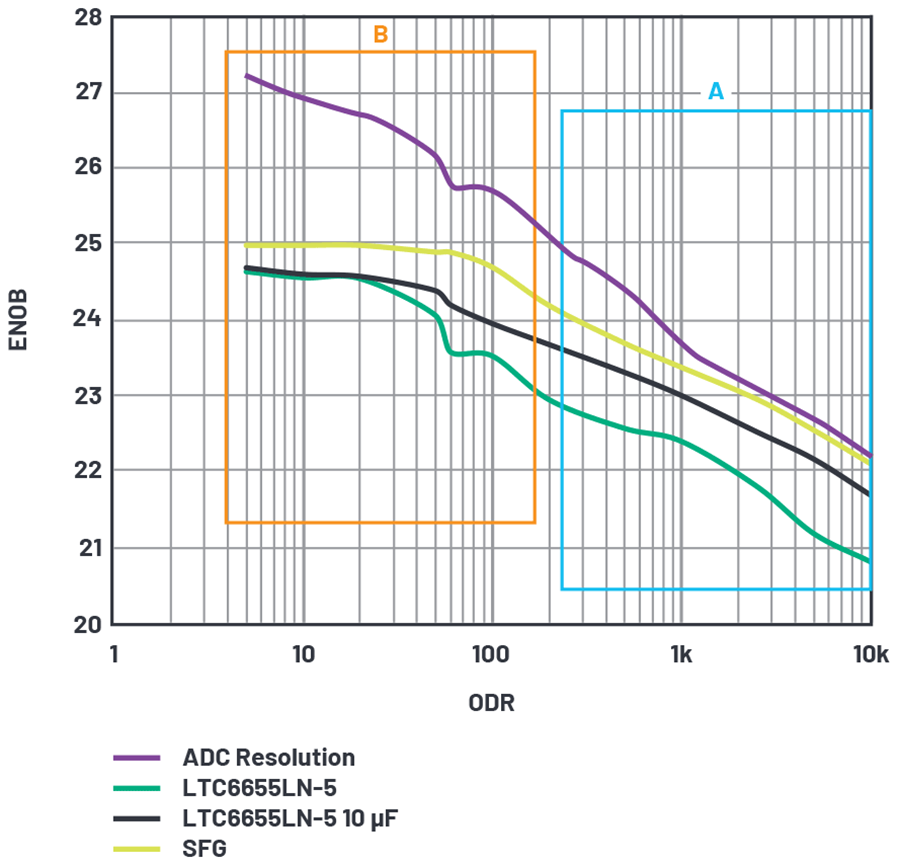

图13显示噪声谱密度,图14显示输出数据速率(ODR)和ENOB,描述AD7177-2的性能,它的VREF输入连接至LTC6655或者采用10uF NR电容的LTC6655LN或者使用SFG方法滤波的LTC6655。关于在1 kHz时噪声谱密度的比较结果,请参见表4。图13和图14都有两个重要区域。

表4.1 kHz时的噪声谱密度比较结果

区域A:

噪声谱密度图(图13)显示,ODR为500SPS及以上时,滤波LTC6655(SFG)和ADC直流输入源噪声远低于ADC的噪声,因此,ADC可以最大限度的去实现其最大性能,具体如图14中的区域A所示。从ODR、ENOB和噪声谱密度图中可以看出,在区域A中,总集成噪声(rms)的增高会妨碍信号链达到25位测量分辨率。

区域B:

在这个区域中,噪声谱密度图(图13)显示,三个基准电压选项和直流源的闪烁噪声升高,整体的系统噪声则受直流源噪声主导。区域B中的闪烁噪声升高,会导致测量性能和ADC可以实现的最大性能之间的ENOB偏差增大(图14)。

根据ODR和ENOB图,滤波LTC6655(SFG)的ODR在小于等于20SPS时可以实现25位分辨率,带10µF NR电容的LTC6655LN-5和LTC6655实现的分辨率最高不超过24.6位。

图13.噪声谱密度。

图14.ODR与ENOB。

下方的表5汇总介绍AD7177-2ADC的性能,其中VREF输入连接至LTC6655或者带10µF NR电容的LTC6655LN,或者连接至滤波LTC6655(SFG)。在ADC输入连接直流源,VREF输入连接至LTC6655时,零缩放栏确定AD7177-2可以实现的最佳动态范围。在ADC输入设置为近乎满量程时,带10 μF NR电容的LTC6655LN-5的动态范围平均增大4dB(与LTC6655相比,ODR范围为10000SPS到59.96SPS)。另一方面,滤波LTC6655(SFG)的动态范围平均增大7dB(与LTC6655相比,ODR范围为10000SPS到59.96SPS)。在59.96SPS以下,动态范围区域的变化不大,由ADC输入直流源产生、占主导作用的低频率闪烁噪声是导致差异的主要原因。

与LTC6655/LTC6655LN相比,将10µF电容连接至LTC6655LN的NR引脚时,在1kHz时可以将宽带噪声降低62%,滤波LTC6655(SFG)可以将宽带噪声降低97%。

精密系统如果想要实现25位或以上的分辨率,必须非常重视基准电压噪声。如图2所示,VREF噪声占系统噪声的比例与ADC满量程的使用率成正比。本文显示,在精密基准电压中添加滤波器可以衰减VREF噪声,从而降低整体的系统噪声。后接SFG滤波器的LTC6655基准电压可以将未配备滤波器的LTC6655的宽带噪声降低97%。但这会额外增加物料成本,增大PCB面积和功耗,降低几PPM的直流精度,且导致精密基准电压源输出随温度发生变化。在考虑与SFG LPF有关的取舍时,LTC6655LN采用简单设计,功耗低,只需要使用单个电容来降低宽带噪声,且无需使用外部缓冲器来驱动ADC。带10µF NR电容的LTC6655LN与不带滤波器的LTC6655相比,其宽带噪声降低62%。因此,用户现在可以使用内置的LTC6655LN低通滤波器来让精密系统实现所需的分辨率。

文章出处:【微信公众号:亚德诺半导体】欢迎添加关注!文章转载请注明出处。

-

噪声

+关注

关注

13文章

1118浏览量

47377 -

基准电压

+关注

关注

3文章

83浏览量

23124

原文标题:为何基准电压噪声非常重要?看了这篇你就明白了

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于LT6656精准串联电压基准的低噪声基准

高质量的电压基准设计

电压基准噪声对增量累加ADC中的DC噪声性能的影响

DSPICFJ128GP802做音频晶体离针远一点重要吗?

滤波器电路图有吗?该如何降低基准输出噪声?

775噪声测量系统低噪声电压基准

基准电压噪声重要吗?看完你就明白了!

基准电压噪声重要吗?看完你就明白了!

评论