第二篇以德州仪器(TI)的高速ADC芯片——ads52j90为例,介绍完了4线SPI配置时序。本篇将以该芯片SPI结构为例,具体介绍如何利用verilog实现4线SPI配置时序。

无论实现读还是写功能,都先要提供SCLK。假如FPGA系统工作时钟40MHz,我们可以利用计数器产生一个n分频的时钟作为SCLK,本例中n取8,SCLK频率5MHz。SCLK产生的代码如下:

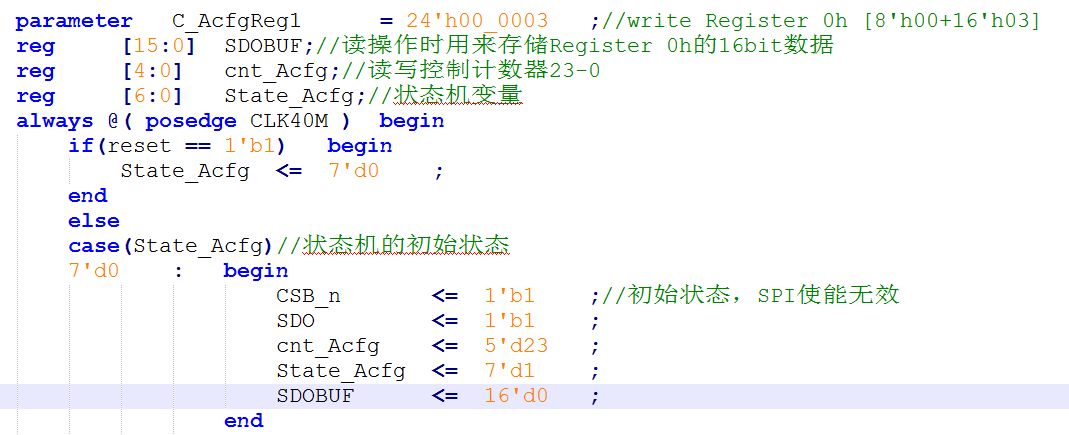

SCLK时钟有了,接下来我们建立一个状态机实现读和写功能:

初始化状态的下一个状态就是写寄存器操作了,每次SCLK的上升沿写入数据:

写完一个寄存器参数,CSB先拉高。接下来在进入下一个状态,本篇例子下一个状态的操作是读取对应寄存器地址的数据。我们首先需在SCLK的上升沿写入8bit的寄存器地址,接下来在SCLK的下降沿读取16bit的数据。

到此,读写操作都完成了。代码上的注释可以便于大家理解,大家还可以仿真看一下波形加深理解。

-

Verilog

+关注

关注

28文章

1351浏览量

110139 -

SPI

+关注

关注

17文章

1707浏览量

91696 -

ADC芯片

+关注

关注

3文章

78浏览量

20316

原文标题:FPGA通过SPI对ADC配置简介(四)---Verilog实现4线SPI配置

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DAC7568按数据手册上要求的SPI时序不能配置,内部参考是否也没有输出,为什么?

Verilog 测试平台设计方法 Verilog FPGA开发指南

KeyStone架构串行外设接口(SPI)手册

能否在纯fpga上通过verilog实现SPI控制器去配置adc12dj3200?

ADS127L11配置ADC使用外部时钟以及FILTER[4:0]都不成功,为什么?

ADS127L11使用4线spi不管怎么配置寄存器,示波器看到ADC的drdy脉冲周期始终是400K,怎么回事?

瀚海微SD NAND之SD 协议(42)SPI总线时序

如何利用Verilog-A开发器件模型

如何利用verilog实现4线SPI配置时序

如何利用verilog实现4线SPI配置时序

评论