孔径延迟,英文释义为Aperture delay,是由于采样保持开关关断需要一定时间,相当于在采样时钟上引入一个小延迟,使得采集的信号为实际信号的延迟版本,因此,若孔径延迟是固定常数,则它并不产生误差,只会在时钟输入或模拟输入中起固定延迟的作用。

但若是两个AD转换器同步采样应用,由于不同AD转换器的孔径延迟是有差异的,可能给高摆率的信号带来误差,那么两个AD转换器必须精密匹配,必须适当调整采样时钟相对ADC的相位,从而消除孔径延迟不匹配问题。

二、什么是ADC的孔径抖动,它与孔径延迟一样吗?

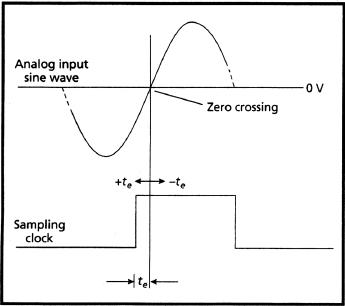

前文我们理解了孔径延迟,若其存在样本间变化(即,不同的输入信号带来不同的孔径延迟),则会产生电压误差,在开关断开时刻,这种样本间变化称为孔径抖动,英文释义为Aperture jitter,或叫孔径不确定性英文释义为Aperture uncertainty,如下图所示,从而带来孔径抖动误差(Aperture jitter error),用均方根皮秒(ps rms)来衡量。

图1 孔径抖动

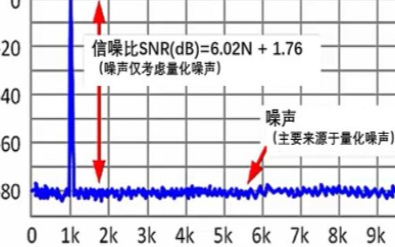

三、孔径抖动对ADC信噪比的影响

下面仅单独考虑孔径抖动对ADC信噪比的影响。

假定对n位的ADC输入频率为f的满幅度正弦信号,表示为下式:

V(t)=V0*sin(2πft)

由于时钟抖动引起的SNR可以简述为下式:

SNRj=-20log2πftj

tj表示抖动时间的均方根。

可见,SNR随输入信号的频率减小,但与输入信号的幅度无关,可以简单计算一下,一个输入信号频率为f=24M的ADC,它的抖动时间造成SNR降低情况如下:

tj=0.5ps,SNRj=82.45dB

tj=1ps,SNRj=76.43dB

tj=3.48ps,SNRj=65.6dB

tj=5ps,SNRj=62.45dB

可以发现,SNR随孔径抖动时间增加下降很快,可知其带来的影响非常严重,尤其是在高速ADC应用中,其带来的信噪比衰减更快。

-

adc

+关注

关注

98文章

6495浏览量

544441 -

信噪比

+关注

关注

3文章

260浏览量

28618

发布评论请先 登录

相关推荐

时域时钟抖动分析(上)

详解ADC的信噪比公式

ADC重要的信噪比公式是怎么来的?

高速ADC在低抖动采样时钟电路设计中的应用

孔径抖动对ADC信噪比的影响

孔径抖动对ADC信噪比的影响

评论