早期的CPU是通过提高主频来提升CPU的性能,但是随着频率“红利”越来越困难的情况下,厂商开始用多核来提高CPU的计算能力。多核是指一个CPU里有多个核心,在同一时间一个CPU能够同时运行多个线程,通过这样提高CPU的并发能力。

内存一致性模型(memory consistency model)就是用来描述多线程对共享存储器的访问行为,在不同的内存一致性模型里,多线程对共享存储器的访问行为有非常大的差别。这些差别会严重影响程序的执行逻辑,甚至会造成软件逻辑问题。在后面的介绍中,我们将分析不同的一致性模型里,多线程的内存访问乱序问题。

目前有多种内存一致性模型:

顺序存储模型(sequential consistency model)

完全存储定序(total store order)

部分存储定序(part store order)

宽松存储模型(relax memory order)

在后面我们会分析这几个一致性模型的特性

在分析之前,我们先定义一个基本的内存模型,以这个内存模型为基础进行分析

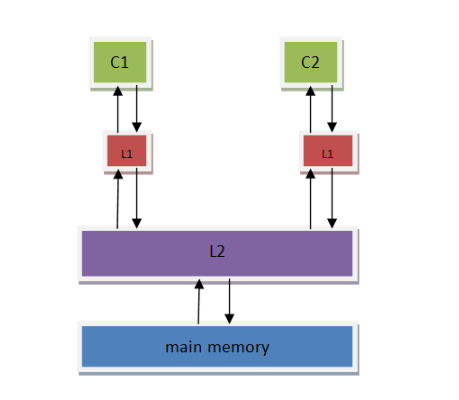

上图是现代CPU的基本内存模型,CPU内部有多级缓存来提高CPU的load/store访问速度(因为对于CPU而言,主存的访问速度太慢了,上百个时钟周期的内存访问延迟会极大的降低CPU的使用效率,所以CPU内部往往使用多级缓存来提升内存访问效率。)

C1与C2是CPU的2个核心,这两个核心有私有缓存L1,以及共享缓存L2。最后一级存储器才是主存。后面的顺序一致性模型(SC)中,我们会以这个为基础进行描述(在完全存储定序、部分存储定序和宽松内存模型里会有所区别,后面会描述相关的部分)

为了简化描述的复杂性,在下面的内存一致性模型描述里,会先将缓存一致性(cache coherence)简单化,认为缓存一致性是完美的(假设多核cache间的数据同步与单核cache一样,没有cache引起的数据一致性问题),以减少描述的复杂性。

顺序存储模型是最简单的存储模型,也称为强定序模型。CPU会按照代码来执行所有的load与store动作,即按照它们在程序的顺序流中出现的次序来执行。从主存储器和CPU的角度来看,load和store是顺序地对主存储器进行访问。

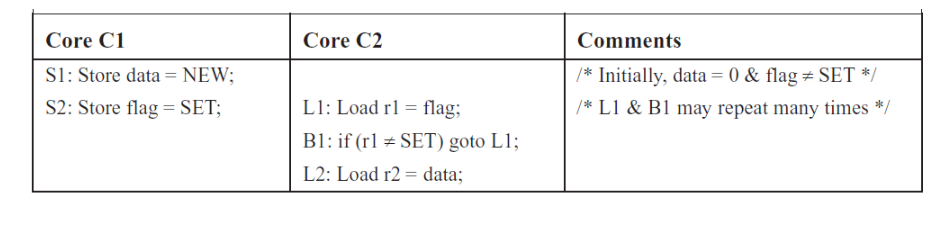

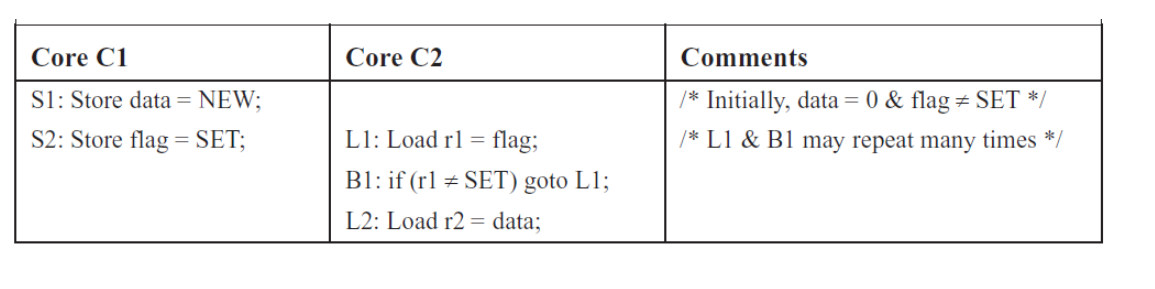

下面分析这段代码的执行结果

在顺序存储器模型里,MP(多核)会严格严格按照代码指令流来执行代码

所以上面代码在主存里的访问顺序是:

S1 S2 L1 L2

通过上面的访问顺序我们可以看出来,虽然C1与C2的指令虽然在不同的CORE上运行,但是C1发出来的访问指令是顺序的,同时C2的指令也是顺序的。虽然这两个线程跑在不同的CPU上,但是在顺序存储模型上,其访问行为与UP(单核)上是一致的。

我们最终看到r2的数据会是NEW,与期望的执行情况是一致的,所以在顺序存储模型上是不会出现内存访问乱序的情况

3完全存储定序

为了提高CPU的性能,芯片设计人员在CPU中包含了一个存储缓存区(store buffer),它的作用是为store指令提供缓冲,使得CPU不用等待存储器的响应。所以对于写而言,只要store buffer里还有空间,写就只需要1个时钟周期(哪怕是ARM-A76的L1 cache,访问一次也需要3个cycles,所以store buffer的存在可以很好的减少写开销),但这也引入了一个访问乱序的问题。

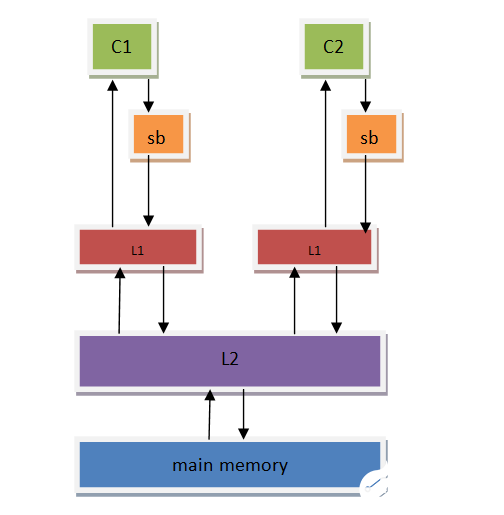

首先我们需要对上面的基础内存模型做一些修改,表示这种新的内存模型

相比于以前的内存模型而言,store的时候数据会先被放到store buffer里面,然后再被写到L1 cache里。

首先我们思考单核上的两条指令:

S1:store flag= set

S2:load r1=data

S3:store b=set

如果在顺序存储模型中,S1肯定会比S2先执行。但是如果在加入了store buffer之后,S1将指令放到了store buffer后会立刻返回,这个时候会立刻执行S2。S2是read指令,CPU必须等到数据读取到r1后才会继续执行。这样很可能S1的store flag=set指令还在store buffer上,而S2的load指令可能已经执行完(特别是data在cache上存在,而flag没在cache中的时候。这个时候CPU往往会先执行S2,这样可以减少等待时间)

这里就可以看出再加入了store buffer之后,内存一致性模型就发生了改变。

如果我们定义store buffer必须严格按照FIFO的次序将数据发送到主存(所谓的FIFO表示先进入store buffer的指令数据必须先于后面的指令数据写到存储器中),这样S3必须要在S1之后执行,CPU能够保证store指令的存储顺序,这种内存模型就叫做完全存储定序(TSO)。

我们继续看下面的一段代码

在SC模型里,C1与C2是严格按照顺序执行的

代码可能的执行顺序如下:

S1 S2 L1 L2

S1 L1 S2 L2

S1 L1 L2 S2

L1 L2 S1 S2

L1 S1 S2 L2

L1 S1 L2 S2

由于SC会严格按照顺序进行,最终我们看到的结果是至少有一个CORE的r1值为NEW,或者都为NEW。

在TSO模型里,由于store buffer的存在,L1和S1的store指令会被先放到store buffer里面,然后CPU会继续执行后面的load指令。Store buffer中的数据可能还没有来得及往存储器中写,这个时候我们可能看到C1和C2的r1都为0的情况。

所以,我们可以看到,在store buffer被引入之后,内存一致性模型已经发生了变化(从SC模型变为了TSO模型),会出现store-load乱序的情况,这就造成了代码执行逻辑与我们预先设想不相同的情况。而且随着内存一致性模型越宽松(通过允许更多形式的乱序读写访问),这种情况会越剧烈,会给多线程编程带来很大的挑战。

4部分存储定序

芯片设计人员并不满足TSO带来的性能提升,于是他们在TSO模型的基础上继续放宽内存访问限制,允许CPU以非FIFO来处理store buffer缓冲区中的指令。CPU只保证地址相关指令在store buffer中才会以FIFO的形式进行处理,而其他的则可以乱序处理,所以这被称为部分存储定序(PSO)。

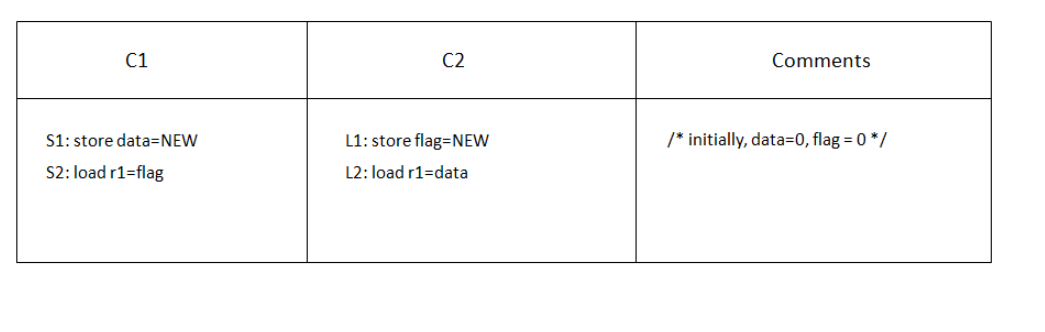

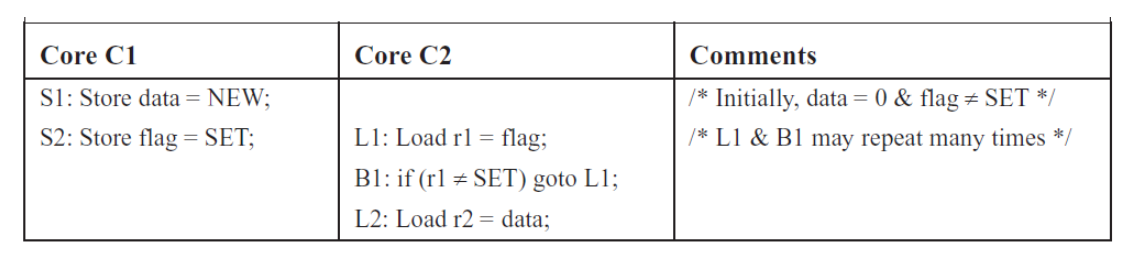

那我们继续分析下面的代码

S1与S2是地址无关的store指令,cpu执行的时候都会将其推到store buffer中。如果这个时候flag在C1的cahe中存在,那么CPU会优先将S2的store执行完,然后等data缓存到C1的cache之后,再执行store data=NEW指令。

这个时候可能的执行顺序:

S2 L1 L2 S1

这样在C1将data设置为NEW之前,C2已经执行完,r2最终的结果会为0,而不是我们期望的NEW,这样PSO带来的store-store乱序将会对我们的代码逻辑造成致命影响。

从这里可以看到,store-store乱序的时候就会将我们的多线程代码完全击溃。所以在PSO内存模型的架构上编程的时候,要特别注意这些问题。

5宽松内存模型

丧心病狂的芯片研发人员为了榨取更多的性能,在PSO的模型的基础上,更进一步的放宽了内存一致性模型,不仅允许store-load,store-store乱序。还进一步允许load-load,load-store乱序, 只要是地址无关的指令,在读写访问的时候都可以打乱所有load/store的顺序,这就是宽松内存模型(RMO)。

我们再看看上面分析过的代码

在PSO模型里,由于S2可能会比S1先执行,从而会导致C2的r2寄存器获取到的data值为0。在RMO模型里,不仅会出现PSO的store-store乱序,C2本身执行指令的时候,由于L1与L2是地址无关的,所以L2可能先比L1执行,这样即使C1没有出现store-store乱序,C2本身的load-load乱序也会导致我们看到的r2为0。从上面的分析可以看出,RMO内存模型里乱序出现的可能性会非常大,这是一种乱序随可见的内存一致性模型。

6内存屏障

芯片设计人员为了尽可能的榨取CPU的性能,引入了乱序的内存一致性模型,这些内存模型在多线程的情况下很可能引起软件逻辑问题。为了解决在有些一致性模型上可能出现的内存访问乱序问题,芯片设计人员提供给了内存屏障指令,用来解决这些问题。

内存屏障的最根本的作用就是提供一个机制,要求CPU在这个时候必须以顺序存储一致性模型的方式来处理load与store指令,这样才不会出现内存访问不一致的情况。

对于TSO和PSO模型,内存屏障只需要在store-load/store-store时需要(写内存屏障),最简单的一种方式就是内存屏障指令必须保证store buffer数据全部被清空的时候才继续往后面执行,这样就能保证其与SC模型的执行顺序一致。

而对于RMO,在PSO的基础上又引入了load-load与load-store乱序。RMO的读内存屏障就要保证前面的load指令必须先于后面的load/store指令先执行,不允许将其访问提前执行。

我们继续看下面的例子:

例如C1执行S1与S2的时候,我们在S1与S2之间加上写屏障指令,要求C1按照顺序存储模型来进行store的执行,而在C2端的L1与L2之间加入读内存屏障,要求C2也按照顺序存储模型来进行load操作,这样就能够实现内存数据的一致性,从而解决乱序的问题。

ARM的很多微架构就是使用RMO模型,所以我们可以看到ARM提供的dmb内存指令有多个选项:

LD load-load/load-store

ST store-store/store-load

SY any-any

这些选项就是用来应对不同情况下的乱序,让其回归到顺序一致性模型的执行顺序上去

-

存储器

+关注

关注

38文章

7576浏览量

165324 -

cpu

+关注

关注

68文章

10972浏览量

214386 -

内存

+关注

关注

8文章

3086浏览量

74705

发布评论请先 登录

相关推荐

请问如何保证多片AD1278的通道之间相位一致性?

FCB-EV9520L光轴一致性的典范,焦距变换精准如初

一致性测试系统的技术原理和也应用场景

LMK05318的ITU-T G.8262一致性测试结果

TPS23882B SIFOs IEEE802.3bt 一致性测试报告

电感值和直流电阻的一致性如何提高?

新品发布 | 同星智能正式推出CAN总线一致性测试系统

铜线键合焊接一致性:如何突破技术瓶颈?

请问ESP-NOW对数据的完整性和一致性有校验吗?

为什么主机厂愈来愈重视CAN一致性测试?

锂电池组装及维修的关键:电芯一致性的重要性

新品发布 | 同星智能重磅发布TH7011—CAN FD一致性干扰仪!

多种内存一致性模型的特性分析

多种内存一致性模型的特性分析

评论