正如他们所说,“除了时间表,一切都会改变。” 作为设计师,我们知道这一点,并且保持低调,并在截止日期之前完成最后的100次连接。我们很聪明,将违反设计规则的情况降至最低。我们与夜间备份共享我们的工作。那些不断共享的设计都装饰有一封电子邮件,其中总结了任务并指出了每天的任何风险。

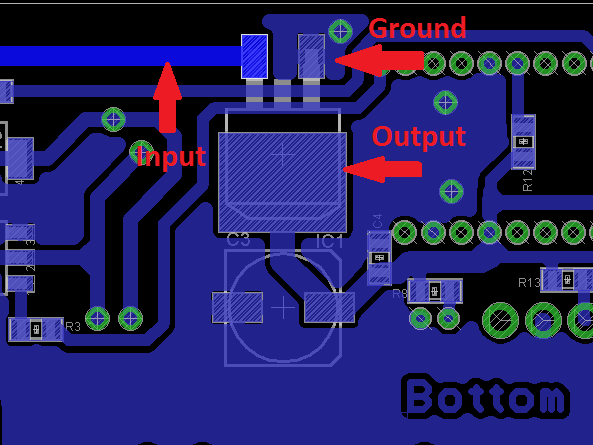

信号和电源完整性规则已被严格约束,从而使设计从始至终都符合要求。虚拟电路板的仿真和迭代使专家们满意,该电路板将完成其工作。通过对已知良好电路的设计重用,可以使学习曲线尽可能平坦。嘈杂的电源和那些emo接收链再也不能分开了。我们做了他们要求的一切,还有更多。

丝网印刷和装配图的所有参考标记均已组织好,以便进行位置审查。剩下的就是由于按摩布局以获得更好的路由而导致的偶然文本重叠。哦,当然,每个原理图修订版都包含一些新零件。毫无疑问,您又一次导入了网表,以确保没有人试图对您进行快速筛选。

初步文件已与Fab和组装单位共享,当然,供应商对如何使他们更容易获得了意见。就像一位优秀的设计师一样,您将所有这些信息都插入了数据库。叠层和受控阻抗线的几何形状已由制造商预先批准。在这一点上没有惊喜。

组装子面板具有拾放机的所有正确功能,可将组件对准覆盖区。除工具孔和基准点外,折断区域还带有金属小偷,可防止任何翘曲问题。面板说明了所有边缘连接器。面板上甚至还有一个箭头,向他们显示电路板将通过回流炉的方式。

已经考虑了纤维编织对传输线的影响。试图沿着这些带状线和微带线的迹线指出另一个位置的人显然并没有注意迹线上方或下方的层。天线区域周围的任何更多通孔都会使保持阻抗所需的电介质板耗尽。我们必须为电源平面和走线留点东西。

仅当组件根本不允许使用保护带时,关键线之间的隔离才会受到损害。即使这样,也可以平衡分担痛苦。内存总线已按规格进行了调整,外观小巧而通风,同时仍保持紧凑。高速配对绝对优雅!即使是未经训练的眼睛也可以通过过大的气隙发现时钟网。

考虑到导电阳极丝的生长,将高压部分隔开。从模具的结点一直到地球母亲的热路径都是坚如磐石。温升和压降将是可控的。围绕每一层周长的地面环可将您的噪音挡在外面,并将噪音挡在外面。完全没有静电;牢固的接地可使ESD事件远离板子的内部圣殿。

尺寸是完整的,与产品设计移交的所有内容都十分相似。保留区中没有任何部件,所有有限的净空区域都可以容纳。库符号已与数据表进行了仔细检查。毫无疑问,每个IC上的插针都是一脚,钽电容上的极性标记清楚无误,二极管的阴极插针清晰可见,从组装到丝网印刷的所有过程都在重复。

零件编号和修订级别与图纸匹配。设计说明是完整且连贯的。涵盖了环境和排放法规。该阻焊是正确的颜色。你做好了 当检查图出来进行“最终”审查时,所有的小细节都摆平了,所以,最终比赛应该是低压力的胜利圈,为什么从来没有这样呢?

在我们将所有点连接在一起之前,任何人都很难祝福这个位置。就个人而言,我知道我会在扇出和布线过程中四处移动东西,以便为通孔或其他布线元素让路。我们会尽力将组件放置在各自的位置,然后找出错误的地方。即使空间足够用于布线计划,这也仅意味着可以在此处和此处收紧该位置。

PCB设计是一个动态的过程。我们永远不会从完整的故事开始。克服不确定性是一个风险/回报过程。一旦所有细节都知道了,木板可能会有点钙化,但是比起所有空白画布要完成的工作要近得多。一个对工作感到自豪的设计师,但又足够实际,可以接受无法预料的情况,这将是远远的。

-

PCB设计

+关注

关注

394文章

4692浏览量

85882 -

PCB线路板

+关注

关注

10文章

434浏览量

19925 -

PCB打样

+关注

关注

17文章

2968浏览量

21745 -

华秋DFM

+关注

关注

20文章

3494浏览量

4597

发布评论请先 登录

相关推荐

HDMI模块的PCB设计

专业PCB设计,高速PCB设计,PCB设计外包, PCB Layout,PCB Design,PCB画板公司,PCB设计公司,迅安通科技公司介绍

pcb设计中如何设置坐标原点

PCB设计与PCB制板的紧密关系

PCB设计基本原则总结,工程师必看

PCB设计的EMC有哪些注意事项

PCB设计中的常见问题有哪些?

pcb设计

多层pcb设计如何过孔的原理

PCB设计表面到底应不应该敷铜?

PCB设计应该如何获得最后的成功

PCB设计应该如何获得最后的成功

评论