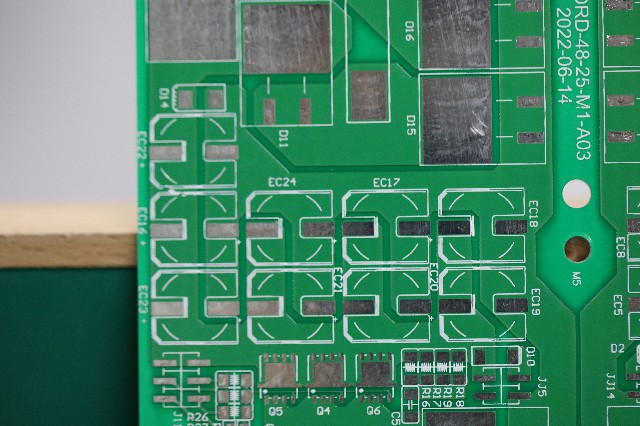

在PCB设计中,您希望时钟信号迅速到达其集成电路(IC)的目的地。但是,一种称为时钟偏斜的现象会导致时钟信号早晚到达某些IC。当然,这会导致各个IC的数据完整性不一致。

什么是时钟偏斜

时钟偏斜是一种现象,其中时钟信号以不同的间隔到达不同的目的地。时钟信号通常用于PCB设计中的同步通信。例如,串行外设接口(SPI)使用时钟信号在设备之间发送和接收数据。

在理想的主机到多个从机组件的配置中,时钟信号的传播时间没有延迟。时钟总线上连接的所有组件均应同时接收信号。

但是,在实际应用中,会发生传播延迟,并且时钟脉冲可能以各种间隔到达目标组件。时钟偏斜的根源在于寄生电容和时钟信号的不同走线长度。

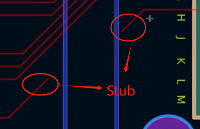

想象一下一个来自驱动器的时钟信号,它分成两个不同的路径。路径A是路径B长度的一半,并且它们都连接到不同的接收器。很自然,路径A上的时钟信号比路径B上的时钟信号更早到达目的地。

在电子产品中,时钟信号用作组件的时间参考,以将接收引脚上的数据位锁存。一些协议在向上的时钟脉冲上锁存数据,而其他协议在向下的时钟脉冲上锁存数据。无论采用哪种锁存机制,可靠的时钟参考都是重要的。

如果出现时钟偏斜,则时钟信号可能比预期的早或晚匹配。当时钟在数据信号更新之前更改时,接收组件会将旧数据锁存到其寄存器中。如果协议基于时钟稳态而不是跳变来锁存数据,则时钟偏斜可能会导致接收器用两个后续数据覆盖存储器。

通常,时钟偏斜对于低速设计不是问题,因为存在大量误差。但是,如果您要在数百MHz的范围内设计高速应用程序,则时钟偏斜将成为真正的问题。

闩锁错误可能会导致数据完整性严重受损,并且在实际应用中可能造成灾难性的后果。对于时钟偏斜引起的出牙问题,预防总是比治疗更好。

防止PCB设计出现时钟偏移的技巧

当您了解时钟偏斜的原因时,防止这种现象就变得容易了。防止时钟偏斜的关键在于确保时钟信号同时到达不同的接收器。

为此,您需要确保源组件和目标组件之间的走线长度应相等(长度匹配)。这意味着最短的走线长度可能不再是最佳路径。

在典型的同步设计中,您需要将一个驱动程序连接到多个接收器。可能是,某些接收器将更靠近驱动器,而另一些接收器将更靠近PCB。您需要先将时钟信号路由到最远的引脚,并确保其他时钟信号走线以相同的长度路由。

避免时钟信号分支以防止反射也很重要。这可以通过使用时钟驱动器来完成,而不是直接从源组件路由到接收器。此外,在时钟信号上使用阻抗匹配电阻也有助于确保时钟信号的完整性。

-

PCB设计

+关注

关注

394文章

4702浏览量

86555 -

PCB布线

+关注

关注

21文章

463浏览量

42159 -

PCB设计软件

+关注

关注

0文章

52浏览量

10264 -

华秋DFM

+关注

关注

20文章

3495浏览量

4799

发布评论请先 登录

相关推荐

深度解析:PCB高速信号传输中的阻抗匹配与信号完整性

PCB设计中的爬电距离:确保电路板安全可靠

pcb设计中布局的要点是什么

pcb设计中如何设置坐标原点

CDCM7005-SP高性能、低相位噪声和低偏斜时钟同步器数据表

PCB设计与PCB制板的紧密关系

Clock时钟电路PCB设计布局布线要求

储能PCB设计与制造思考 探讨储能PCB设计与制造中的关键要素

在PCB设计中如何避免时钟偏斜

在PCB设计中如何避免时钟偏斜

评论