目前,印刷电路板布局与以往一样具有挑战性。同时,现在比以往任何时候都容易。进步前进,很少回头。您的PCB布局是否超出了已知的范围?是否出现了一个全新的规范,数据速率突然从兆字节变为千兆字节?曾经经过严格审查的实践现在无法满足设计要求?这些问题使我们思考如何在满足围绕我们的设计严格的功率要求和排放标准的情况下,如何跟上不断增长的边沿速率。

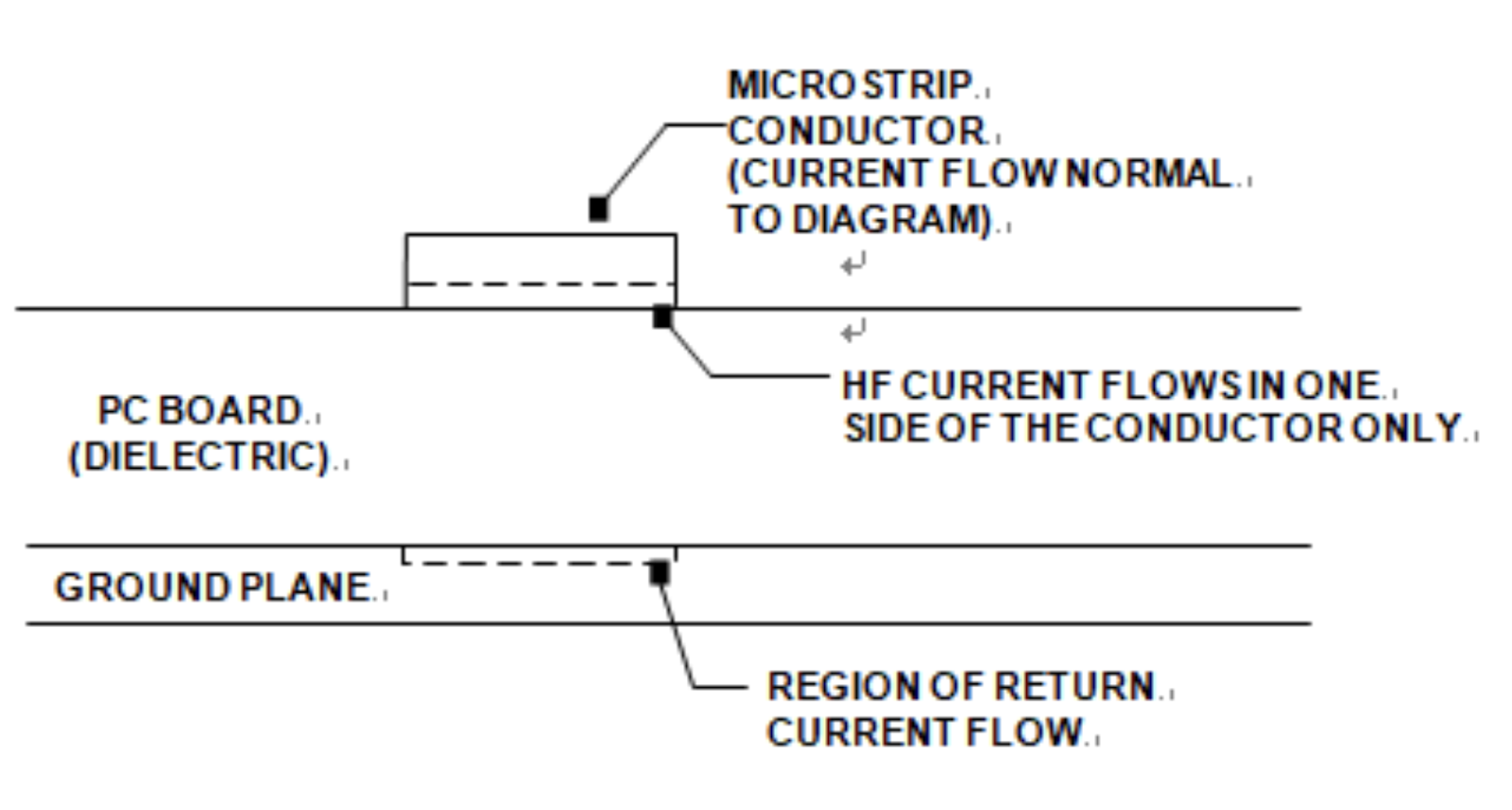

高速数字设计开始类似于RF工作,速度约为1 GB / s。每秒发生十亿次的任何事情最好对每条信息都有一个非常清晰的起点和终点。从横截面看,信号沿线的移动方式从使用整个轨迹变为主要沿着轨迹的外围流动。许多因素围绕着这种现象。这不是一件简单的事情。这种“皮肤效应”使我们想要更宽的痕迹,以在游戏中获得更多的皮肤。较宽的走线使我们重新计算介电层厚度,以保持正确的阻抗。

缩小尺寸

信号在精心设计的传输线上会以惊人的速度传播。即使这样,越短越好。与关键路径同情的精心布置将使布线更加容易,并节省了设计余量。与DDR一样,在更宽的总线上工作是为什么我使用“小心放置”而不是压缩放置的原因。过度拥挤的痕迹严重威胁信号的完整性。您自己的经验以及仅参与扇出研究将有助于找出每种独特情况的最佳层数和走线几何形状。留出一些额外的空间,以使较高速度的连接发挥作用。

一旦有人从布局中说明了他们想要的东西,便总是想像这样为他们总结一下。“那么,您希望所有零件都紧靠在一起,并且所有布线都分开吗?” 基本上就是这样。再次,巧妙的布局以及巧妙的扇出处理可以缓解密度热点,这可能需要花费一些迭代时间,才能达到最佳效果。切勿阻止改善电路流程。如果您有幸看到一些仿真以及布线的微小变化对仿真的影响,您将获得深刻的见解,可以推动下一个设计的发展。

为下一个电压摆幅做好准备

较低电压的设备通常具有较低的本底噪声。不要争权夺利。使用位于电源引脚附近的并联电容器的形式可以方便地使用它,并且重要的是,如果附近有电容,则电容帽的另一侧希望与设备上的接地引脚保持舒适。从电源引脚穿过电容帽到设备接地的整个路径都很重要,因为它形成了一个电感环路。该循环越小越好。可以将芯片引脚固定为特定的电源和接地引脚对。可能有很多这样的配对。

注意应用笔记将有助于解决功耗难题。当公司拥有内部芯片团队时,PCB布局的体系结构通常取决于您。进行映射会议是找出任何易受攻击或特别具有攻击性的引脚的最佳时间。如果您可以参加该审查并影响引脚位置,那么这是一个绝佳机会,可以帮助专注于团队的团队考虑系统架构。它不应该是一个外来的概念,但是对于某些人来说,这个词以晶圆为结尾。如果您所能获得的就是XO引脚移到外围,那就赢了。做好参考设计,您永远都不知道谁会使用它们。

防止差分对变得太大。

器件制造商和我们的电气工程师越来越喜欢松散耦合的差分对。与紧密耦合的差分对相比,长距离运行时互电容可能较小。我们的差分对之间的气隙通常比走线本身宽,走线是紧密耦合和松散耦合之间的临界点。

随着极端的上升和下降时间,我们必须更加意识到保持每一对中的两个成员彼此协调。正迹线和负迹线之间的额外气隙使占据曲线内部的迹线具有更大的长度优势。S曲线抵消了差异,但掉头加起来了。有时候,弯曲一对的最佳方法是经过目标引脚对然后再返回。尽可能避免诱惑。线对间的偏斜加起来可以达到毫米,这比应用笔记通常所允许的偏差大一个数量级。尽可能平衡左右弯曲,以免出现过多的相位调整凸块而超出未耦合长度限制的情况。这是一种平衡行为,偏差逐渐消失。

在这种情况下,您的专家(小g)思维技巧是考虑使用动态相位控制。这就意味着每次有实质性的转折时都要重新对齐两条轨迹。我们想要的是两个波形以同步的方式沿着整个路径的每个部分传播。采用较短路径的走线中的一个小凸起是该技术的关键。就像我们不能在同一条河上漂两次一样,一个区域中存在的条件瞬息万变。我们不仅要进行相位调整,以使两个信号同时到达接收器引脚对,而且还要使它们从一端同步到另一端。

当然,我们不希望高速走线上有任何过孔。就是说,如果一组中的一个获得一个或两个,则其他成员应该在相同的层上具有同感过孔和布线。外层相对于内层降低了信号的速度,并且它们提供了更少的EMI和物理保护用于传输线。通过使用相同的拓扑来保持传播速度相同是好的。几乎相同的迹线更好。在高速过渡附近有接地孔是好的。通过用三个或更多个接地过孔围绕信号过孔来在Z轴上创建同轴电缆是EMI抑制的下一个层次。腾出空间来花更多的时间和精力。尝试将质量改进到失败的设计中会花费更多的精力。投入具有额外呼吸空间的坚固设计可以带来更好的收益。给你一些!

-

PCB设计

+关注

关注

394文章

4696浏览量

86029 -

PCB布线

+关注

关注

20文章

463浏览量

42089 -

电路板打样

+关注

关注

3文章

375浏览量

4724 -

华秋DFM

+关注

关注

20文章

3494浏览量

4660

发布评论请先 登录

相关推荐

离AI更进一步|全新阵容!杰和科技AIOT解决方案

德州仪器推动自动驾驶发展更进一步

性能更进一步,一体机主板CB4-X12-V0大有可为

英特尔将进一步分离芯片制造和设计业务

RFTOP进一步扩充波导同轴转换器产品线

iPhone 15在美国市场需求进一步减弱

Melexis推出全新MLX81123芯片,进一步扩展LIN RGB系列产品线

西门子与微软进一步扩展战略合作关系

进一步解读英伟达 Blackwell 架构、NVlink及GB200 超级芯片

Arbe在中国上海设立分公司,进一步增强企业影响力

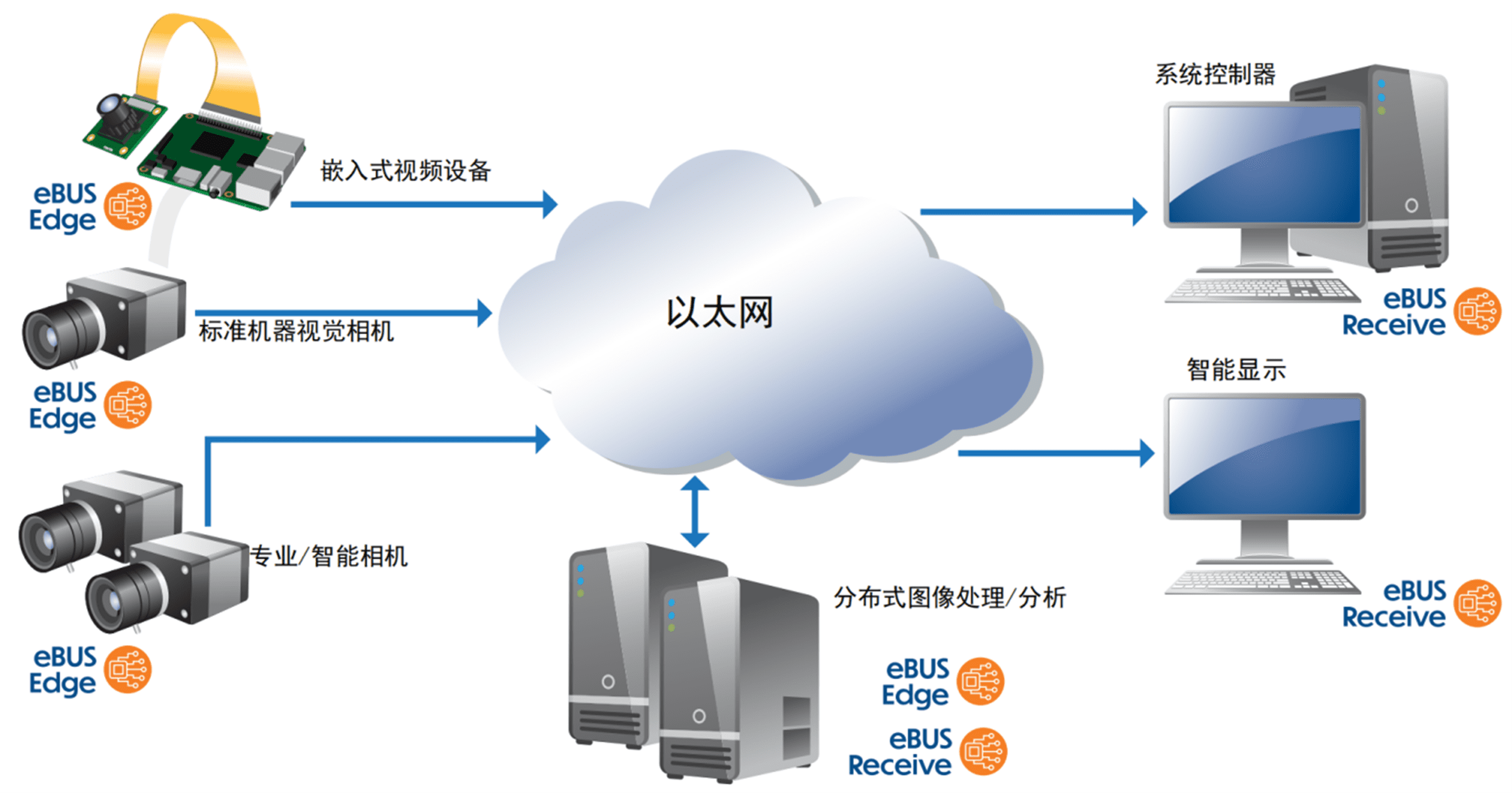

一键解锁:将任意图像设备秒变GigE Vision设备的终极秘诀

英飞凌重组销售与营销组织,进一步提升以客户为中心的服务及领先的应用支持能力

使高速PCB布局更进一步的方法

使高速PCB布局更进一步的方法

评论