消除过孔至过孔耦合噪声的技巧

众所周知,多层PCB设计可以减轻高速信号电路的EMI / EMC效应。导电通孔可在PCB的多个层之间提供连通性,为设计人员提供了分离AC和DC信号的空间,可优化组件的位置,并提供足够的接地层以降低噪声。

结果,多层PCB趋于更紧凑,从而使设计人员能够将更多功能集成到更小的外形尺寸中,而在当今世界中,对更小,更强大的电子产品的需求一直在增长,这是至关重要的元素。

但是,尽管与单层板相比,这些多层板具有这些优势,但多层板并非没有自己的EMI / EMC挑战。在设计多层PCB时,尤其是通孔到通孔的耦合仍然是一个具有挑战性的方面。在这篇文章中,我们将介绍一些消除通孔噪声的技巧。

什么是Via?

VIA是垂直互连访问的缩写。Via也是路径的拉丁语。结果,该首字母缩写词被通俗地视为单词“ via”,而不是首字母缩写词“ VIA”。

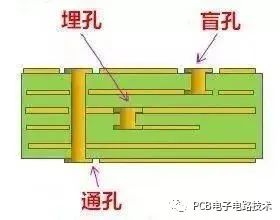

就像它的名字所暗示的那样,通孔在多层PCB的各层之间提供垂直连接。通孔的解剖结构包括:

l桶,是形成通孔主体的导电管。它在多层板上的平面之间镀覆穿过绝缘层钻出的孔。

l垫从桶的顶部径向向外延伸,以将过孔连接到该层上的组件,平面或走线。

l防焊盘是平面层和通孔之间的空隙,可防止平面短路到通孔。

通孔串扰是PCB设计中的主要问题

无论您的通孔是盲孔,埋孔还是通孔,水平应用于走线的对串扰和信号速度的担忧也适用于垂直过孔。只要您有电流并行流过两个或更多导电路径,就会发生耦合。

当耦合干扰严重到足以干扰信号质量时,就会发生串扰。串扰可以是电感性的也可以是电容性的,下面让我们仔细看看这两种干扰模式。

l感应串扰:在一个通孔中改变信号会产生磁场,该磁场会通过在导体上产生电动势来干扰“受害者”通孔的信号。

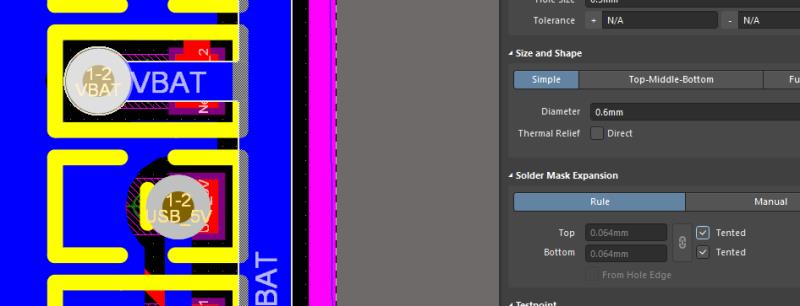

l电容性串扰:当两个导体之间相隔一个小间隙时,例如通孔的抗焊盘,您会得到一个可以静电存储能量的简单电容器。寄生电容会减慢信号,干扰时钟速度和时序。

在低速电路中,由于有足够的时间在反焊盘与平面结之间聚集电荷,因此寄生电容引起的串扰往往是一个更大的问题。在更高速度的电路中,电感是一个更大的问题,因为通孔中信号快速变化产生的磁场会在相邻的通孔上产生较强的电动势。

这里有一些提示

PCB设计中的耦合是生活的自然组成部分。诀窍是围绕这种现实进行设计以防止串扰。这里有一些常见的技巧和窍门,以减少过孔周围的噪声。

l差分配对过孔。将多层板中的层之间的通孔作为差分对进行布线(一个通孔载有信号,另一个通孔返回信号)。差分成对的通孔越近,噪声的降低就越好,但需要权衡较高的寄生互电容。在高速信号电路中,寄生电容并不是问题。

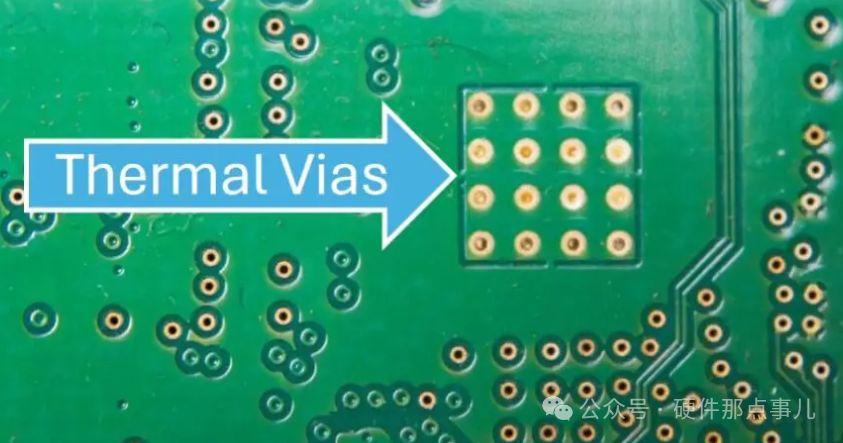

l通孔栅栏:通孔栅栏(又称通孔屏蔽)是一排通孔,它们沿RF信号的路径路径排列,以减少串扰和EMI的影响。

l通孔缝合:您可以在多层板上的两个平面之间建立牢固的垂直连接,方法是在板上的所有自由区域填充通孔。这减少了返回路径并导致低阻抗连接。

l去耦电容器:一种防止寄生电容的方法是为系统提供本地电容器,以通过为电路提供稳定的能量储备来防止电压尖峰。由于耦合可以是电容性或电感性的,因此去耦电容器在阻抗较高的电感元件较高的高信号电路中效率较低。

结论

仅关注板子水平面中的EMI和串扰已不再足够。随着对高速多层板的需求增加,也需要理解并遵循最佳实践来管理使这些多层配置成为可能的通孔。

围绕多层PCB的EMI和串扰管理的数学运算可能变得非常复杂。这就是为什么使用3D建模和PCB设计分析软件来确保最终准备好生产时考虑所有变量的重要性。

-

电路板设计

+关注

关注

1文章

127浏览量

16529 -

PCB设计

+关注

关注

394文章

4692浏览量

85895 -

PCB布线

+关注

关注

20文章

463浏览量

42083 -

华秋DFM

+关注

关注

20文章

3494浏览量

4598

发布评论请先 登录

相关推荐

PCB过孔的开窗,盖油,塞油到底是什么意思?厂家EQ该怎么回复?

PCB过孔设计的基础知识

PCB板生产时对过孔大小的要求

pcb设计中盲孔和过孔的区别?

PCB板上过孔太多如何解决

PCB阻抗匹配过孔的多个因素你知道哪些?

多层pcb设计如何过孔的原理

什么是PCB扇孔,PCB设计中对PCB扇孔有哪些要求

PCB线路板过孔盖油与过孔塞油的优劣比较

过孔能否打在焊盘上?

PCB中过孔是什么意思

PCB设计:消除过孔至过孔耦合噪声的技巧

PCB设计:消除过孔至过孔耦合噪声的技巧

评论