1 概述

TSA5059是专门为数字卫星接收机的调谐系统设计的单片PLL频率合成器,它的工作频率可达2.7GHz,供电电压为5V±10%,电源电流为45mA。输入信号幅度(RMS)在频率为64-150MHz、150MHz-2.2GHz、2.2-2.7GHz时分别为12.6-300mV、7.1-300mv和22.4-300mV。该器件的晶振频率为4-16MHz,工作温度范围为-20-+85℃,采用SO16及SSO16两种封装形式。其引脚排列如图1所示。各引脚的功能说明如下:

1脚(CP):电荷泵输出端,该脚可编程为四种电流值输出方式。

2脚(XTAL):参考晶振或其它振荡器输入。

3脚(XT/COMP):参考频率输出端,该脚在软件控制下,既可输出由晶体产生的振荡信号或其它振荡器信号,也可输出上述信号的4分频信号。

4脚(AS):I2c总线地址选择输入,高电平有效。

5脚(SDA)、6脚(SCL):分别为I2c总线的数据线和时钟线。

7-10脚(P3-P0):集电极开路式I/O口,在I2c总线控制下可读入外部数据或向外输出数据。

11脚(ADC):内部3位A/D转换器模拟信号输入端,该转换器与其它部分相对独立,通过I2c总线可读取转换结果。

12脚(Vcc):电源端。

13脚(RFA)、14脚(RFB):通常与压控振荡器(VCO)的输出端相连。

15脚(GND):接地端。

16脚(VT):调谐电压输出端,一般作为压控振荡器的控制电压。

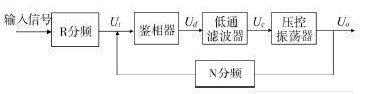

2 工作原理

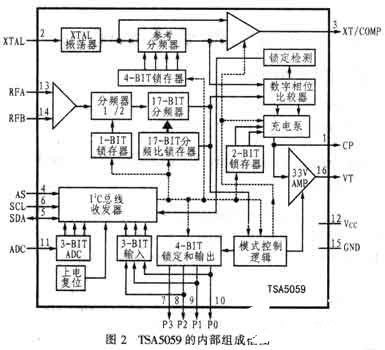

图2所示是TSA5059的内部组成框图。图中,来自于2脚的晶振或其它振荡器信号经TSA5059内部振荡器后产生相应的频率信号,该频率信号再经参考分频器分频即可产生参考频率FR。13脚、14脚的输入信号一般为压控振荡器(VCO)的输出信号,该信号在TSA5059内部经放大器进行呻鬲度放大后再经预定标器(由软件可控为分频值为1或2的分频器)和17位分频器后可产生比较信号频率Fc,把这两个信号送人数字相位比较器进行相位此较以产生相位差信号,然后将该相位差信号再经电荷泵电路处理来产生相对应的电流,该电流一路由1脚输出,另一路经33V放大器(33V AMP)后由16脚输出以控制压控振荡器的输出频率F。,从而使Fc值锁定在FR值上。这样,由于这两者仅有相位之差而无频率值之差,而且F。与Fc之间有固定的分频值,故F。是稳定的,这就是TSA5059锁相环的基本工作原理。

3 对TSA5059的控制:

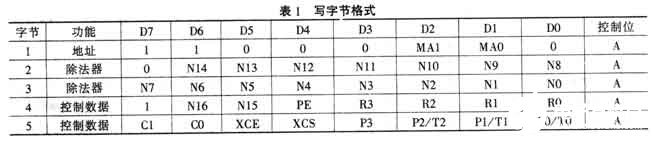

对TSA5059的控制可通过I2c总线来实现。在向TSA5059写入控制数据时,可按表1所列顺序进行。其中第一个字节为地址字节,且在写入时,D7位必须为0。表1中主要字节的每位含义如下:

MAl、MA0:可编程地址位,如果一块电路板上有多个TSA5059(最多四个)由一个控制器控制,为了分别控制每一个TSA5059,其MAI、MA0应按表2所列编码并向4脚提供电压。

A:回答位。

N16-NO:17位分频器分频比N控制位,即:

N=N16 X 216+N15 X 215+.。.+ N1 X 21+NO

PE:预定标器控制位,PE=1时,预定标器分频比为2,反之为1。

R3-BO:参考分频器分频比控制位,见表3所列。

C1、CO:电荷泵电流选择位,当ClC0为00时,其电荷泵电流IcP典型值为135μA,为01时,IcP为280μA,为10时,IcP为600μA,为11时,IcP为1230μA。

XCE:XT/COMP输出允许位,该位为1时,输出被激活。

XCS:XT/COMP选择位,该位为1时,为信号输出模式,为0时为测试模式。

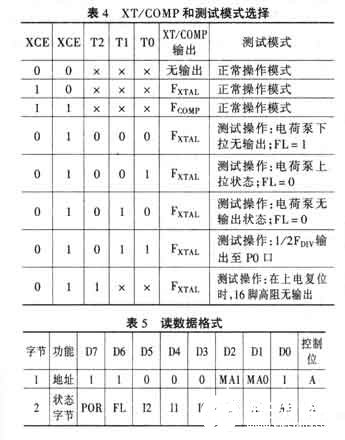

T2-T0:XCE=0且XCS=1时的测试模式。

P3-P1:P3-P1口输出状态。

P0:P0口输出状态,但测试模式除外。表4给出了TSA5059中XT/COMP和测试模式的具体选择说明。实际上,也可以在第一个字节后按以下几种顺序进行写操作:

(1)字节4、5、2和3;

(2)字节2、3、4和停止信号;

(3)字节4、5、2和停止信号;

(4)字节2、3和停止信号;

(5)字节2和停止信号;

(6)字节4和停止信号。

对TSA5059进行读操作可按表5的顺序进行。在读操作时,地址字节的D7位必须为1。当TSA5059的地址被确认后,TSA5059将产生应答脉冲以使第一个数据字节(状态字节)被传送在SDA线上,当第一个数据字节被读出后,假若控制器在SDA线上产生了一个应答脉冲,第二个数据字节即可被读出。而如果控制器在SDA线上产生了一个非应答脉冲,那么,数据传送将结束,此时TSA5059将释放SDA 线并使控制器产生停止状态。当把P0至P2口当作输入口时,它们必须被编程为高阻状态。

表5中各状态字节的每位含义如下:

当上电或Vcc低于2.75V时,POR标志位为1;在对TSA5059进行读操作时,如果TSA5059检测到读时序结束,那么,POR标志位为0。当环路相位被锁定时,FL=1。12、11、10位分别代表I/O口的状态。

A2、A1、A0的编码值代表了11脚的5个不同电压等级,当A2AlA0为100时, 11脚电压值为0.6Vcc-Vcc,011时为0.45Vcc-0.6Vcc,010时为0.3Vcc-0.45Vcc,001时为0.15Vcc-0.3Vcc,000时为0.-0.15Vcc。若把AFC电压接至11脚,即可通过I2c总线读出其数值的大小范围,其读出精度为±0.03 Vcc。

参考频率FR的获取是通过向表1中的第4个字节中的R3-R0写入不同的编码值来实现的,在4MHz晶振时,R3-R0在不同值时的FR值可参见表3。应当说明的是:TSA5059的3脚既可输出2脚所接的晶振频率,也可输出经参考分频器分频后的FR。

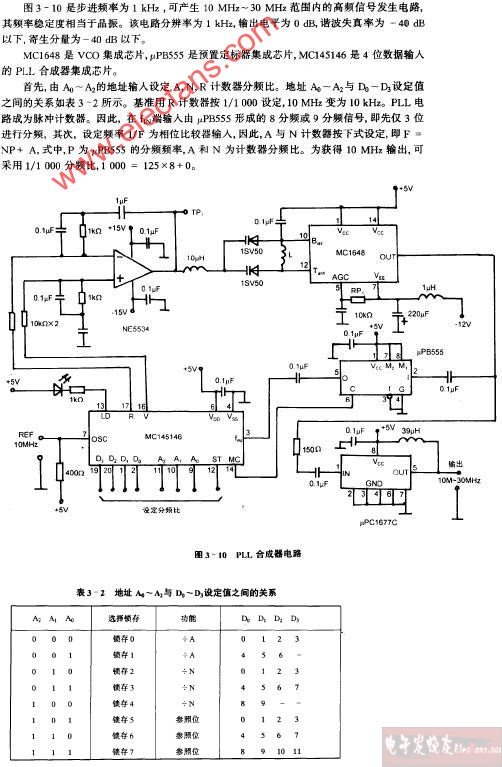

4 典型应用

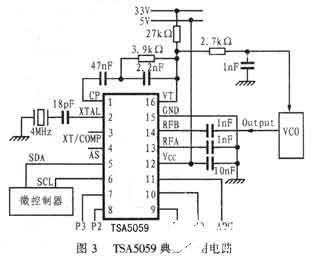

TSA5059的典型应用电路如图3所示,其中33V电压作为33V放大器的电源。1脚与16脚之间所接的元件组成环路滤波器,具体元件数值应视VCO的中心频率而定。16脚的输出电压经RC低通滤波器滤波后可用于控制压控振荡器(VCO),而VCO的输出电压则送至14脚并经分频后与参考频率相比较以产生相位差信号,该相位差信号再经33V放大器放大以控制振荡频率。本电路采用的是负反馈,其最终VCO的输出频率将被锁定在预定的数值上。

另外,利用TSA5059及SLl925(卫星零IF QPSK调谐电路)、STV0299(内含QPSK、BPSK解调电路及误码校正电路)还可组成高性能数字卫星接收机的下变频器。

责任编辑:gt

-

接收机

+关注

关注

8文章

1180浏览量

53460 -

卫星

+关注

关注

18文章

1713浏览量

67009 -

pll

+关注

关注

6文章

776浏览量

135141

发布评论请先 登录

相关推荐

详解频率合成器高性能架构的实现

如何利用FPGA设计PLL频率合成器?

DDS PLL短波频率合成器设计

基于FPGA与PLL频率合成技术设计的整数/半整数频率合成器

单片PLL频率合成器TSA5059的特点性能及典型应用电路

单片PLL频率合成器TSA5059的特点性能及典型应用电路

评论