随着速度成为影响产品性能的关键因素,人们通常知道设计具有许多高速接口。因此,不难发现经常出现信号以及电源完整性问题,进而导致设备故障。实际上,考虑到高速PCB设计的模拟特性,对于设计工程师来说变得越来越重要。

为了达到通常所说的SI的信号完整性,需要明确定义PCB路径。这些明确定义的路径又使信号可以在正确的时间从驱动器传递到接收器。另一方面,如果设计的SI较差,则不太可能在正确的时间传递信号。还已知不良的SI会导致辐射发射高于可接受的水平。设计中的问题还可能导致设备故障,使其根本无法运行。

有助于实现高速SI的设计元素:

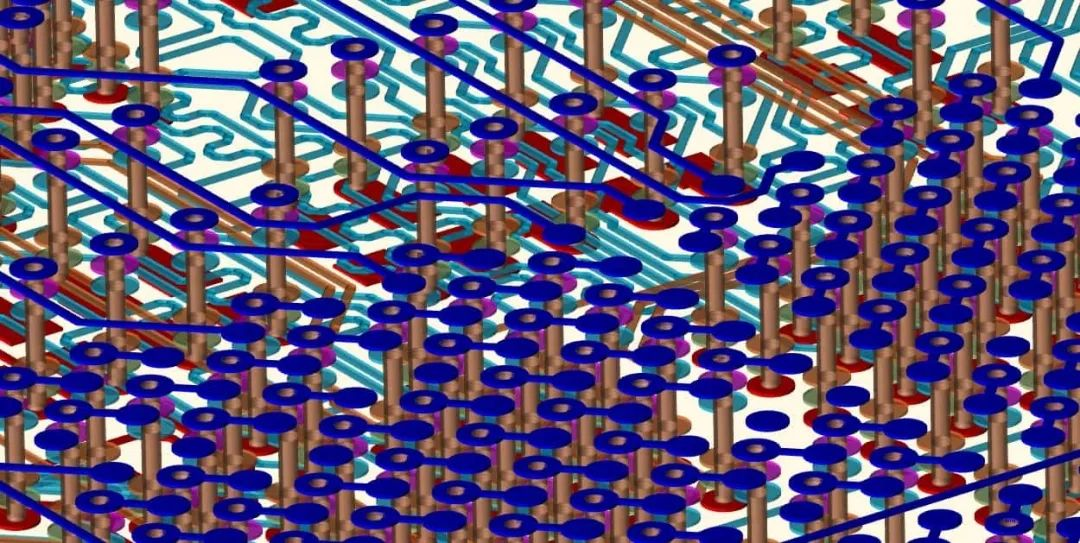

高速频率下的传输线行为-随着时钟速率和信号速度的提高,PCB走线的长度与通过它们的边沿速率的长度顺序相同。因此,延迟和损失需要仔细权衡。最常见的传输线阻抗为50Ω。为了获得所需的PCB材料阻抗,需要确定其每一层的走线宽度。两条常用的传输线包括带状线和微带线。带状线的信号走线位于两个参考平面之间,而在微带的情况下,信号走线在外层布线。信号速度要求以及设计复杂性决定了是否需要使用带状线或微带线。总的来说,微带已知提供更快的信号路径。

在考虑信号走线时,选择具有不变基准面的短走线也很重要。这样做的好处是电流可以流向接收器并通过最小阻抗的路径返回。常见的返回路径问题包括:

l参考平面中的不连续性

l下方无参考平面的路由信号层的变化

继而,以上导致信号反射和振铃。信号反射可能是驱动器,传输线或接收器阻抗的函数。如果信号遇到PCB阻抗的变化(称为阻抗不连续性),则信号可能会反射回其信号源,这会导致信号失真。在多次反射的情况下,会导致振铃。另一方面,如果驱动器,传输线和接收器具有相同的阻抗,则不会发生反射和振铃的问题。

出现的另一个问题是串扰。这是信号耦合的结果,如果多个信号的布线距离太近,则可能发生耦合。如果走线和返回路径的走线宽度是其他信号的两倍,则可以防止串扰。振铃也会增加串扰。

需要牢记的其他一些因素包括:

l端接拓扑

l迹线长度

l讯号速度

l痕迹形状等

因此,为了保持SI,需要牢记以下几点:

l识别高速信号。

l确保最高速度的信号位于顶层和底层。

l信号走线应与返回路径保持一个电介质。

l确保提供良好的地面参考

l线对间距保持大于2倍的线宽规则。

l确保与其他接口的线宽间距大于3倍。

l需要避免直角转弯

l通孔数量需要最小化

l高速信号需要远离噪声信号。

电源完整性

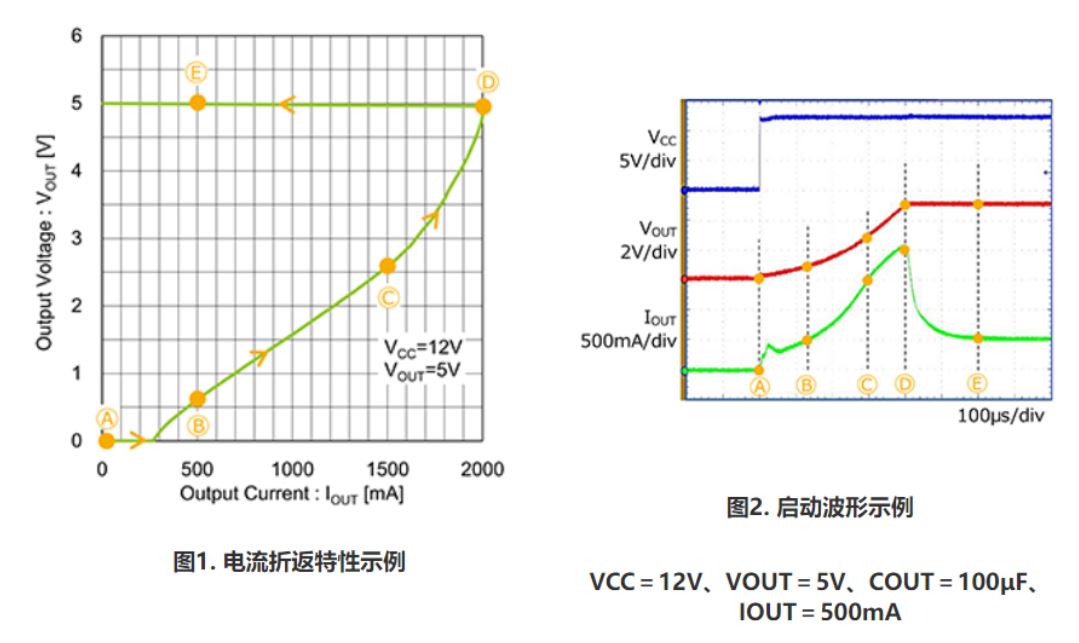

系统内部提供的符合电源条件的供电网络或PDN会导致电源完整性。与SI相比,电源完整性更难以可视化,因为有许多节点,每个节点都会影响整体阻抗。因此,与PI有关的问题很难解决。因此,在布局前后的PCB设计阶段都必须对Pi进行透彻研究。今天的PI研究涉及高频载荷的研究。

PI分析的关键是将电源轨视为传输平面并分析其特征阻抗。另一个问题是,在不同的频率下存在不同的阻抗,因此需要仔细研究组件以及放置位置。

-

PCB线路板

+关注

关注

10文章

433浏览量

19843 -

PCB打样

+关注

关注

17文章

2968浏览量

21637 -

电路板打样

+关注

关注

3文章

375浏览量

4674 -

华秋DFM

+关注

关注

20文章

3492浏览量

4364

发布评论请先 登录

相关推荐

pcb板故障分析与处理方法

高速PCB设计指南

如何防止使用高速PCB导致设备故障的

如何防止使用高速PCB导致设备故障的

评论