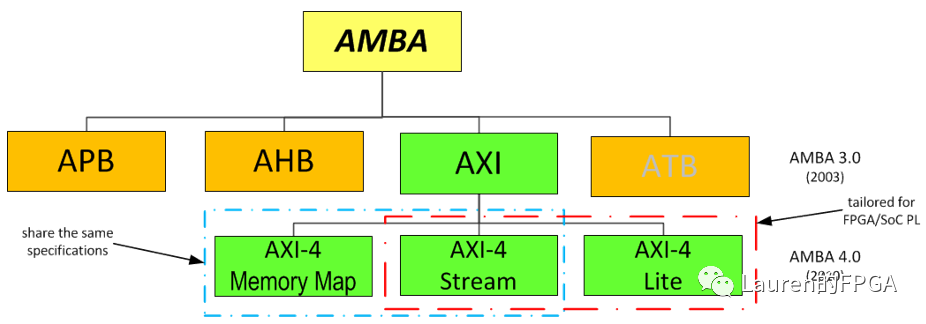

AXI全称Advanced eXtensibleInterface,是Xilinx从6系列的FPGA开始引入的一种接口协议,主要描述了主设备和从设备之间的数据传输方式。该协议是AMBA3.0(Advanced Microcontroller Bus Architecture)中最重要的部分,是一种面向高性能、高带宽、低延迟的片内接口协议。AMBA4.0将其修改升级为AXI4.0,如下图所示。

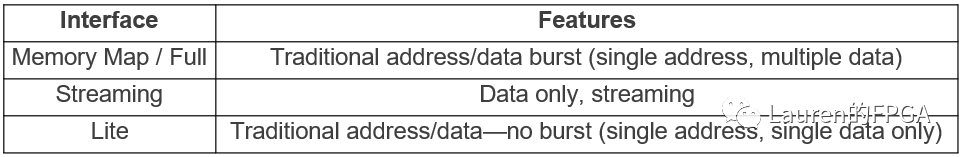

AXI4.0提供三种类型的接口形式,分别是AXI-4 Memory Map(也称之为AXI-4 Full)、AXI-4 Stream和AXI-4 Lite,三者的特性如下图所示。

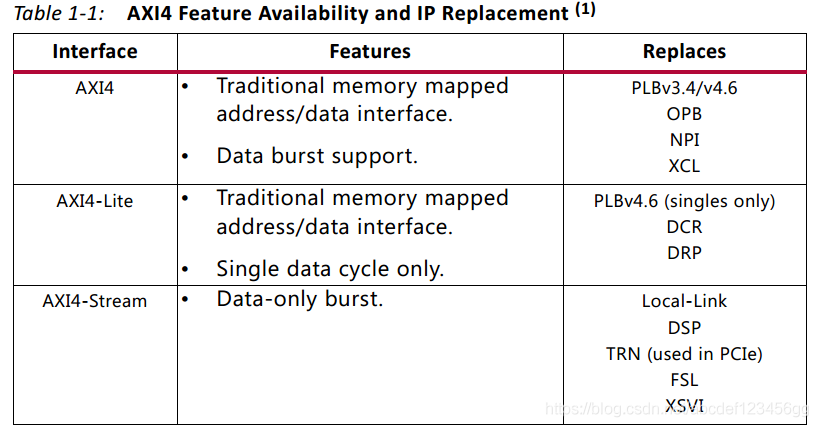

AXI-4 Full协议相当于原来的AHB协议,提供高速的系统内部互连通道,可以支持burst模式,主要用于处理器访问存储单元等需要高速数据传输的场合;AXI4-Lite相当于原来的APB协议,主要用于访问一些低速外设;AXI4-Stream接口就像FIFO一样,数据传输的时候不需要地址,而是主从设备直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA接口等需要高速数据传输的场合,跟Xilinx原来的Local Link协议类似。

总体而言,AXI接口协议具有如下特征:

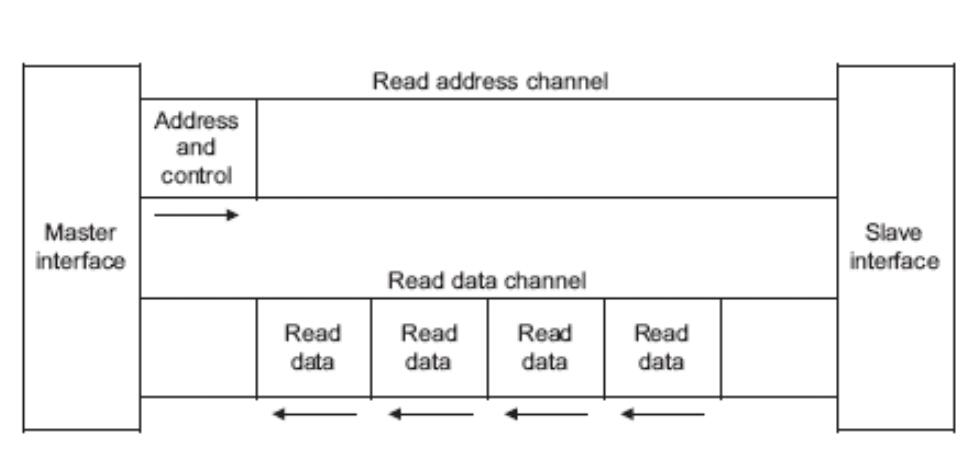

分离的地址/控制、数据相位

使用字节选通,支持非对齐的数据传输

基于burst传输,只需传输首地址

读、写数据通道分离,能提供低功耗DMA

支持多种寻址方式

支持乱序传输

易于添加寄存器级来进行时序收敛

AXI并非总线(Bus),总线是如下图所示的数据传输和互联方式,而AXI是点对点(Point-to-point)的主从接口协议。当多个外设需要互相交互数据时,我们需要加入一个所谓的AXI Interconnect模块(Xilinx提供了这个IP),也就是AXI互联矩阵,作用是提供将一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制(有点类似于交换机里面的交换矩阵)。

-

接口协议

+关注

关注

5文章

41浏览量

18672 -

AXI

+关注

关注

1文章

131浏览量

16898

原文标题:AXI是Interface还是Bus?

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

XILINX FPGA IP之AXI Traffic Generator

AXI接口协议的类型和特征

AXI接口协议的类型和特征

评论