同步时钟是指发送时钟和接收时钟是由同一个MMCM或PLL生成,两者之间有明确的相位关系。例如:两者可以是同频但有固定相差;或者同相但不同频。这里我们重点介绍一下同相不同频的跨时钟域路径,分两种情形:从慢时钟到快时钟和从快时钟到慢时钟。

从慢时钟到快时钟

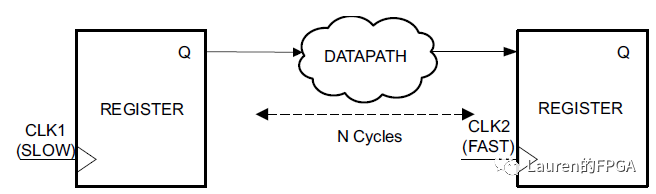

如下图所示,这里假定CLK2的频率是CLK1的3倍。这实际是条多周期路径。

发送时钟和接收时钟之间的关系如下图所示。

在只有时钟周期约束而没有多周期路径约束的情况下,STA(Static Timing Analysis)工具会认为建立时间检查和保持时间检查如下图所示。不难看出,保持时间检查是合理的,但建立时间检查不是期望的。换言之,建立时间如果按此分析就会过紧。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

同步时钟

+关注

关注

0文章

55浏览量

3321

原文标题:同步跨时钟域路径如何约束

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

跨时钟域的时钟约束介绍

解释了什么时候要用到FALSE PATH: 1.从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑。 2. 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟

发表于 07-03 11:59

关于FPGA中跨时钟域的问题分析

跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟

发表于 08-19 14:52

•3448次阅读

同相不同频的跨时钟域路径介绍

同相不同频的跨时钟域路径介绍

评论